| 5V ASYNCHRONOUS SRAMs   |   |

|-------------------------|---|

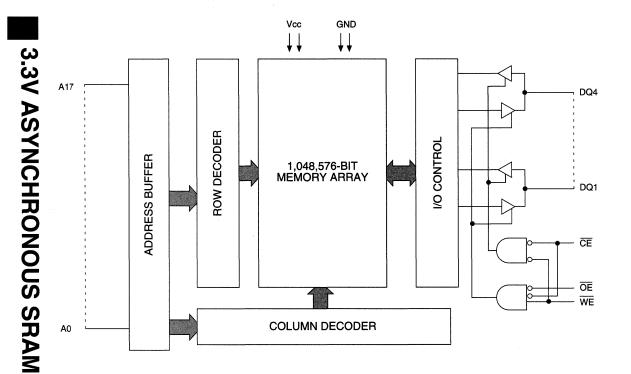

| 3.3V ASYNCHRONOUS SRAMs | 2 |

| SYNCHRONOUS SRAMs       | 3 |

| SRAM MODULES            | 4 |

| TECHNICAL NOTES         | 5 |

| PRODUCT RELIABILITY     | 6 |

| PACKAGE INFORMATION     | 7 |

| SALES INFORMATION       | 8 |

# **SRAM DATA BOOK**

2805 East Columbia Road Boise, Idaho 83706 Telephone: 208-368-3900 Fax: 208-368-4431 Micron DataFax<sup>™</sup>: 208-368-5800 Customer Comment Line: U.S.A. 800-932-4992 Intl. 01-208-368-3410 Fax 208-368-3342

©1994, Micron Semiconductor, Inc. Printed in the U.S.A.

Micron Semiconductor, Inc., reserves the right to change products or specifications without notice. Micron DataFax is a service mark of Micron Semiconductor, Inc.

-RON

Front — A variety of features highlight Micron's SRAM product line. Shown at left, a circuitry backdrop rendered from a scanning electron microscope. Bottom right, the intricate memory of a 256K SRAM wafer, etched in silicon, which reflects the many hues of the natural color spectrum.

Back — Micron's Boise, Idaho, headquarters.

## **IMPORTANT NOTICE**

Micron Semiconductor, Inc. (Micron), reserves the right to change products or specifications without notice. Customers are advised to obtain the latest versions of product specifications, which should be considered in evaluating a product's appropriateness for a particular use. There is no assurance that Micron's semiconductor products are appropriate for any application by a customer.

MICRON MAKES NO WARRANTIES, EX-PRESSED OR IMPLIED, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANT-ABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OTHER THAN COMPLIANCE WITH MICRON'S SPECIFICATION SHEET FOR THE PRODUCT AT THE TIME OF DE-LIVERY. IN NO EVENT SHALL MICRON BE LIABLE FOR ANY INDIRECT, SPECIAL, IN-CIDENTAL OR CONSEQUENTIAL DAM-AGES AS A RESULT OF THE PERFOR-MANCE, ORFAILURE TOPERFORM, OF ANY MICRON PRODUCT.

ANY CLAIM AGAINST MICRON MUST BE MADE WITHIN 90 DAYS FROM THE DATE OF SHIPMENT BY MICRON AND MICRON HAS NO LIABILITY THEREAFTER. Micron's liability is limited to replacement of defective product or either Customer or Micron may elect refund of amounts paid in lieu of replacement. The warranty covers only defects arising under normal use and not malfunctions resulting from misuse, abuse, modification, or repairs by anyone other than Micron.

MICRON'S PRODUCTS ARE NOT AUTHO-RIZED FOR USE AS CRITICAL COMPO-NENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRIT-TEN APPROVAL OF THE PRESIDENT OF MICRON. Life support devices or systems are those which are intended to support or sustain life and whose failure to perform can be reasonably expected to result in a significant injury or death to the user. Critical components are those whose failure to perform can be reasonably expected to cause failure of a life support device or system or affect its safety or effectiveness.

MICRON DOES NOT WARRANT PRODUCT TO BE FREE OF CLAIMS OF PATENT IN-FRINGEMENT BY ANY THIRD PARTY AND DISCLAIMS ANY SUCH WARRANTY OR INDEMNIFICATION AGAINST PATENT IN-FRINGEMENT.

## Dear Customer:

Micron Semiconductor, Inc., is dedicated to the design, manufacture and marketing of high-quality, highly reliable memory components. Our corporate mission is:

## "To be a world-class team developing advantages for our customers."

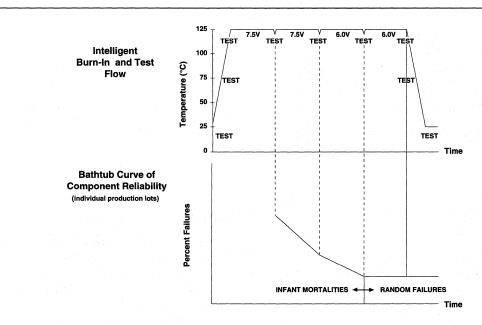

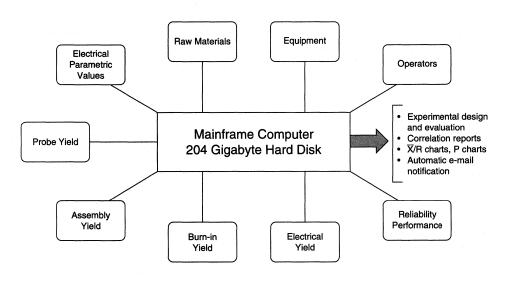

At Micron, we are investing time, talent and resources to bring you the finest DRAMs, SRAMs and other specialty memory products. We have developed a unique intelligent burn-in system, AMBYX<sup>®</sup>, which evaluates and reports the quality level of each and every component we produce.

We are dedicated to continuous improvement of all our products and services. This means continual reduction of electrical and mechanical defect levels. It also means the addition of new services such as "just-in-time" delivery and electronic data interchange programs. And when you have a design or application question, you can get the answers you need from one of Micron's applications engineers.

We're proud of our products, our progress and our performance. And we're pleased that you're choosing Micron as your memory supplier.

## The Micron Team

#### ADVANTAGES

Micron Semiconductor brings quality, productivity and innovation together to provide advantages for our customers. Our products feature some of the industry's fastest speeds. And we establish delivery standards based on customer expectations, including JIT programs, made possible by ever-increasing product reliability.

#### COMPONENT INTEGRATED CIRCUITS

Micron entered the memory market in 1978, first designing, then manufacturing dynamic random access memory (DRAM). From there, we developed high-performance fast static RAM (SRAM), multiport DRAM (including triple-port DRAM), and a variety of other memory products.

As we bring innovative memory solutions to our customers, we enjoy recognition for our achievements. Micron's Triple-Port DRAM was the first IC ever to incorporate a second, independent serial access port, allowing unparalleled flexibility in data manipulation. Micron's Triple-Port received the 1990 "Product of the Year" award from *Electronic Products* magazine.

#### SPECIALTY MEMORY PRODUCTS

Beyond our standard component memory, Micron is introducing many revolutionary products that we expect will follow the Triple-Port tradition. Micron continues to forge ahead into new and exciting frontiers.

We are pleased to be first to market with our compact, easy-to-install 88-pin DRAM card. Ideal for laptop, notebook and other portable systems, Micron's DRAM Card offers both high density and low power within JEDEC and JEIDA specifications.\*

#### **DIE SALES**

In addition to our durable packaging, Micron also provides memory devices in bare die form. These are increasingly in demand for use in highly specialized applications. Micron's bare die products are available both in 6" wafers and wafflepacks.

#### CUSTOM MANUFACTURING SERVICES

For total project management, Micron offers valueadded services. These include both standard contract manufacturing services for system-level products including design, assembly, customer kitted assembly, comprehensive quality testing or shipping as well as complete turnkey services covering all phases of production. Our component and system-level manufacturing facilities are centrally located in Boise, Idaho, so the component products you need are readily available.

#### MICRON DATAFAX

When you can't afford to wait for critical product information or specifications, Micron offers a convenient solution available 24 hours a day, every day. Micron DataFax enables you to make automated requests for data sheets, product literature, and other information from your fax machine. Just dial 208-368-5800 from your fax machine and Micron DataFax will give you instructions on how to order documents, including an index of documents. Once your order is placed, Micron DataFax will process your order, faxing up to two documents per call to your fax machine.

#### QUALITY

Without a doubt, quality is the most important thing we provide to every Micron customer with each Micron shipment. That's because we believe that quality must be internalized consistently at each level of our company. We provide every Micron team member with the training and motivation needed to make Micron's quality philosophy a reality.

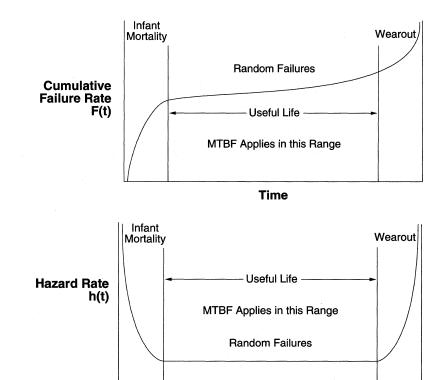

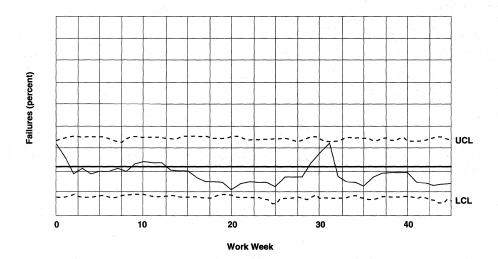

One way we have measurably improved both productivity and product quality is through our own quality improvement program formed by individuals throughout the company. Micron quality teams get together to address a wide range of issues within their areas. We consistently and regularly perform a company-wide selfassessment based on the Malcolm Baldrige National Quality Award criteria. We've also implemented statistical process controls to evaluate every facet of the memory design, fabrication, assembly and shipping process. And our AMBYX intelligent burn-in and test system\*\* gives Micron a unique edge in product reliability.

These quality programs recently resulted in Micron becoming one of the first U.S. semiconductor manufacturers to receive ISO 9001 certification. ISO 9001 is the most comprehensive level of certification in the internationally recognized ISO family of specifications. The certification implies that Micron's systems for accepting orders, reviewing customers' specifications, manufacturing and testing products, and delivering those products to its customers are quality controlled and produce consistent results.

\*See NOTE, page v.

\*\*For more information on AMBYX, see Section 6.

#### **ABOUT THIS BOOK**

#### CONTENT

The 1995 SRAM Data Book from Micron Semiconductor provides complete specifications on Micron's standard SRAMs, Synchronous SRAMs and SRAM Modules.

The SRAM Data Book is one of three product data books Micron currently publishes. Its two companion volumes include our DRAM Data Book and Flash Data Book. As product lines continue to diversify, more data books will be released.

#### SECTION ORGANIZATION

Micron's 1995 SRAM Data Book contains a detailed Table of Contents with sequential and numerical indexes of products as well as a complete product selection guide. The Data Book is organized into nine sections:

- Sections 1–4: Individual product families. Each contains a product selection guide followed by data sheets.

- Section 5: Technical/application notes.

- Section 6: Summary of Micron's unique quality and reliability programs and testing operation, including our AMBYX intelligent burn-in and test system.\*

- Section 7: Packaging information.

- Section 8: Sales information, including a list of sales representatives and distributors worldwide.

#### DATA SHEET SEQUENCE

Data sheets in this book are ordered first by width and second by depth. For example, the SRAM section begins with the  $256K \times 1$  followed by 1 Meg x 1, the  $64K \times 4$  and all other x4 configurations in order of ascending depth. Next come the x8 products, etc., as applicable to the specific product family.

#### DATA SHEET DESIGNATIONS

As detailed in the table below, each Micron product data sheet is classified as either Advance, Preliminary or Final. In addition, new product data sheets that are new additions are designated with a "New" indicator in the tab area of each page.

#### SURVEY

We have included a removable, postage-paid survey form in the front of this book. Your time in completing and returning this survey will enhance our efforts to continually improve our product literature.

For more information on Micron product literature, or to order additional copies of this publication, contact:

Micron Semiconductor, Inc. 2805 East Columbia Road Boise, ID 83706 Phone: 208-368-3900 Fax: 208-368-4431 Micron DataFax: 208-368-5800 Customer Comment Line: U.S.A. 800-932-4992 Intl. 01-208-368-3410 Fax 208-368-3342

| DATA SHEET MARKING | DEFINITION                                                                                                                                                                                                                                                                                  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance            | This data sheet contains initial descriptions of products still under development.                                                                                                                                                                                                          |

| Preliminary        | This data sheet contains initial characterization limits that are subject to change upon full characterization of production devices.                                                                                                                                                       |

| No Marking         | This data sheet contains minimum and maximum limits specified over the complete power supply and temperature range for production devices. Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur. |

| New                | This data sheet (which may be either Advance, Preliminary or Final) is a new addition to the data book.                                                                                                                                                                                     |

### DATA SHEET DESIGNATIONS

NOTE: Micron uses acronyms to refer to certain industry-standard-setting bodies. These are defined below: EIA/JEDEC—Electronics Industry Association/Joint Electron Device Engineering Council JEIDA—Japanese Electronics Industry Development Association PCMCIA—Personal Computer Memory Card International Association

\*Micron's Quality/Reliability Handbook is available by calling 208-368-3900.

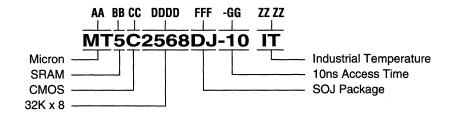

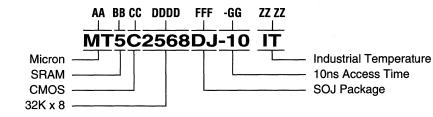

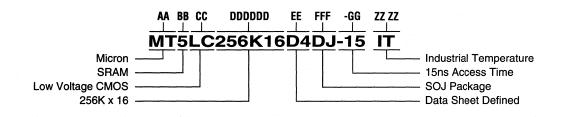

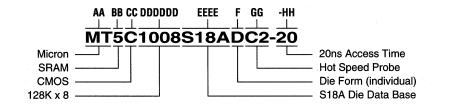

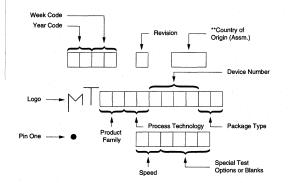

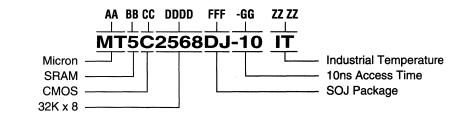

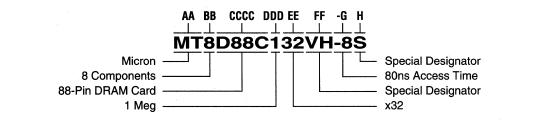

### PREFACE PRODUCT NUMBERING

#### **EXPANDED COMPONENT NUMBERING SYSTEM**

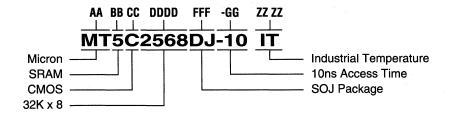

#### AA – PRODUCT LINE IDENTIFIER

Micron Product ...... MT

#### **BB – PRODUCT FAMILY**

| Flash            |    |

|------------------|----|

| DRAM             |    |

| SGRAM            | 41 |

| SRAM             |    |

| Synchronous SRAM |    |

#### **CC – PROCESS TECHNOLOGY**

| CMOS                   | C  |

|------------------------|----|

| Low Voltage CMOS       |    |

| Flash CMOS             | F  |

| Low Voltage Flash CMOS | LF |

#### DDDD – DEVICE NUMBER

(Can be modified to indicate variations)

| Flash            | Density, Configuration |

|------------------|------------------------|

| DRAM             |                        |

| TPDRAM           | Width, Density         |

| SRAM             | Total Bits, Width      |

| Synchronous SRAM | Density, Width         |

#### **E – DEVICE VERSIONS**

(Alphabetic characters only; located between D and F when required.)

| JEDEC Test Mode (4 Meg DRAM) | J |

|------------------------------|---|

| Errata on Base Part          | Q |

#### **FFF – PACKAGE CODES**

| PLASTIC                 |       |

|-------------------------|-------|

| DIP                     | Blank |

| DIP (Wide Body)         | W     |

| ZIP                     |       |

| LCC                     | EJ    |

| SOP/SOIC                | SG    |

| QFP                     | LG    |

| TSOP (Type I)           | VG    |

| TSOP (Type I, Reversed) |       |

| TSOP (Type II)          |       |

| TSOP (Reversed)         | RG    |

| TSOP (Longer)           | TL    |

| SOJ                     |       |

| SOJ (Reversed)          | DR    |

| SOJ (Longer)            |       |

#### EXPANDED COMPONENT NUMBERING SYSTEM (continued)

- -

#### **GG – ACCESS TIME**

| -5  | 5ns or 50ns   |

|-----|---------------|

| -6  | 6ns or 60ns   |

| -7  | 7ns or 70ns   |

| -8  | 8ns or 80ns   |

| -10 | 10ns or 100ns |

| -12 | 12ns or 120ns |

| -15 |               |

| -17 | 17ns          |

| -20 |               |

| -25 | 25ns          |

| -35 | 35ns          |

| -45 | 45ns          |

| -53 |               |

| -55 |               |

|     |               |

#### **ZZ ZZ – PROCESSING CODES**

(Multiple processing codes are separated by a space and are listed in hierarchical order.)

#### Example:

A DRAM supporting low power, extended refresh (L); low voltage (V) and the industrial temperature range (IT) would be indicated as V  $\,$  L  $\,$  IT.

| Interim     | . I |

|-------------|-----|

| Low Voltage | ٧   |

#### ZZ ZZ – PROCESSING CODES (continued)

| DRAMs                                                                                                                                                  |                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Low Power (Extended Refresh)                                                                                                                           | L                                      |

| Low Power (Self Refresh/Extended Refresh)                                                                                                              | S                                      |

| SRAMs                                                                                                                                                  |                                        |

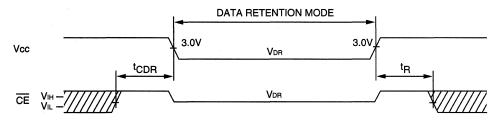

| Low Volt Data Retention                                                                                                                                | L                                      |

| Low Power                                                                                                                                              | P                                      |

| Low Power, Low Volt Data Retention                                                                                                                     | LP                                     |

| Flash                                                                                                                                                  |                                        |

| Bottom Boot                                                                                                                                            | B                                      |

| Top Boot                                                                                                                                               | T                                      |

| EPI Wafer                                                                                                                                              |                                        |

| Commercial Testing                                                                                                                                     |                                        |

| $0^{\circ}C$ to $+70^{\circ}C$                                                                                                                         | Riank                                  |

|                                                                                                                                                        |                                        |

| -40°C to +85°C                                                                                                                                         | IT                                     |

| -40°C to +85°C<br>-40°C to +125°C                                                                                                                      | IT<br>AT                               |

| -40°C to +85°C                                                                                                                                         | IT<br>AT                               |

| -40°C to +85°C<br>-40°C to +125°C                                                                                                                      | IT<br>AT                               |

| -40°C to +85°C<br>-40°C to +125°C<br>-55°C to +125°C<br>Special Processing<br>Engineering Sample                                                       | IT<br>AT<br>XT<br>ES                   |

| -40°C to +85°C<br>-40°C to +125°C<br>-55°C to +125°C<br>Special Processing<br>Engineering Sample<br>Mechanical Sample                                  | IT<br>AT<br>XT<br>ES<br>MS             |

| -40°C to +85°C<br>-40°C to +125°C<br>-55°C to +125°C<br>Special Processing<br>Engineering Sample<br>Mechanical Sample<br>Sample Kit*                   | IT<br>AT<br>XT<br>ES<br>               |

| -40°C to +85°C<br>-40°C to +125°C<br>-55°C to +125°C<br>Special Processing<br>Engineering Sample<br>Mechanical Sample<br>Sample Kit*<br>Tape-and-Reel* | IT<br>AT<br>XT<br>ES<br>MS<br>SK<br>TR |

| -40°C to +85°C<br>-40°C to +125°C<br>-55°C to +125°C<br>Special Processing<br>Engineering Sample<br>Mechanical Sample<br>Sample Kit*                   | IT<br>AT<br>XT<br>ES<br>MS<br>SK<br>TR |

\* Used in device order codes; this code is not marked on device.

#### PREFACE PRODUCT NUMBERING

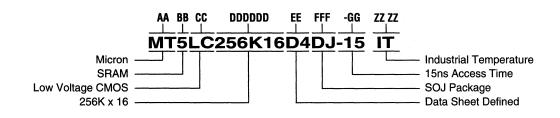

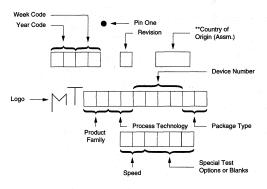

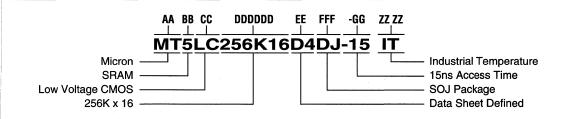

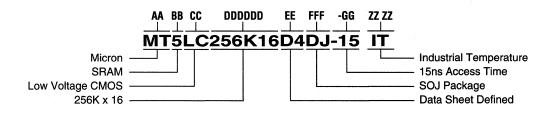

#### **NEW COMPONENT NUMBERING SYSTEM**

#### **AA - PRODUCT LINE IDENTIFIER**

Micron Product ..... MT

#### **BB – PRODUCT FAMILY**

| 4  |

|----|

| 41 |

| 43 |

| 48 |

| 5  |

| 58 |

|    |

#### **CC – PROCESS TECHNOLOGY**

| CMOS               | C |

|--------------------|---|

| Low Voltage CMOS   |   |

| BICMOS             | В |

| Low Voltage BiCMOS |   |

#### DDDDDD - DEVICE NUMBER

Depth, Width

Example:

| 1M16 = 1 megabit deep by 16 bits v<br>memory. |          |

|-----------------------------------------------|----------|

| No Letter                                     | Bits     |

| К                                             |          |

| Μ                                             | Megabits |

| G                                             | Gigabits |

#### **EE – DEVICE VERSIONS**

(The first character is an alphabetic character only; the second character is a numeric character only.) Specified by individual data sheet.

#### **FFF – PACKAGE CODES**

| Plastic         |       |

|-----------------|-------|

| DIP             | Blank |

| DIP (Wide Body) | W     |

| ZIP             |       |

| LCC             | EJ    |

| SOP/SOIC        | SG    |

| QFP             | LG    |

| TSOP (Type II)  | TG    |

| TSOP (Reversed) | RG    |

| TSOP (Longer)   | TL    |

| SOJ             |       |

| SOJ (Wide)      | DW    |

| SOJ (Reversed)  |       |

| SOJ (Longer)    |       |

|                 |       |

## **NEW COMPONENT NUMBERING SYSTEM (continued)**

#### **GG – ACCESS TIME**

| -5  |          | 5ns or 50ns   |

|-----|----------|---------------|

|     |          |               |

| -7  |          | 7ns or 70ns   |

| -8  |          | 8ns or 80ns   |

| -9  |          | 9ns or 90ns   |

| -10 |          | 10ns or 100ns |

| -12 |          | 12ns or 120ns |

| -15 |          | 15ns or 150ns |

| -17 | •••••••• | 17ns          |

| -20 |          | 20ns          |

|     |          |               |

| -35 |          | 35ns          |

| -45 |          | 45ns          |

|     |          |               |

| -55 |          | 55ns          |

|     |          |               |

#### **ZZ ZZ – PROCESSING CODES**

(Multiple processing codes are separated by a space and are listed in hierarchical order.)

#### Example:

A DRAM supporting low power, extended refresh (L); low voltage (V) and the industrial temperature range (IT) would be indicated as V L IT.

| Interim     | <br> |   |

|-------------|------|---|

| Low Voltage | <br> | V |

#### ZZ ZZ – PROCESSING CODES (continued)

| DRAMs                                    |       |

|------------------------------------------|-------|

| Low Power (Extended Refresh)             | L     |

| Low Power (Self Refresh/Extended Refresh |       |

| SRAMs                                    |       |

| Low Volt Data Retention                  | L     |

| Low Power                                | P     |

| Low Volt Data Retention, Low Power       | LP    |

| EPI Wafer                                |       |

| Commercial Testing                       |       |

| 0°C to +70°C                             | Blank |

| -40°C to +85°C                           | IT    |

| -40°C to +125°C                          |       |

| -55°C to +125°C                          | XT    |

| Special Processing                       |       |

| Engineering Sample                       | ES    |

| Mechanical Sample                        | MS    |

| Sample Kit*                              | SK    |

| Tape-and-Reel*                           | TR    |

| Bar Code*                                | BC    |

|                                          |       |

\* Used in device order codes; this code is not marked on device.

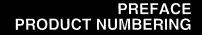

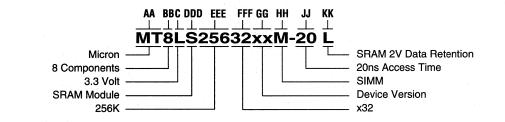

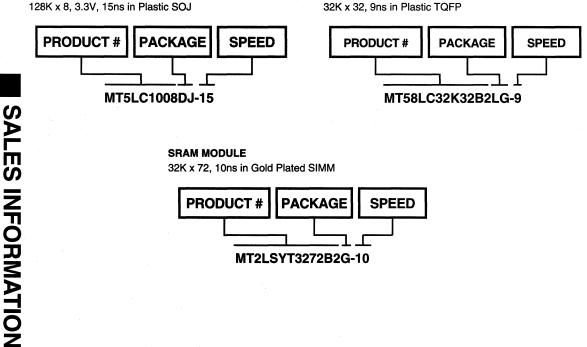

#### **MODULE NUMBERING SYSTEM**

#### **AA – PRODUCT LINE IDENTIFIER**

Micron Semiconductor Product ..... MT

#### **BB – NUMBER OF MEMORY COMPONENTS**

#### **C – PROCESS TECHNOLOGY**

| LOW VOLTAGE (3.3V) | L |  |

|--------------------|---|--|

|                    |   |  |

#### DDD – RAM FAMILY

| D   |

|-----|

| DT  |

| S   |

| ST  |

| SY  |

| SYT |

|     |

#### EEE – DEPTH

#### FFF – WIDTH

#### **GG – DEVICE VERSIONS**

Specified by individual data sheet (Synchronous SRAM only)

#### HH – PACKAGE CODE

| Gold Plated SIMM/DIMM                         | G  |

|-----------------------------------------------|----|

| ZIP                                           | Z  |

| SIP                                           | N  |

| SIMM/DIMM                                     | M  |

| Small Outline DIMM                            | H  |

| Small Outline Gold DIMM                       | HG |

| Double-Sided SIMM (1 or 4 Meg x 36 Only)      | DM |

| Double-Sided SIMM (Gold 1 or 4 Meg x 36 Only) | DG |

#### JJ - ACCESS TIME

| -10 | 10ns |

|-----|------|

| -12 |      |

| -15 |      |

| -17 |      |

| -20 |      |

| -25 |      |

| -35 | 35ns |

| -6  |      |

| -7  |      |

| -8  |      |

|     |      |

#### KK – MODULE SPECIAL DESIGNATOR

#### SRAM

| 2V data retention            | - 1 - C |

|------------------------------|---------|

| Low Power                    |         |

| Low Power, 2V data retention | LP      |

| DRAM                         |         |

| Low Power (Extended Refresh) | L       |

| ECC                          | C       |

| Extended Data Out            | X       |

| Self Refresh                 | S       |

| 16 Meg DRAM 4,096 Refresh    | B       |

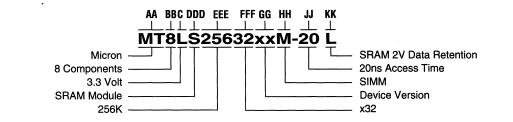

## PREFACE PRODUCT NUMBERING

#### DRAM CARD NUMBERING SYSTEM

#### PREFACE PRODUCT NUMBERING

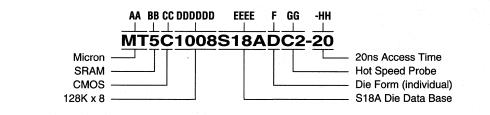

#### **DIE PRODUCT NUMBERING SYSTEM**

#### **AA – PRODUCT LINE IDENTIFIER**

| Component Product   | MT |

|---------------------|----|

| BB – PRODUCT FAMILY |    |

| SRAM                                  |  |

|---------------------------------------|--|

| DRAM                                  |  |

| Synchronous SRAM                      |  |

| • • • • • • • • • • • • • • • • • • • |  |

#### CC – PROCESS TECHNOLOGY

| CMOS             | C  |

|------------------|----|

| Low Voltage CMOS | LC |

#### DDDDDD - DEVICE NUMBER

| When no alpha character appears | as part of this section, the |

|---------------------------------|------------------------------|

| section is defined as:          |                              |

| DRAM                            | Width, Density               |

| SRAM                            | Total Bits, Width            |

| Synchronous SRAM                | Depth, Width                 |

When an alpha character occurs as part of this section, the section is defined as: Depth, Width

#### Example:

1M16 = 1 megabit deep by 16 bits wide = 16 megabits of total memory.

| No Letter | Bits     |

|-----------|----------|

| К         | Kilobits |

|           | Megabits |

|           | Gigabits |

#### **EEEE – DIE DATA BASE REVISION**

#### F – FORM

| Die Form | D |

|----------|---|

|          | W |

#### **GG – TESTING LEVELS**

| Standard Probe (0° to 70°C)  | C1 |

|------------------------------|----|

| Hot Speed Probe (0° to 70°C) | C2 |

| Known Good Die (0° to 70°C)  | C3 |

## HH – ACCESS TIME

| (Applicable for C2 and C3 only) |               |

|---------------------------------|---------------|

| -5                              | 5ns or 50ns   |

| -6                              | 6ns or 60ns   |

| -7                              | 7ns or 70ns   |

| -8                              | 8ns or 80ns   |

| -9                              |               |

| -10                             | 10ns or 100ns |

| -12                             | 12ns or 120ns |

| -15                             | 15ns or 150ns |

| -17                             | 17ns          |

| -20                             | 20ns          |

| -25                             | 25ns          |

| -35                             | 35ns          |

| -45                             | 45ns          |

| -50 (SRAM only)                 | 50ns          |

| -SS (C2 only)                   |               |

|                                 |               |

## **5V ASYNCHRONOUS SRAMs**

| MT5C2561    | 256K x 1    |

|-------------|-------------|

| MT5C1001    | 1 Meg x 1   |

| MT5C2564    | U           |

| MT5C2565    | 64K x 4     |

| MT5C1005    |             |

| MT5C256K4A1 |             |

| MT5C2568    |             |

| MT5C1008    |             |

| MT5C128K8A1 |             |

| MT5C64K16A1 | 64K x 16    |

| СЕ          | CHIP ENABLE |

| BE          | BYTE ENABLE |

## **3V ASYNCHRONOUS SRAMs**

| MT5LC2561     |           |

|---------------|-----------|

| MT5LC1001     |           |

| MT5LC2564     |           |

| MT5LC2565     | 64K x 4   |

| MT5LC1005     |           |

| MT5LC256K4D4  | 256K x 4  |

| MT5LC1M4D4    | 1 Meg x 4 |

| MT5LC2568     |           |

| MT5LC1008     | 128K x 8  |

| MT5LC128K8D4  |           |

| MT5LC512K8D4  | 512K x 8  |

| MT5LC64K16D4  | 64K x 16  |

| MT5LC256K16D4 | 256K x 16 |

| CE<br>BE      |           |

|               |           |

#### <u>CE</u> only ..... 1-1 <u>CE</u> only ..... 1-11 <u>CE</u> only ..... 1-21 $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ ..... 1-31 <u>CE & OE</u> ..... 1-41 CE & OE, Revolutionary Pinout ..... 1-51 <u>CE & OE</u> ..... 1-61 <u>CE1</u>, CE2 & <u>OE</u>...... 1-71 CE & OE, Revolutionary Pinout ..... 1-81 BE, CE & OE, Revolutionary Pinout ..... 1-91 ..... OUTPUT ENABLE OE .....

REVOLUTIONARY PINOUT ....... CENTER PIN POWER AND GROUND

## PAGE

| $\overline{\text{CE}}$ only with separate I/O                          | 2-1              |

|------------------------------------------------------------------------|------------------|

| CE only with separate I/O                                              | 2-9              |

| CE only                                                                | 2-17             |

| CE & OE                                                                | 2-25             |

| $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$        | 2-33             |

| CE, Revolutionary Pinout                                               | 2-41             |

| CE & OE, Revolutionary Pinout                                          | 2-51             |

| $\overline{\operatorname{CE}} \And \overline{\operatorname{OE}}$       | 2-59             |

| $\overline{\text{CE1}}$ , CE2 & $\overline{\text{OE}}$                 | 2-67             |

| CE & OE, Revolutionary Pinout                                          | 2-75             |

| CE & OE, Revolutionary Pinout                                          | 2-85             |

| BE, CE & OE, Revolutionary Pinout                                      | 2-93             |

| $\overline{\text{BE}}, \overline{\text{CE}} \And \overline{\text{OE}}$ | 2-103            |

|                                                                        | ENABLE<br>GROUND |

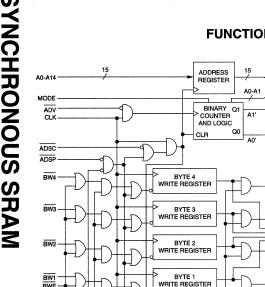

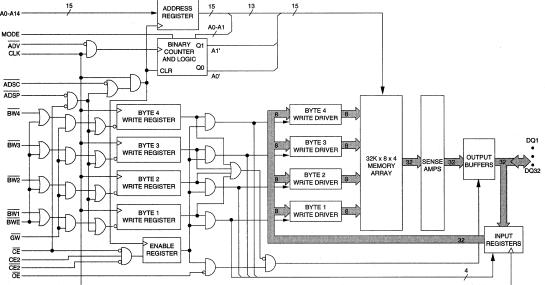

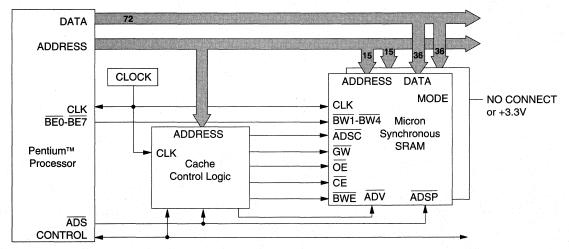

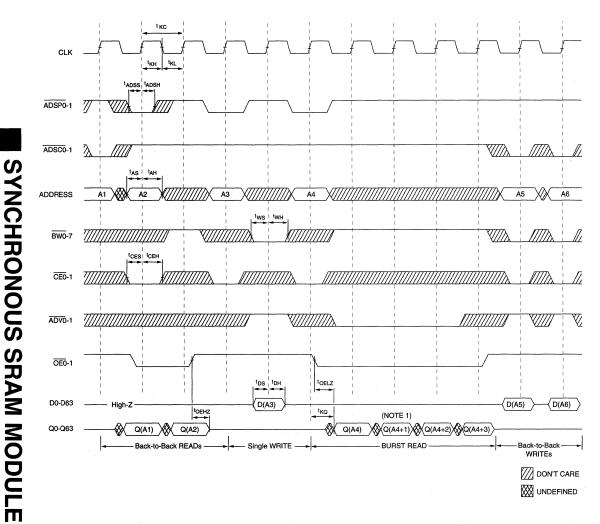

## SYNCHRONOUS SRAMs

AON

| MT58LC64K18B2 | 64K x 18  |

|---------------|-----------|

| MT58LC64K18M1 | 64K x 18  |

| MT58LC64K18C4 | 64K x 18  |

| MT58LC64K18A6 | 64K x 18  |

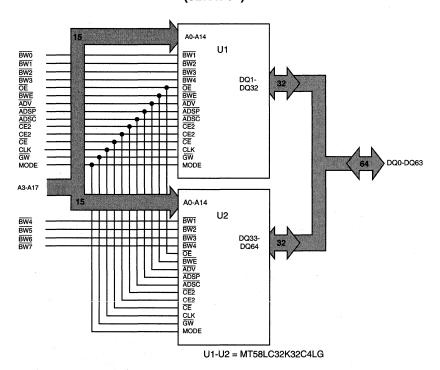

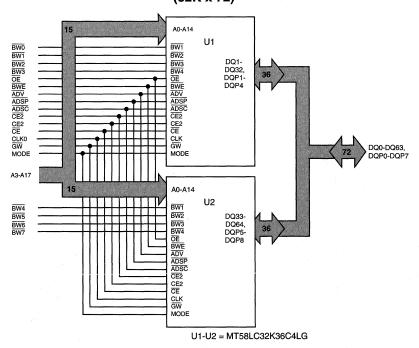

| MT58LC32K32B2 | .32K x 32 |

| MT58LC32K32C4 | .32K x 32 |

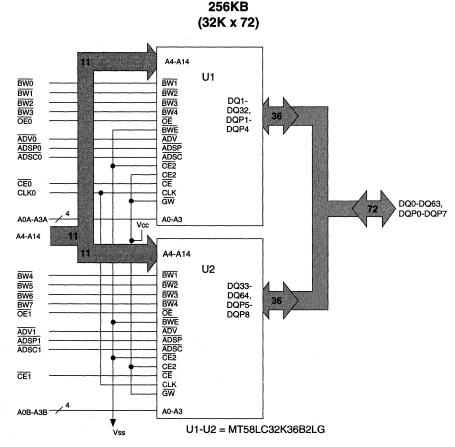

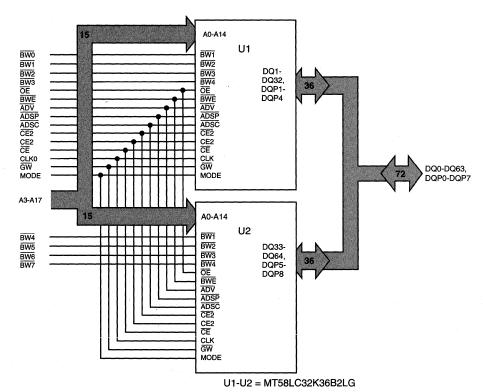

| MT58LC32K36B2 | .32K x 36 |

| MT58LC32K36C4 | .32K x 36 |

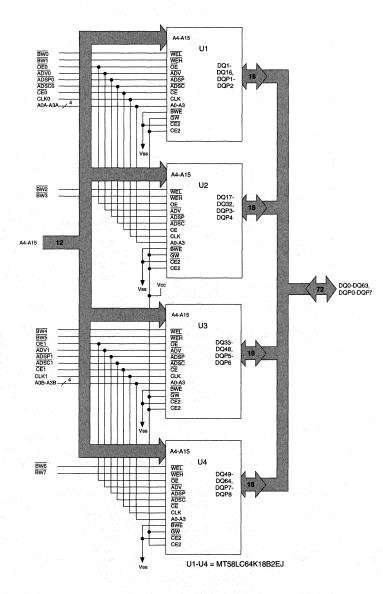

|               |           |

| SyncBurst <sup>™</sup> , Interleaved, Linear | 3-1  |

|----------------------------------------------|------|

| SyncBurst, Linear                            | 3-1  |

| SyncBurst, Interleaved, Linear               | 3-17 |

| SyncBurst, Linear                            | 3-17 |

| SyncBurst                                    | 3-33 |

| SyncBurst, Interleaved, Pipelined            | 3-49 |

| SyncBurst, Interleaved                       | 3-65 |

| SyncBurst, Interleaved, Pipelined            | 3-81 |

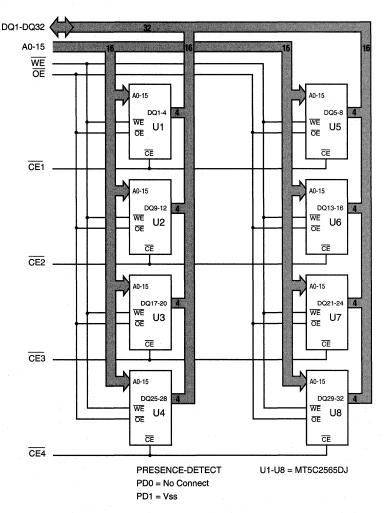

## **SRAM MODULES**

| MT8S6432               | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-1     |

|------------------------|-----------------------------------------------------------------|---------|

| MT8LS643264K x 32      | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-9     |

| MT4S12832 128K x 32    | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-17    |

| MT4LS12832128K x 32    | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-25    |

| MT8S25632              | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-33    |

| MT8LS25632             | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-41    |

| MT8LS1321 Meg x 32     | $\overline{\operatorname{CE}}$ & $\overline{\operatorname{OE}}$ | 4-49    |

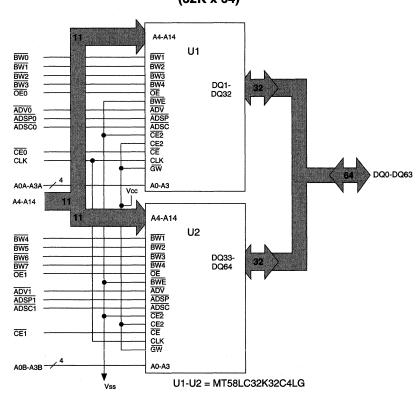

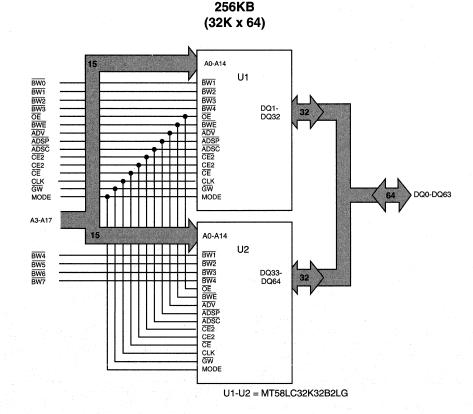

| MT2LSYT3264T1 32K x 64 | SyncBurst, Linear                                               | 4-57    |

| MT2LSYT3264T2 32K x 64 | SyncBurst, Interleaved                                          | 4-57    |

| MT2LSYT3264T4 32K x 64 | SyncBurst, Interleaved, Pipelined                               | 4-69    |

| MT2LSYT3264T6 32K x 64 | SyncBurst, Linear, Pipelined                                    | 4-69    |

| MT2LSYT3264B2 32K x 64 | SyncBurst, Interleaved, Linear                                  | 4-81    |

| MT2LSYT3264C4 32K x 64 | SyncBurst, Interleaved, Linear,                                 |         |

|                        | Pipelined                                                       | 4-87    |

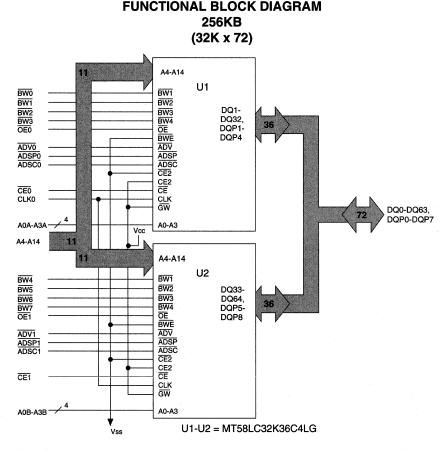

| MT2LSYT3272T1 32K x 72 | SyncBurst, Linear                                               | 4-93    |

| MT2LSYT3272T2 32K x 72 | SyncBurst, Interleaved                                          | 4-93    |

| MT2LSYT3272T4 32K x 72 | SyncBurst, Interleaved, Pipelined                               | 4-107   |

| MT2LSYT3272T6 32K x 72 | SyncBurst, Linear, Pipelined                                    | 4-107   |

| MT2LSYT3272B2 32K x 72 | SyncBurst, Interleaved, Linear                                  | 4-121   |

| MT2LSYT3272C4 32K x 72 | SyncBurst, Interleaved, Linear,                                 |         |

|                        | Pipelined                                                       | 4-129   |

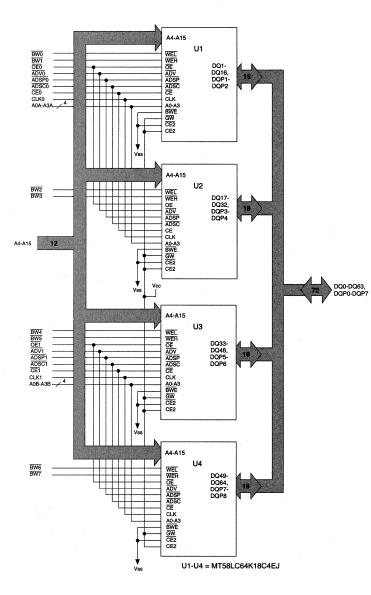

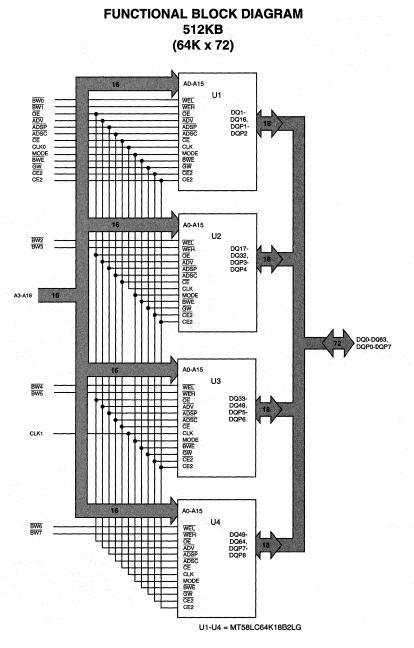

| MT4LSY6472T1 64K x 72  | SyncBurst, Linear                                               | 4-93    |

| MT4LSY6472T2 64K x 72  | SyncBurst, Interleaved                                          | 4-93    |

| MT4LSY6472T4 64K x 72  | SyncBurst, Interleaved, Pipelined                               | 4-107   |

| MT4LSY6472T6 64K x 72  | SyncBurst, Linear, Pipelined                                    | 4-107   |

| MT4LSYT6472B2          | SyncBurst, Interleaved, Linear                                  | 4-121   |

| MT4LSYT6472C4          | SyncBurst, Interleaved, Linear,                                 |         |

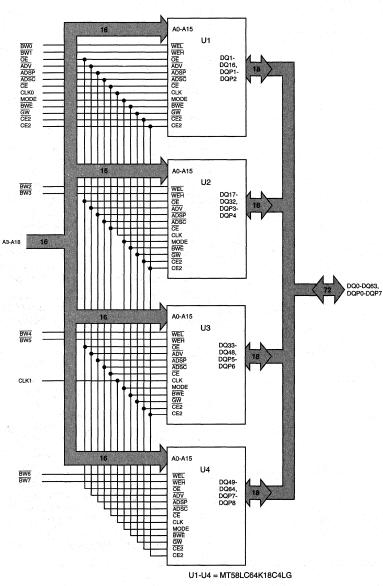

|                        | Pipelined                                                       | 4-129   |

| CE CHIP ENABLE         | ое оuтрит                                                       |         |

| CD CHIF ENABLE         | 01101                                                           | DINADED |

PREFACE Rev. 11/94

## PAGE

MICRON

## PAGE

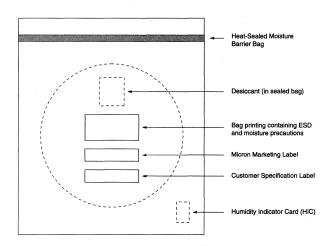

| TN-00-01 | Moisture Absorption in Plastic Packages                       | 5-1  |

|----------|---------------------------------------------------------------|------|

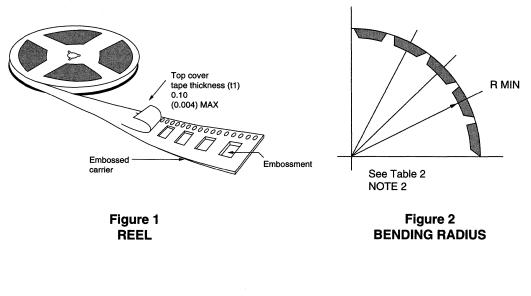

| TN-00-02 | Tape-and-Reel Procedures                                      | 5-3  |

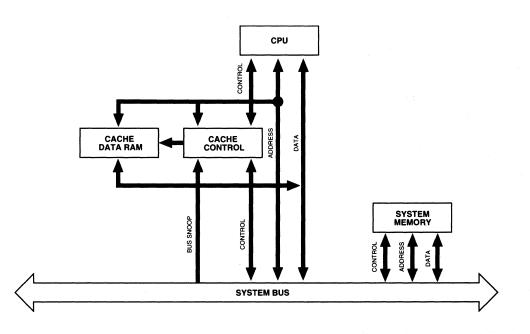

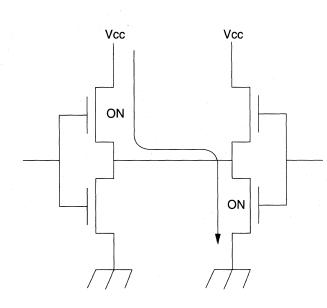

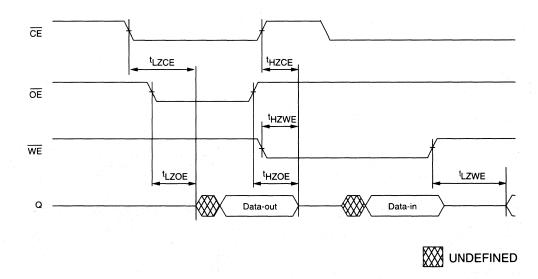

| TN-05-02 | SRAM Bus Contention Design Considerations                     | 5-9  |

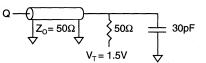

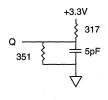

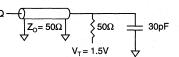

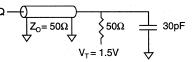

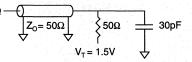

| TN-05-03 | 5V SRAM Capacitive Loading                                    | 5-13 |

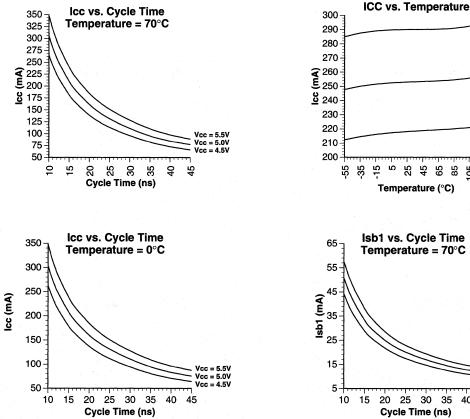

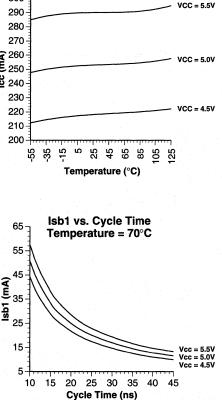

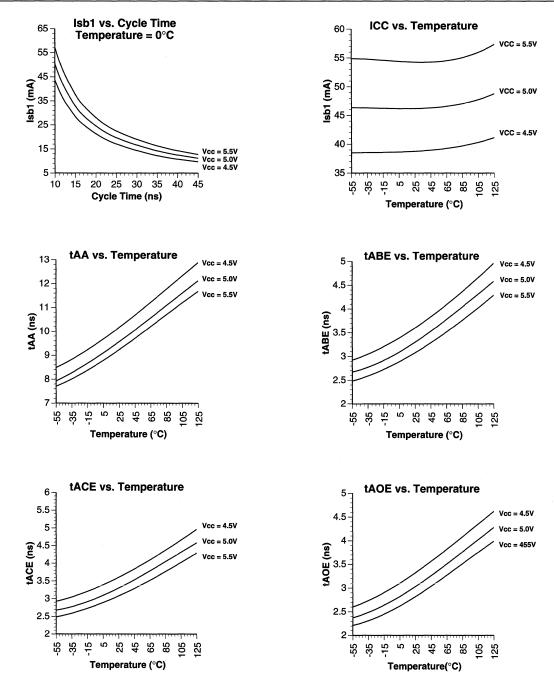

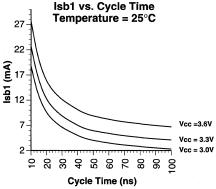

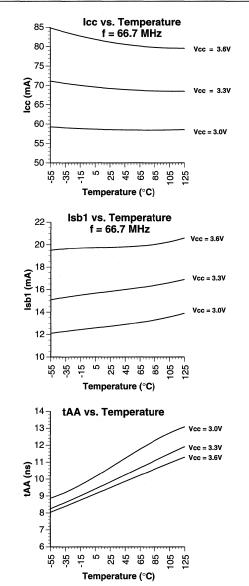

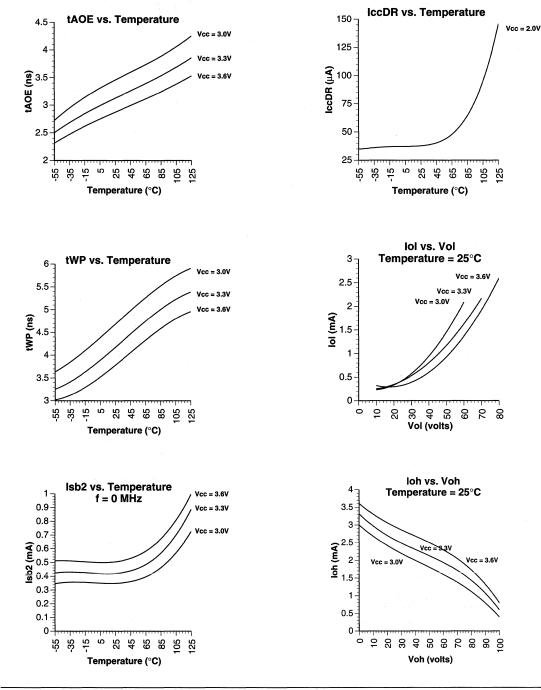

| TN-05-06 | 1 Meg Evolutionary Pinout SRAM Typical (5V) Operating Curves  | 5-15 |

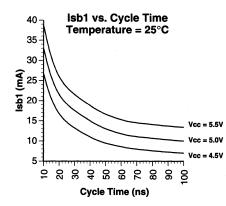

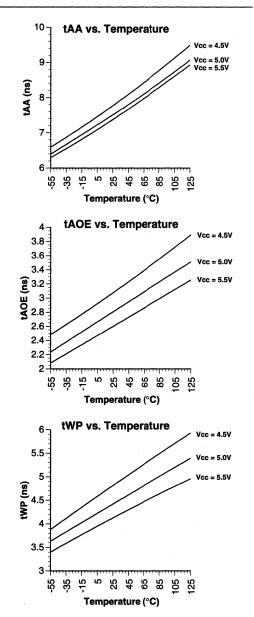

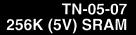

| TN-05-07 | 256K SRAM Typical (5V) Operating Curves                       | 5-17 |

| TN-05-13 | 1 Meg Low-Power SRAMs                                         | 5-19 |

| TN-05-14 | SRAM Thermal Design Considerations                            | 5-23 |

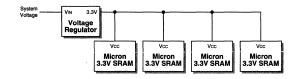

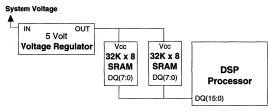

| TN-05-16 | A Designer's Guide to 3.3V SRAMs                              | 5-29 |

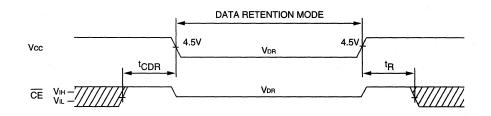

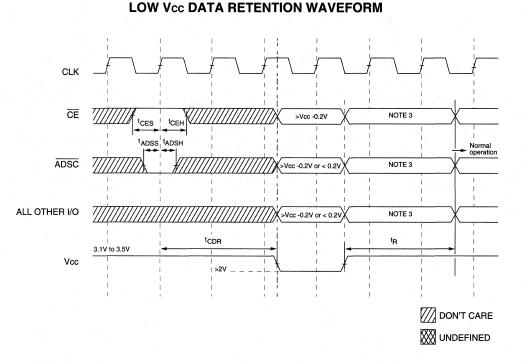

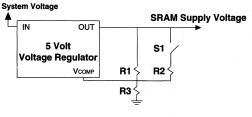

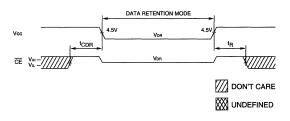

| TN-05-17 | Low-Power Memory Design Using Data Retention                  | 5-35 |

| TN-05-19 | SRAMs and Low-Voltage Data Retention                          | 5-39 |

| TN-05-20 | 3.3V SRAM Capacitive Loading                                  | 5-41 |

| TN-05-21 | High-Speed Memory Design Techniques                           | 5-43 |

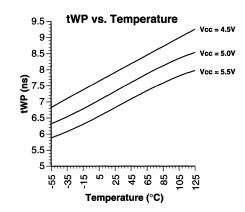

| TN-05-22 | 1 Meg Revolutionary Pinout SRAM Typical (5V) Operating Curves | 5-49 |

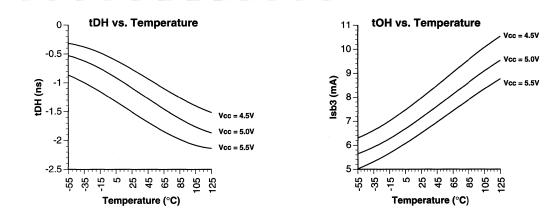

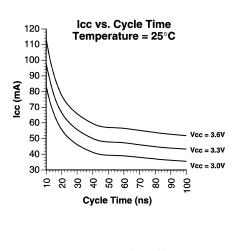

| TN-05-23 | 256K SRAM Typical (3.3V) Operating Curves                     | 5-53 |

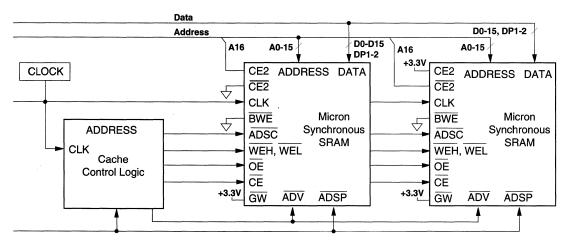

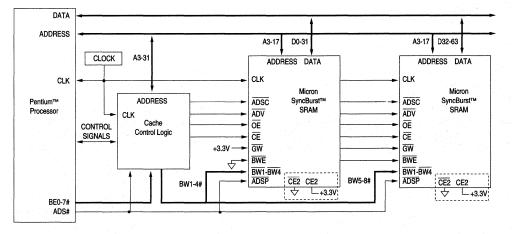

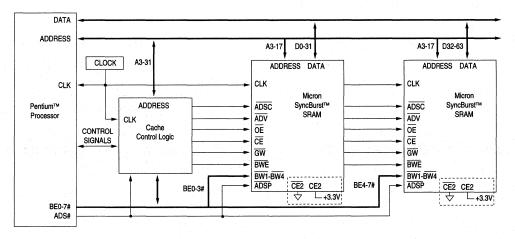

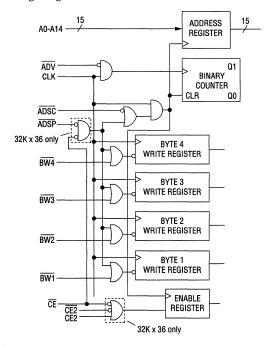

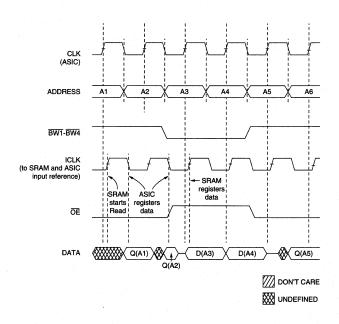

| TN-58-01 | SyncBurst™ SRAM Design for Compatibility                      | 5-55 |

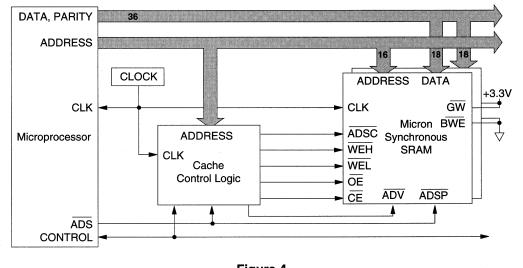

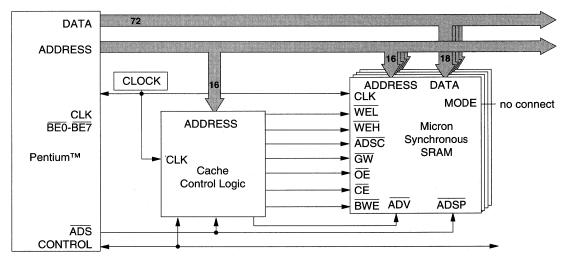

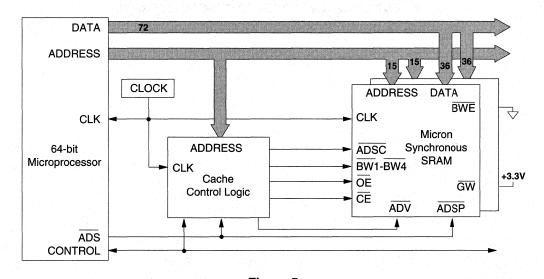

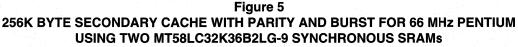

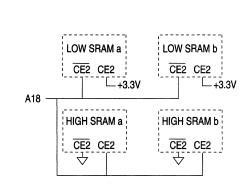

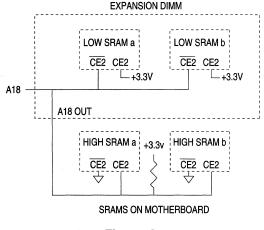

| TN-58-02 | Design Tips: 32K x 36 Synchronous SRAM                        | 5-63 |

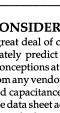

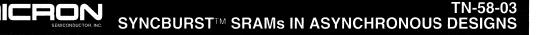

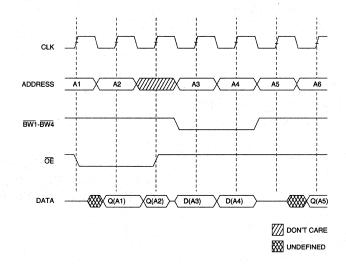

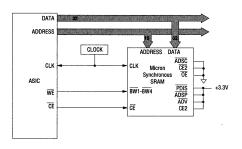

| TN-58-03 | SyncBurst™ SRAMs in Asynchronous Designs                      | 5-69 |

|          |                                                               |      |

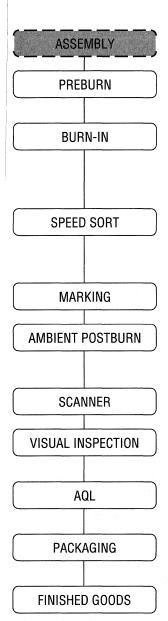

## PRODUCT RELIABILITY

### PAGE

| Overview           |   | 6-1 |

|--------------------|---|-----|

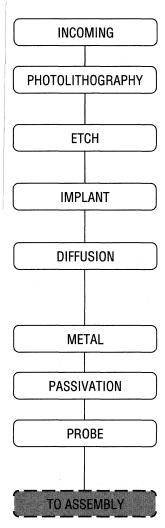

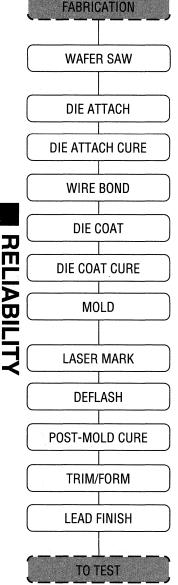

| Process Flow Chart | e | 6-9 |

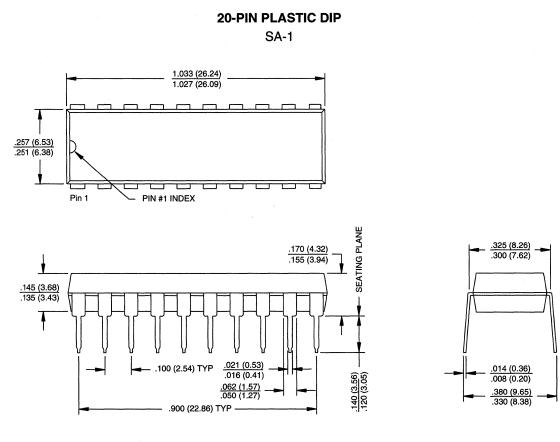

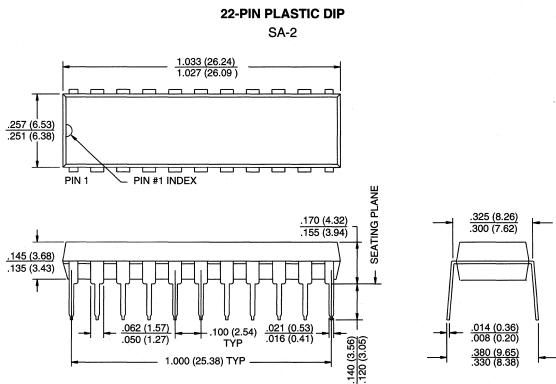

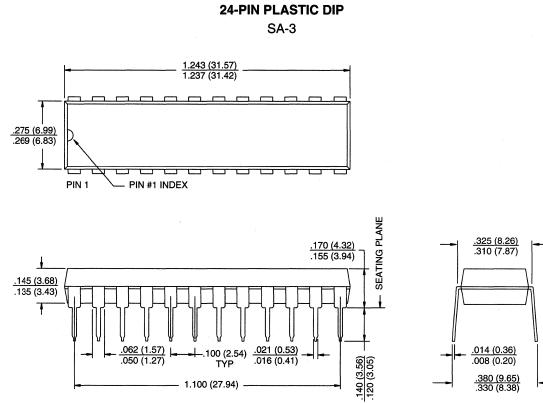

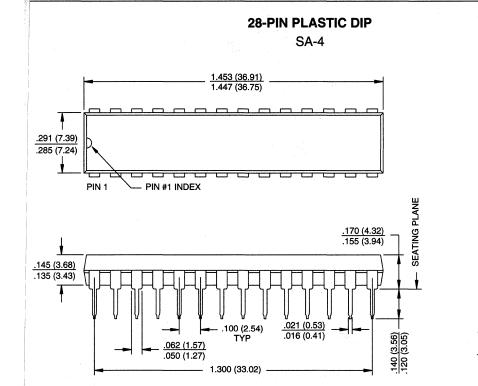

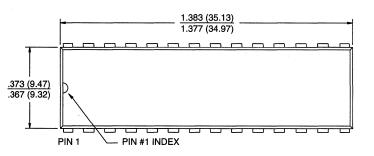

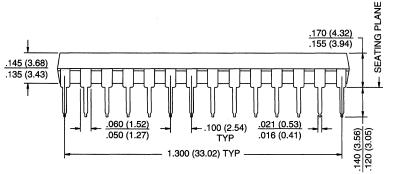

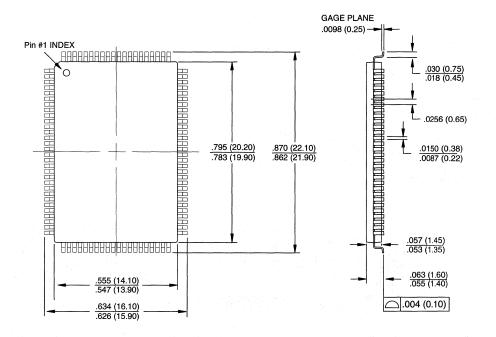

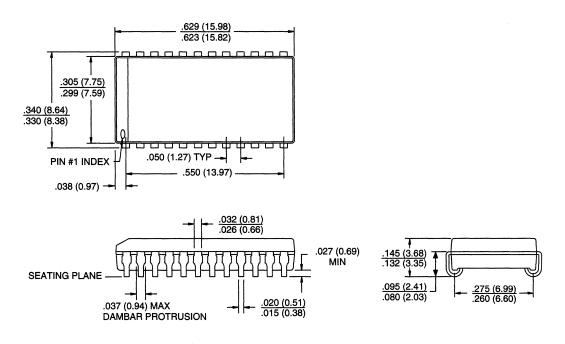

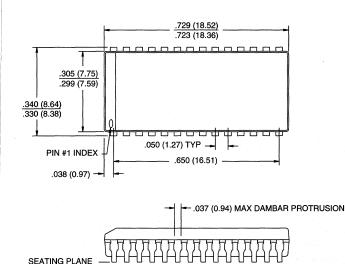

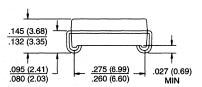

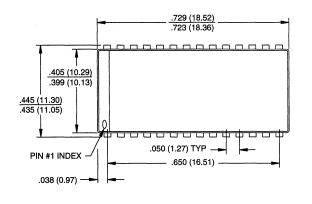

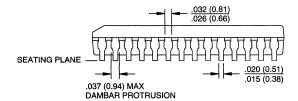

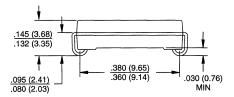

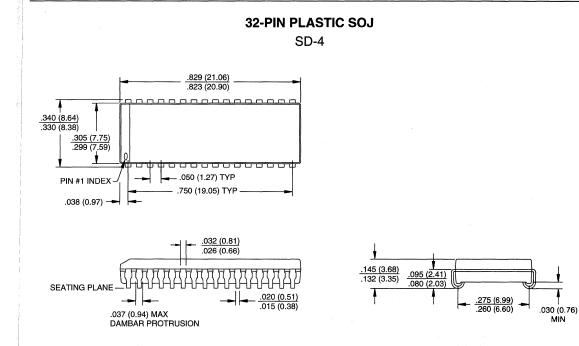

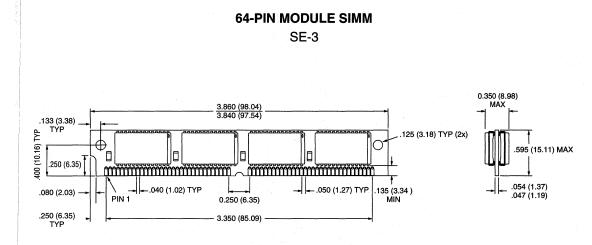

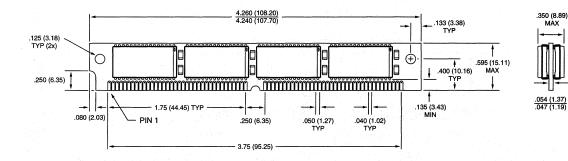

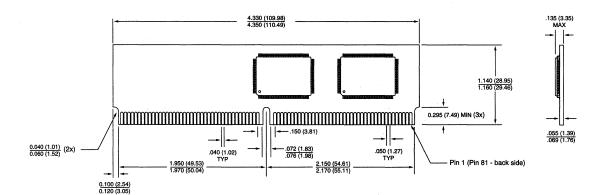

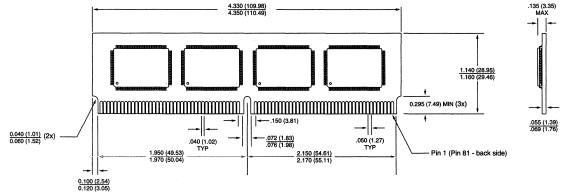

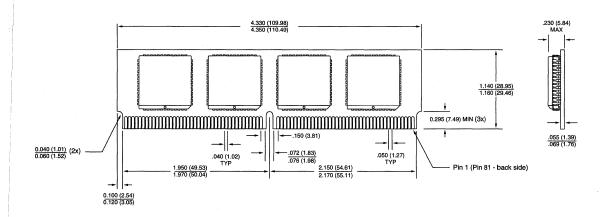

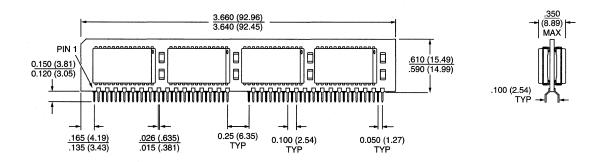

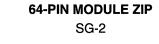

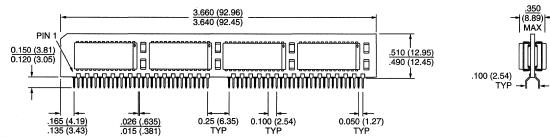

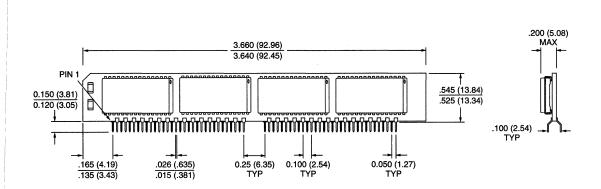

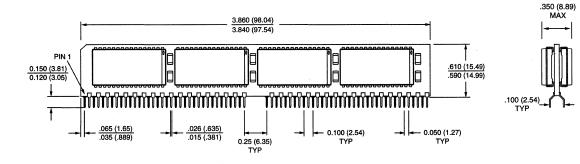

## **PACKAGE INFORMATION**

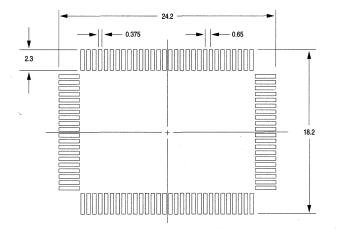

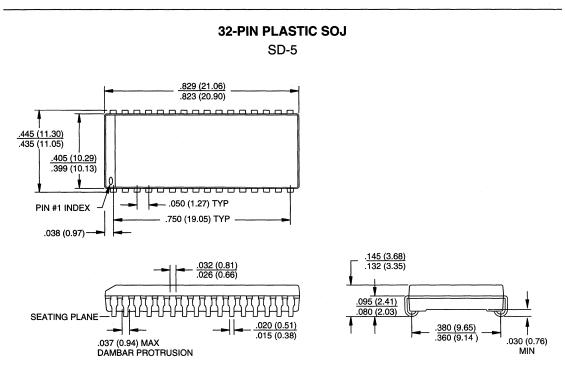

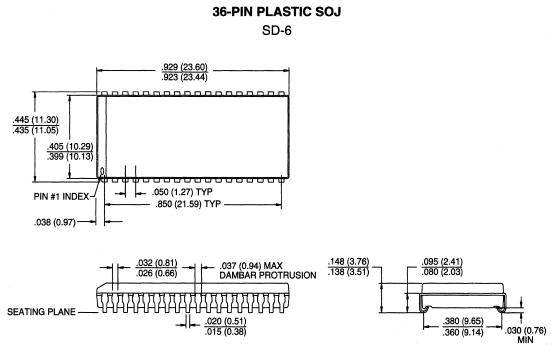

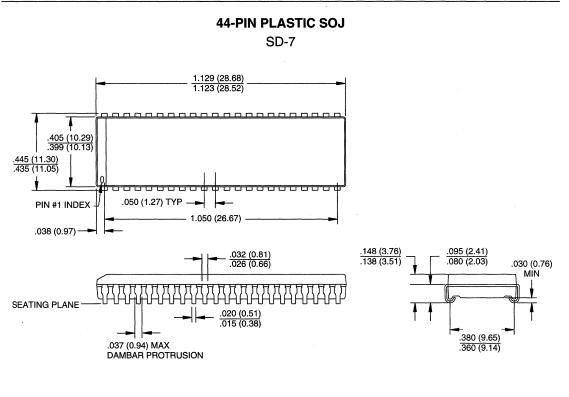

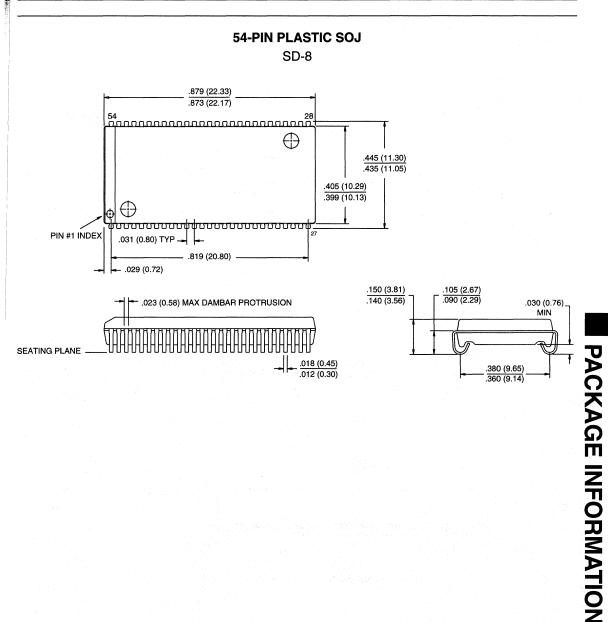

| Index            | 7-1 |

|------------------|-----|

| Package Drawings | 7-2 |

## SALES INFORMATION

## PAGE

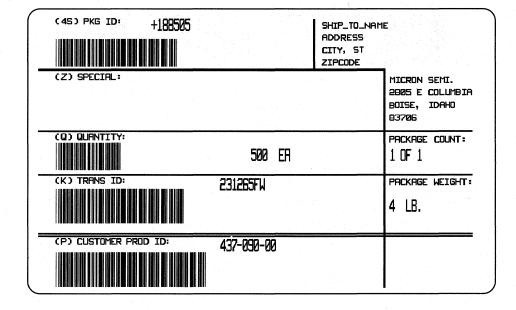

| Customer Service Notes                                | 8-1  |

|-------------------------------------------------------|------|

| Product Numbering System                              | 8-15 |

| Ordering Information and Examples                     | 8-22 |

| North American Sales Representatives and Distributors | 8-23 |

| International Sales Representatives and Distributors  | 8-35 |

## NUMERICAL INDEX

MIC

RON

| Part #, MT: |               |           |

|-------------|---------------|-----------|

| 2LSYT3264B2 | . SRAM MODULE | <br>4-81  |

| 2LSYT3264C4 | . SRAM MODULE | <br>4-87  |

| 2LSYT3264T1 | . SRAM MODULE | <br>4-57  |

| 2LSYT3264T2 | . SRAM MODULE | <br>4-57  |

| 2LSYT3264T4 | . SRAM MODULE | <br>4-69  |

| 2LSYT3264T6 | . SRAM MODULE | <br>4-69  |

| 2LSYT3272B2 | . SRAM MODULE | <br>4-121 |

| 2LSYT3272C4 | . SRAM MODULE | <br>4-129 |

| 2LSYT3272T1 | . SRAM MODULE | <br>4-93  |

| 2LSYT3272T2 | . SRAM MODULE | <br>4-93  |

| 2LSYT3272T4 | . SRAM MODULE | <br>4-107 |

| 2LSYT3272T6 | . SRAM MODULE | <br>4-107 |

| 4LS12832    | . SRAM MODULE | <br>4-25  |

| 4LSY6472T1  | . SRAM MODULE | <br>4-93  |

| 4LSY6472T2  | . SRAM MODULE | <br>4-93  |

| 4LSY6472T4  | . SRAM MODULE | <br>4-107 |

| 4LSY6472T6  | . SRAM MODULE | <br>4-107 |

| 4LSYT6472B2 | . SRAM MODULE | <br>4-121 |

| 4LSYT6472C4 | . SRAM MODULE | <br>4-129 |

| 4S12832     | . SRAM MODULE | <br>4-17  |

| 58LC32K32B2 | SYNC. SRAM    | <br>3-33  |

| 58LC32K32C4 | SYNC. SRAM    | 3-49      |

| 58LC32K36B2 |               | <br>3-65  |

| 58LC32K36C4 | SYNC. SRAM    | 3-81      |

| 58LC64K18A6 | SYNC. SRAM    | <br>3-17  |

| 58LC64K18B2 | SYNC. SRAM    | <br>3-1   |

| 58LC64K18C4 | SYNC. SRAM    | <br>3-17  |

| 58LC64K18M1 | SYNC. SRAM    | <br>3-1   |

| 5C1001      |               | <br>1-11  |

| 5C1005      | 5V SRAM       | 1-41      |

| 5C1008      | 5V SRAM       | 1-71      |

| 5C128K8A1   | 5V SRAM       | 1-81      |

| 5C2561      | 5V SRAM       | <br>1-1   |

| 5C2564      | 5V SRAM       | 1-21      |

| 5C2565      | 5V SRAM       | <br>1-31  |

| 5C2568      | 5V SRAM       | <br>1-61  |

| 5C256K4A1   |               | <br>1-51  |

| 5C64K16A1   |               | <br>1-91  |

| 5LC1001     | 3.3V SRAM     | <br>2-9   |

|             |               |           |

## NUMERICAL INDEX (continued)

RON

M

| Part #, MT: |             |

|-------------|-------------|

|             | 3.3V SRAM   |

| 5LC2561     | 3.3V SRAM   |

| 5LC2564     | 3.3V SRAM   |

|             | 3.3V SRAM   |

|             | 3.3V SRAM   |

|             | 3.3V SRAM   |

| 5LC256K4D4  | 3.3V SRAM   |

|             | 3.3V SRAM   |

| 5LC64K16D4  | 3.3V SRAM   |

| 8LS132      | SRAM MODULE |

|             | SRAM MODULE |

|             | SRAM MODULE |

|             | SRAM MODULE |

| 856432      | SRAM MODULE |

|             |             |

| • • • • • • • • • • • • • • • • • • • • |                       | 2-33    |

|-----------------------------------------|-----------------------|---------|

|                                         |                       | 2-67    |

|                                         | ••••••                | 2-75    |

|                                         |                       | 2-51    |

|                                         |                       | 2-1     |

|                                         |                       | 2-17    |

| ••••••                                  |                       |         |

|                                         |                       | 2-25    |

|                                         |                       | 2-59    |

|                                         |                       | 2-103   |

|                                         |                       | 2-41    |

|                                         |                       | 2-85    |

|                                         |                       | 2-93    |

|                                         |                       | 4-49    |

| ••••••                                  |                       |         |

|                                         | e parte de la company | 4-41    |

|                                         |                       | 4-9     |

|                                         |                       | 4-33    |

|                                         |                       | 4-1     |

| •••••                                   |                       | <u></u> |

## **5V ASYNCHRONOUS SRAM PRODUCT SELECTION GUIDE**

ION

| Memory        | Memory Control                                  |             | Access             | Package/I |     |      |

|---------------|-------------------------------------------------|-------------|--------------------|-----------|-----|------|

| Configuration | Functions                                       | Number      | Time (ns)          | PDIP      | SOJ | Page |

| 256K x 1      | CE only                                         | MT5C2561    | 10, 12, 15, 20, 25 | 24        | 24  | 1-1  |

| 1 Meg x 1     | CE only                                         | MT5C1001    | 12, 15, 20, 25     | 28        | 28  | 1-11 |

| 64K x 4       | CE only                                         | MT5C2564    | 10, 12, 15, 20, 25 | 24        | 24  | 1-21 |

| 64K x 4       | CE and OE                                       | MT5C2565    | 10, 12, 15, 20, 25 | 28        | 28  | 1-31 |

| 256K x 4      | CE and OE                                       | MT5C1005    | 12, 15, 20, 25     | 28        | 28  | 1-41 |

| 256K x 4      | CE, OE and<br>Revolutionary Pinout              | MT5C256K4A1 | 12, 15, 20, 25     | -         | 32  | 1-51 |

| 32K x 8       | CE and OE                                       | MT5C2568    | 10, 12, 15, 20, 25 | 28        | 28  | 1-61 |

| 128K x 8      | CE1, CE2 and OE                                 | MT5C1008    | 12, 15, 20, 25     | 32        | 32  | 1-71 |

| 128K x 8      | CE, OE and<br>Revolutionary Pinout              | MT5C128K8A1 | 12, 15, 20, 25     | -         | 32  | 1-81 |

| 64K x 16      | CE, OE, Byte Enable and<br>Revolutionary Pinout | MT5C64K16A1 | 12, 15, 20, 25     | -         | 44  | 1-91 |

**NOTE:** 1. Many Micron components are available in bare die form. Contact Micron Semiconductor, Inc., for more information.

## 3.3V ASYNCHRONOUS SRAM PRODUCT SELECTION GUIDE

| Memory        | Control                                         | Part          | Access             | Package/N      | lo. of Pins |       |

|---------------|-------------------------------------------------|---------------|--------------------|----------------|-------------|-------|

| Configuration | Functions                                       | Number        | Time (ns)          | PDIP           | SOJ         | Page  |

| 256K x 1      | CE only with separate I/O                       | MT5LC2561     | 12, 15, 20, 25     | 24             | 24          | 2-1   |

| 1 Meg x 1     | CE only with separate I/O                       | MT5LC1001     | 15, 17, 20, 25     | 28             | 28          | 2-9   |

| 64K x 4       | CE only                                         | MT5LC2564     | 12, 15, 20, 25     | 24             | 24          | 2-17  |

| 64K x 4       | CE and OE                                       | MT5LC2565     | 12, 15, 20, 25     | 28             | 28          | 2-25  |

| 256K x 4      | CE and OE                                       | MT5LC1005     | 15, 17, 20, 25     | 28             | 28          | 2-33  |

| 256K x 4      | CE, OE and<br>Revolutionary Pinout              | MT5LC256K4D4  | 12, 15, 20, 25     | -              | 32          | 2-41  |

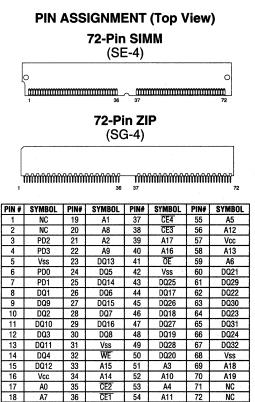

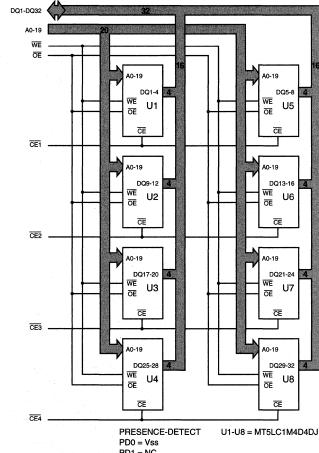

| 1 Meg x 4     | CE, OE and<br>Revolutionary Pinout              | MT5LC1M4D4    | 12, 15, 20, 25, 35 | -              | 32          | 2-51  |

| 32K x 8       | CE and OE                                       | MT5LC2568     | 12, 15, 20, 25     | 28             | 28          | 2-59  |

| 128K x 8      | CE1, CE2 and OE                                 | MT5LC1008     | 15, 17, 20, 25     | 32             | 32          | 2-67  |

| 128K x 8      | CE, OE and<br>Revolutionary Pinout              | MT5LC128K8D4  | 12, 15, 20, 25     | -              | 32          | 2-75  |

| 512K x 8      | CE, OE and<br>Revolutionary Pinout              | MT5LC512K8D4  | 12, 15, 20, 25, 35 | -              | 36          | 2-85  |

| 64K x 16      | CE, OE, Byte Enable<br>and Revolutionary Pinout | MT5LC64K16D4  | 12, 15, 20, 25     | -              | 44          | 2-93  |

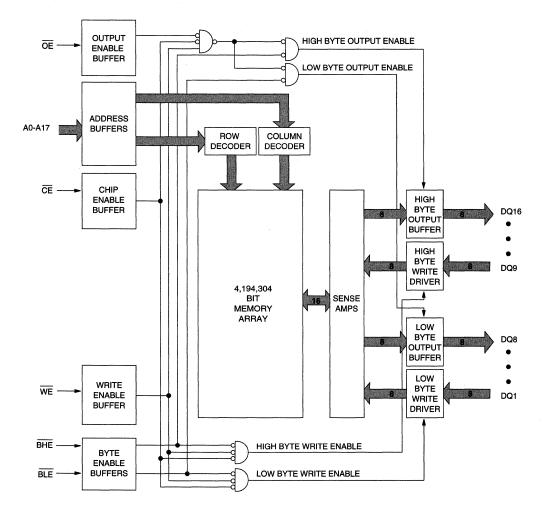

| 256K x 16     | CE, OE, Byte Enable                             | MT5LC256K16D4 | 12, 15, 20, 25, 35 | - 1 - 1<br>- 1 | 54          | 2-103 |

**NOTE:** 1. Many Micron components are available in bare die form. Contact Micron Semiconductor, Inc., for more information.

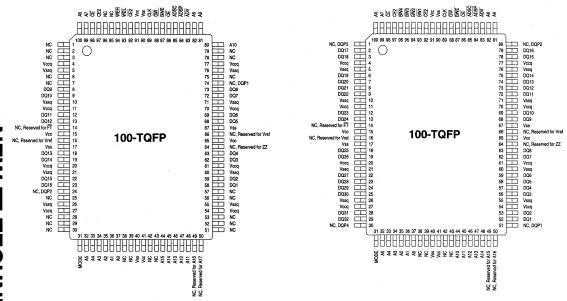

## SYNCHRONOUS SRAM PRODUCT SELECTION GUIDE

| Memory        | Supply  | Control                                    | Part          | Access        | Cycle          | Package | and Numb | er of Pins |      |

|---------------|---------|--------------------------------------------|---------------|---------------|----------------|---------|----------|------------|------|

| Configuration | Voltage | Functions                                  | Number        | Time (ns)     | Time (ns)      | PLCC    | TQFP     | DIE        | Page |

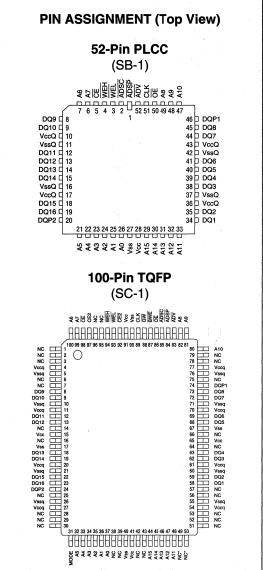

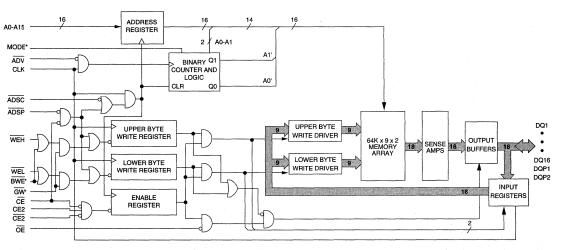

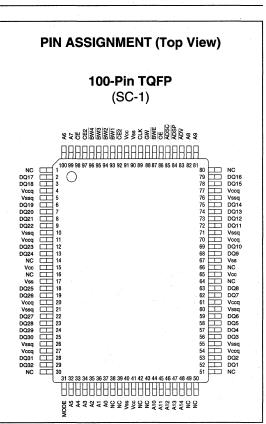

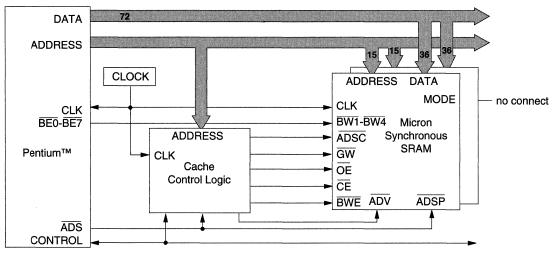

| 64K x 18      | 3.3V    | SyncBurst™, Interleaved, Linear            | MT58LC64K18B2 | 9,10,11,12,14 | 15,15,15,20,20 | 52      | 100      | CD1/CD2    | 3-1  |

| 64K x 18      | 3.3V    | SyncBurst, Linear                          | MT58LC64K18M1 | 9,10,11,12,14 | 15,15,15,20,20 | 52      | 100      | CD1/CD2    | 3-1  |

| 64K x 18      | 3.3V    | SyncBurst, Interleaved, Linear             | MT58LC64K18C4 | 4.5,5,6,7,8   | 8,10,12,15,20  | 52      | 100      | CD1/CD2    | 3-17 |

| 64K x 18      | 3.3V    | SyncBurst, Linear                          | MT58LC64K18A6 | 4.5,5,6,7,8   | 8,10,12,15,20  | 52      | 100      | CD1/CD2    | 3-17 |

| 32K x 32      | 3.3V    | SyncBurst                                  | MT58LC32K32B2 | 9,10,11,12,14 | 15,15,15,20,20 | -       | 100      | CD1/CD2    | 3-33 |

| 32K x 32      | 3.3V    | SyncBurst, Interleaved Burst,<br>Pipelined | MT58LC32K32C4 | 4.5,5,6,7,8   | 8,10,12,15,20  | •       | 100      | CD1/CD2    | 3-49 |

| 32K x 36      | 3.3V    | SyncBurst, Interleaved Burst               | MT58LC32K36B2 | 9,10,11,12,14 | 15,15,15,20,20 | -       | 100      | CD1/CD2    | 3-65 |

| 32K x 36      | 3.3V    | SyncBurst, Interleaved Burst,<br>Pipelined | MT58LC32K36C4 | 4.5,5,6,7,8   | 8,10,12,15,20  | -       | 100      | CD1/CD2    | 3-81 |

NOTE: 1. Many Micron components are available in bare die form. Contact Micron Semiconductor, Inc., for more information.

## PREFACE PRODUCT SELECTION

## SRAM MODULE PRODUCT SELECTION GUIDE

| Memory        | Control                                            | Part          | Access         | Packa | ge and No | . of Pins | l de la secondada<br>Maria de la secondada |

|---------------|----------------------------------------------------|---------------|----------------|-------|-----------|-----------|--------------------------------------------|

| Configuration | Functions                                          | Number        | Time (ns)      | ZIP   | SIMM      | DIMM      | Page                                       |

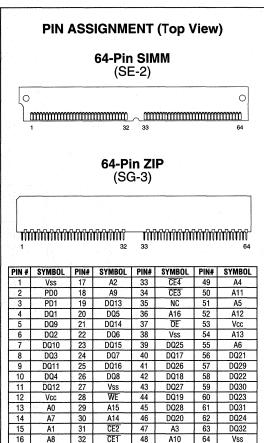

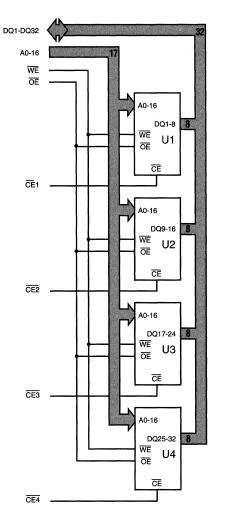

| 64K x 32      | CE and OE                                          | MT8S6432      | 12, 15, 20, 25 | 64    | 64        | -         | 4-1                                        |

| 64K x 32      | CE and OE                                          | MT8LS6432     | 15, 20, 25     | 64    | 64        | -         | 4-9                                        |

| 128K x 32     | CE and OE                                          | MT4S12832     | 15, 20, 25     | 64    | 64        | -         | 4-17                                       |

| 128K x 32     | CE and OE                                          | MT4LS12832    | 17, 20, 25     | 64    | 64        |           | 4-25                                       |

| 256K x 32     | CE and OE                                          | MT8S25632     | 15, 20, 25     | 64    | 64        | -         | 4-33                                       |

| 256K x 32     | CE and OE                                          | MT8LS25632    | 17, 20, 25     | 64    | 64        |           | 4-41                                       |

| 1 Meg x 32    | CE and OE                                          | MT8LS132      | 15, 20, 25, 35 | 72    | 72        | -         | 4-49                                       |

| 32K x 64      | SyncBurst™, Linear Burst                           | MT2LSYT3264T1 | 9, 10, 11, 12  |       |           | 160       | 4-57                                       |

| 32K x 64      | SyncBurst, Interleaved Burst                       | MT2LSYT3264T2 | 9, 10, 11, 12  | -     | -         | 160       | 4-57                                       |

| 32K x 64      | SyncBurst, Interleaved Burst,<br>Pipelined         | MT2LSYT3264T4 | 5, 6, 7, 8     | -     | -         | 160       | 4-69                                       |

| 32K x 64      | SyncBurst, Linear Burst,<br>Pipelined              | MT2LSYT3264T6 | 5, 6, 7, 8     | -     | -         | 160       | 4-69                                       |

| 32K x 64      | SyncBurst,<br>Linear/Interleaved Burst             | MT2LSYT3264B2 | 9, 10, 11, 12  | -     | -         | 160       | 4-81                                       |

| 32K x 64      | SyncBurst, Linear/<br>Interleaved Burst, Pipelined | MT2LSYT3264C4 | 5, 6, 7, 8     |       | -         | 160       | 4-87                                       |

| 32K x 72      | SyncBurst, Linear Burst                            | MT2LSYT3272T1 | 9, 10, 11, 12  | -     | - • •     | 160       | 4-93                                       |

| 32K x 72      | SyncBurst, Interleaved Burst                       | MT2LSYT3272T2 | 9, 10, 11, 12  | - 1   | -         | 160       | 4-93                                       |

| 32K x 72      | SyncBurst, Interleaved Burst,<br>Pipelined         | MT2LSYT3272T4 | 5, 6, 7, 8     | -     | -         | 160       | 4-107                                      |

| 32K x 72      | SyncBurst, Linear Burst,<br>Pipelined              | MT2LSYT3272T6 | 5, 6, 7, 8     | -     | -         | 160       | 4-107                                      |

| 32K x 72      | SyncBurst, Linear/<br>Interleaved Burst            | MT2LSYT3272B2 | 9, 10, 11, 12  | -     | -         | 160       | 4-12                                       |

| 32K x 72      | SyncBurst, Linear/<br>Interleaved Burst, Pipelined | MT2LSYT3272C4 | 5, 6, 7, 8     | -     | -         | 160       | 4-129                                      |

| 64K x 72      | SyncBurst, Linear Burst                            | MT4LSY6472T1  | 9, 10, 11, 12  | ·     | -         | 160       | 4-93                                       |

| 64K x 72      | SyncBurst, Interleaved Burst                       | MT4LSY6472T2  | 9, 10, 11, 12  |       | -         | 160       | 4-93                                       |

| 64K x 72      | SyncBurst, Interleaved Burst,<br>Pipelined         | MT4LSY6472T4  | 5, 6, 7, 8     | -     |           | 160       | 4-107                                      |

| 64K x 72      | SyncBurst, Linear Burst,<br>Pipelined              | MT4LSY6472T6  | 5, 6, 7, 8     | -     | -         | 160       | 4-107                                      |

| 64K x 72      | SyncBurst, Linear/<br>Interleaved Burst            | MT4LSYT6472B2 | 9, 10, 11, 12  | -     | -         | 160       | 4-12                                       |

| 64K x 72      | SyncBurst, Linear/<br>Interleaved Burst, Pipelined | MT4LSYT6472C4 | 5, 6, 7, 8     | -     |           | 160       | 4-129                                      |

## **TECHNICAL NOTE SELECTION GUIDE**

| Technical Note | Title                                                         | Page |

|----------------|---------------------------------------------------------------|------|

| TN-00-01       | Moisture Absorption in Plastic Packages                       | 5-1  |

| TN-00-02       | Tape-and-Reel Procedures                                      | 5-3  |

| TN-05-02       | SRAM Bus Contention Design Considerations                     | 5-9  |

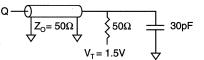

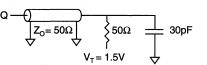

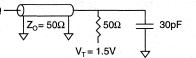

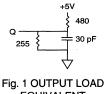

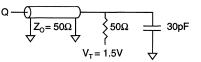

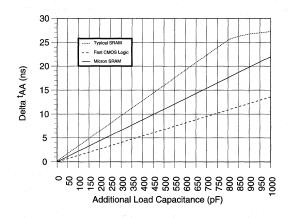

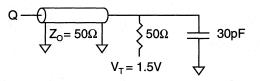

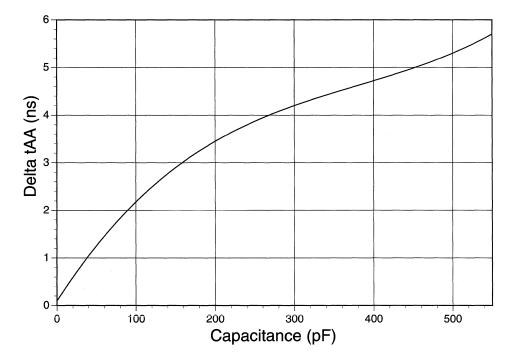

| TN-05-03       | 5V SRAM Capacitive Loading                                    | 5-13 |

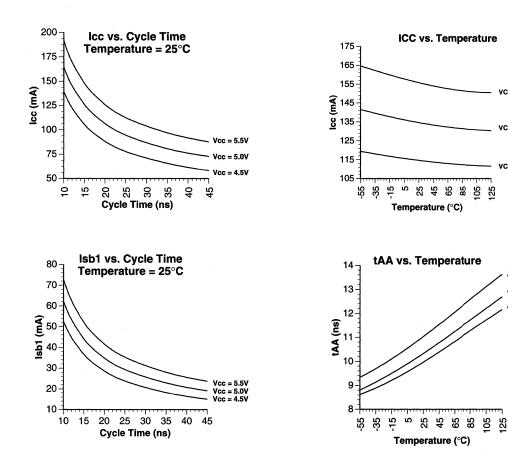

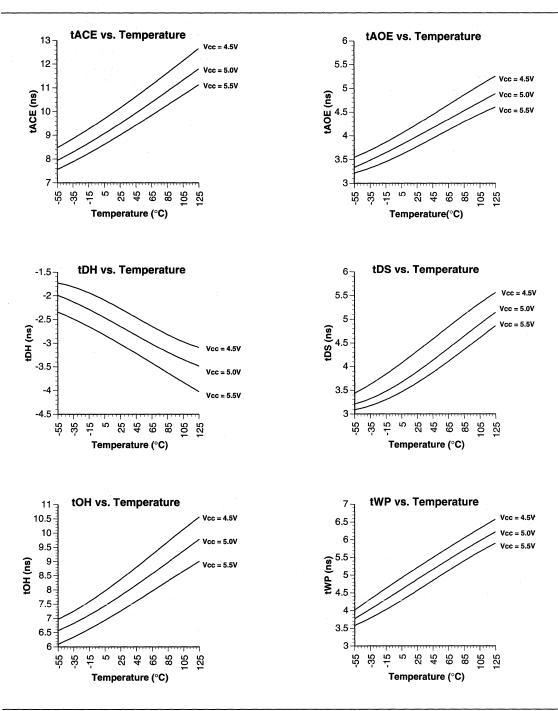

| TN-05-06       | 1 Meg Evolutionary Pinout SRAM Typical (5V) Operating Curves  | 5-15 |

| TN-05-07       | 256K SRAM Typical (5V) Operating Curves                       | 5-17 |

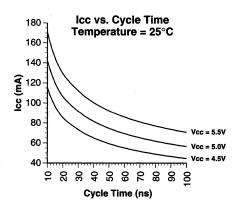

| TN-05-13       | 1 Meg Low-Power SRAMs                                         | 5-19 |

| TN-05-14       | SRAM Thermal Design Considerations                            | 5-23 |

| TN-05-16       | A Designer's Guide to 3.3V SRAMs                              | 5-29 |

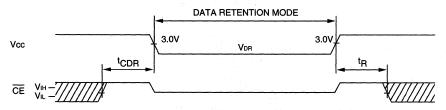

| TN-05-17       | Low-Power Memory Design Using Data Retention                  | 5-35 |

| TN-05-19       | SRAMs and Low-Voltage Data Retention                          | 5-39 |

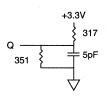

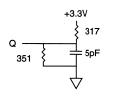

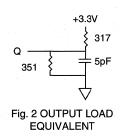

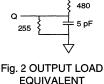

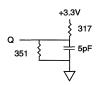

| TN-05-20       | 3.3V SRAM Capacitive Loading                                  | 5-41 |

| TN-05-21       | High-Speed Memory Design Techniques                           | 5-43 |

| TN-05-22       | 1 Meg Revolutionary Pinout SRAM Typical (5V) Operating Curves | 5-49 |

| TN-05-23       | 256K SRAM Typical (3.3V) Operating Curves                     | 5-53 |

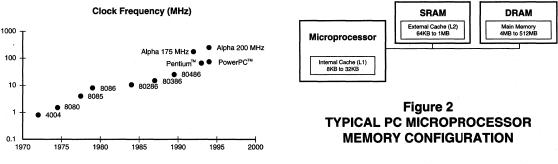

| TN-58-01       | SyncBurst™ SRAM Design for Compatibility                      | 5-55 |

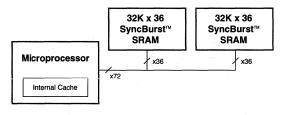

| TN-58-02       | Design Tips: 32K x 36 Synchronous SRAM                        | 5-63 |

| TN-58-03       | SyncBurst™ SRAMs in Asynchronous Designs                      | 5-69 |

## PREFACE PRODUCT SELECTION

MIC

| 5V ASYNCHRONOUS SRAMs   | 1 |

|-------------------------|---|

| 3.3V ASYNCHRONOUS SRAMs | 2 |

| SYNCHRONOUS SRAMs       | 3 |

| SRAM MODULES            | 4 |

| TECHNICAL NOTES         | 5 |

| PRODUCT RELIABILITY     | 6 |

| PACKAGE INFORMATION     | 7 |

| SALES INFORMATION       | 8 |

## **5V ASYNCHRONOUS SRAM PRODUCT SELECTION GUIDE**

| Memory        | Control                                         | Part        | Access             | Package/ | No. of Pins |      |  |

|---------------|-------------------------------------------------|-------------|--------------------|----------|-------------|------|--|

| Configuration | Functions                                       | Number      | Time (ns)          | PDIP     | SOJ         | Page |  |

| 256K x 1      | CE only                                         | MT5C2561    | 10, 12, 15, 20, 25 | 24       | 24          | 1-1  |  |

| 1 Meg x 1     | CE only                                         | MT5C1001    | 12, 15, 20, 25     | 28       | 28          | 1-11 |  |

| 64K x 4       | CE only                                         | MT5C2564    | 10, 12, 15, 20, 25 | 24       | 24          | 1-21 |  |

| 64K x 4       | $\overline{CE}$ and $\overline{OE}$             | MT5C2565    | 10, 12, 15, 20, 25 | 28       | 28          | 1-31 |  |

| 256K x 4      | $\overline{CE}$ and $\overline{OE}$             | MT5C1005    | 12, 15, 20, 25     | 28       | 28          | 1-41 |  |

| 256K x 4      | CE, OE and<br>Revolutionary Pinout              | MT5C256K4A1 | 12, 15, 20, 25     | -        | 32          | 1-51 |  |

| 32K x 8       | CE and OE                                       | MT5C2568    | 10, 12, 15, 20, 25 | 28       | 28          | 1-61 |  |

| 128K x 8      | CE1, CE2 and OE                                 | MT5C1008    | 12, 15, 20, 25     | 32       | 32          | 1-71 |  |

| 128K x 8      | CE, OE and<br>Revolutionary Pinout              | MT5C128K8A1 | 12, 15, 20, 25     | -        | 32          | 1-81 |  |

| 64K x 16      | CE, OE, Byte Enable and<br>Revolutionary Pinout | MT5C64K16A1 | 12, 15, 20, 25     | -        | 44          | 1-91 |  |

**NOTE:** 1. Many Micron components are available in bare die form. Contact Micron Semiconductor, Inc., for more information.

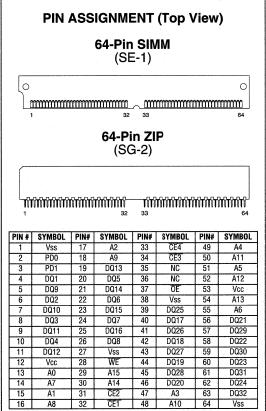

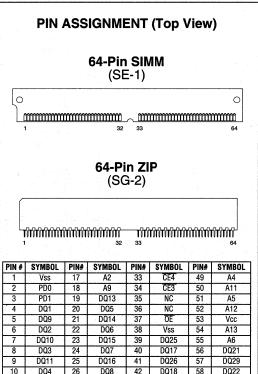

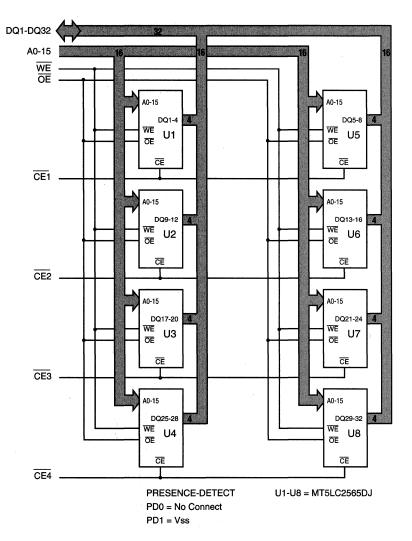

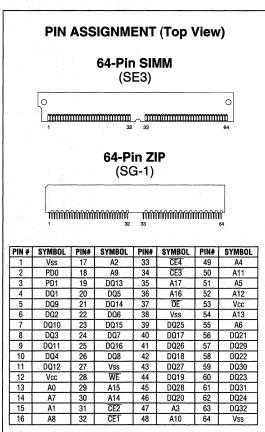

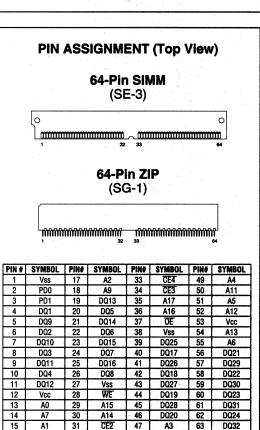

## MT5C2561 256K x 1 SRAM

## 256K x 1 SRAM

14 D D 13 D CE

| FEATURES                                                                                | Г                                      |                                        |

|-----------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|

| <ul> <li>High speed: 10, 12, 15, 20 and</li> <li>High-performance, low-power</li> </ul> |                                        | PIN ASSIGNMENT (Top View)              |

| <ul> <li>process</li> <li>Single +5V ±10% power supp</li> </ul>                         | 1                                      | 24-Pin DIP                             |

| <ul> <li>Easy memory expansion with</li> </ul>                                          |                                        | (SA-3)                                 |

| <ul> <li>All inputs and outputs are TT</li> </ul>                                       |                                        |                                        |

| i in nip un una curp un ure i i                                                         | 2 company                              |                                        |

| OPTIONS                                                                                 | MARKING                                | A1 [] 2 23 [] A17                      |

| Timing                                                                                  |                                        | A2 [] 3 22 [] A16                      |

| 10ns access                                                                             | -10                                    | A3 [] 4 21 [] A15                      |

| 12ns access                                                                             | -12                                    | A4 [] 5 20 ]] A14                      |

| 15ns access                                                                             | -15                                    | A5 [ 6 19 ] A13                        |

| 20ns access                                                                             | -20                                    | A6 [ 7 18 ] A12                        |

| 25ns access                                                                             | -25                                    | A7 [ 8 17 ] A11                        |

|                                                                                         |                                        | A8 [ 9 16 ] A10                        |

| • Packages                                                                              | NT                                     | Q [ 10 15 ] A9                         |

| Plastic DIP (300 mil)                                                                   | None                                   | WE [ 11 14 ] D                         |

| Plastic SOJ (300 mil)                                                                   | DJ                                     | Vss [ 12 13 ] CE                       |

| <ul> <li>2V data retention (optional)</li> </ul>                                        | L                                      |                                        |

| <ul> <li>Low power (optional)</li> </ul>                                                | Р                                      | 24-Pin SOJ                             |

| Temperature                                                                             |                                        | (SD-1)                                 |

| Commercial ( $0^{\circ}$ C to +70°C)                                                    | None                                   |                                        |

| Industrial $(-40^{\circ}\text{C to }+85^{\circ}\text{C})$                               |                                        | A0 [ 1 24 ] Vcc                        |

| Automotive (-40°C to +125°C                                                             |                                        | A1 🛛 2 23 🗅 A17                        |

| Extended (-55°C to +125°C                                                               |                                        | A2 [] 3 22 [] A16<br>A3 [] 4 21 [] A15 |

|                                                                                         |                                        | A4 [] 5 20 [] A14                      |

| Part Number Example: MT50                                                               | .2561DJ-15 P                           | A5 🛛 6 19 🗍 A13                        |

| NOTE: Not all combinations of operating                                                 |                                        | A6 C 7 18 A12                          |

| and low power are necessarily available. Ple                                            | ase contact the factory for availabil- | A7 [] 8 17 [] A11<br>A8 [] 9 16 [] A10 |

| ity of specific part number combinations.                                               |                                        |                                        |

|                                                                                         |                                        | WE 0 11 14 p <u>p</u>                  |

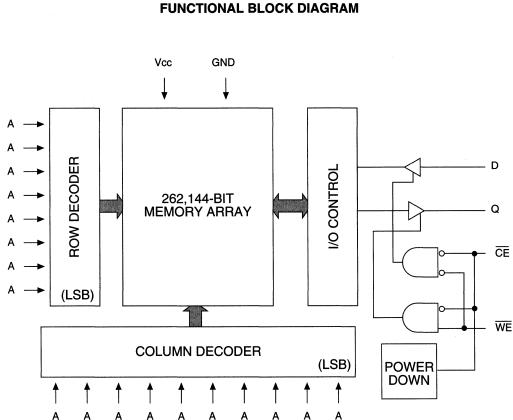

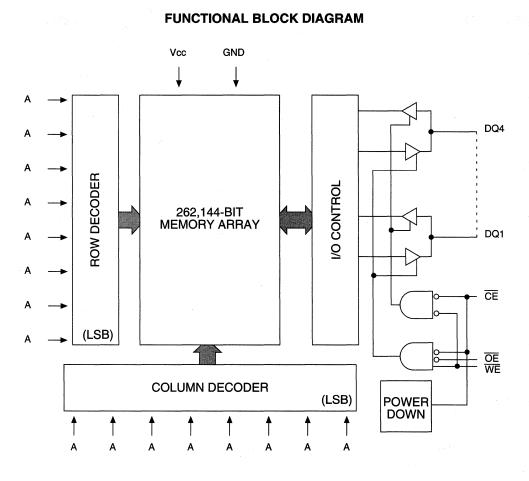

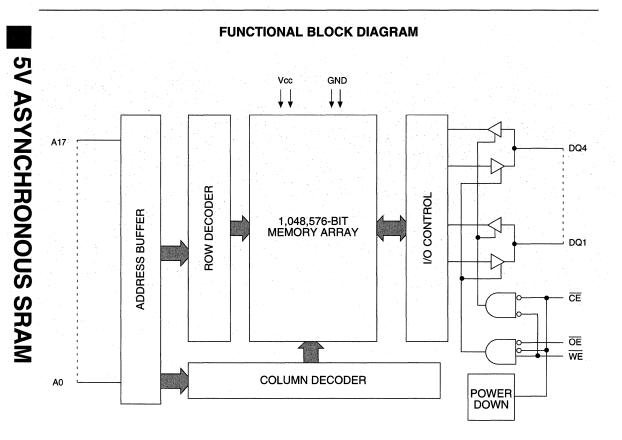

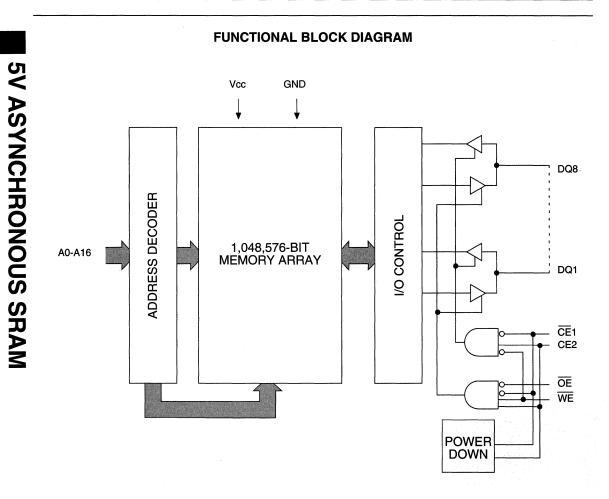

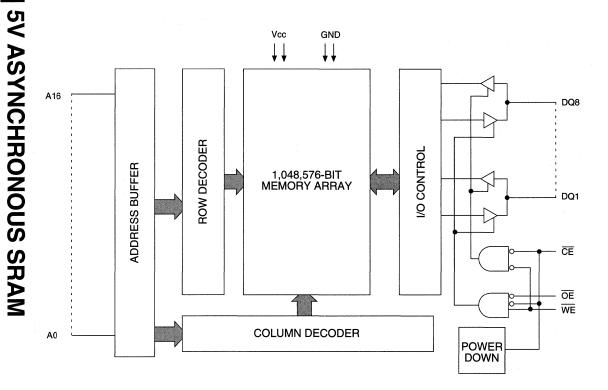

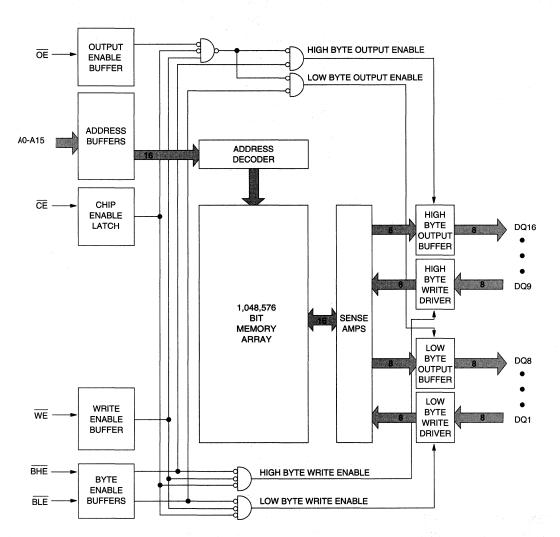

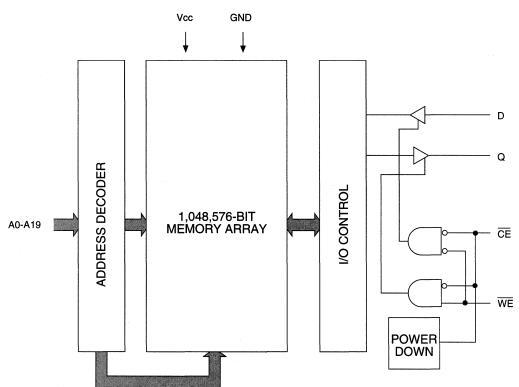

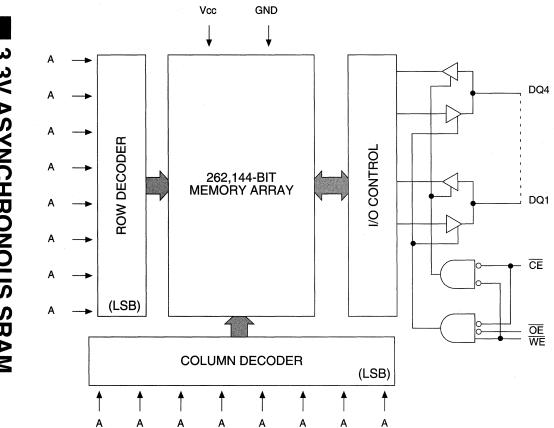

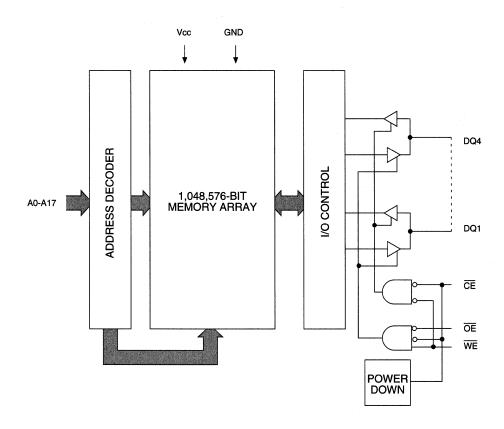

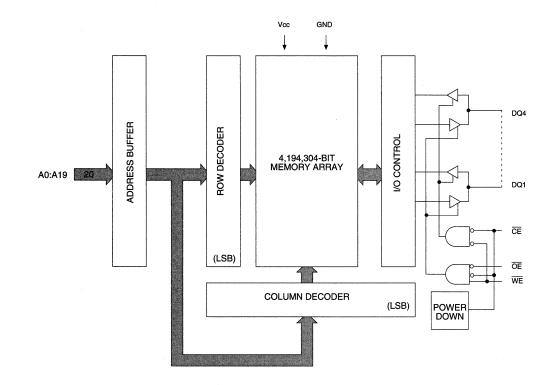

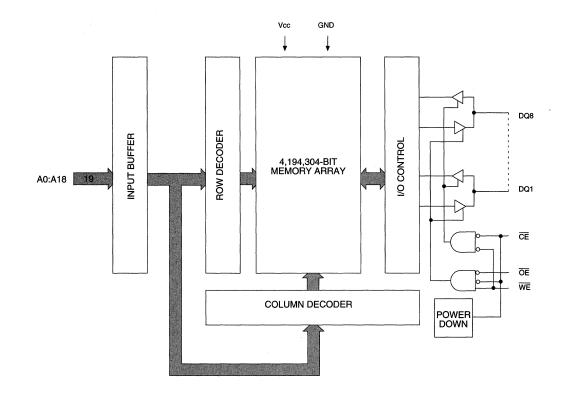

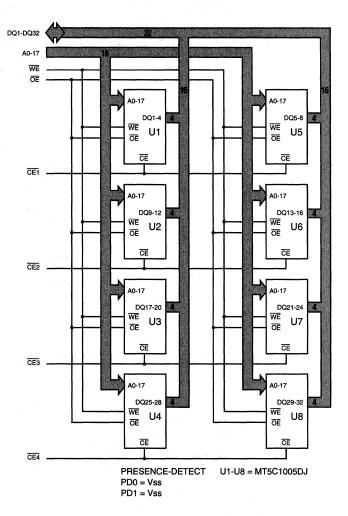

## GENERAL DESCRIPTION

SRAM

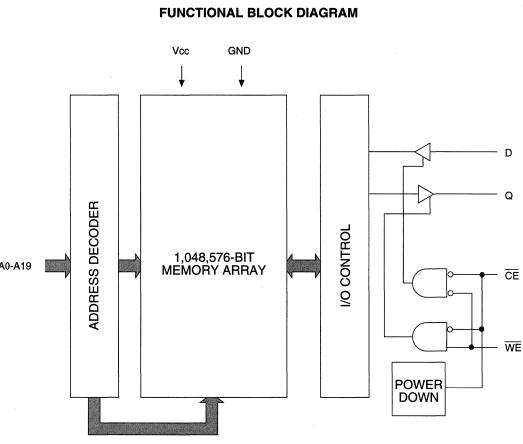

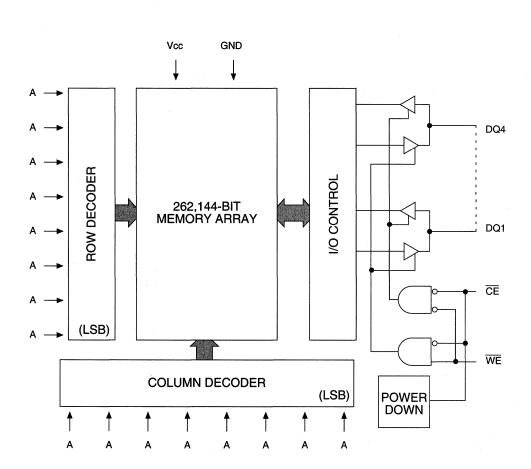

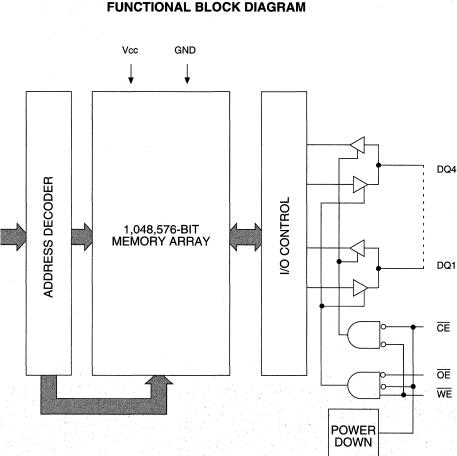

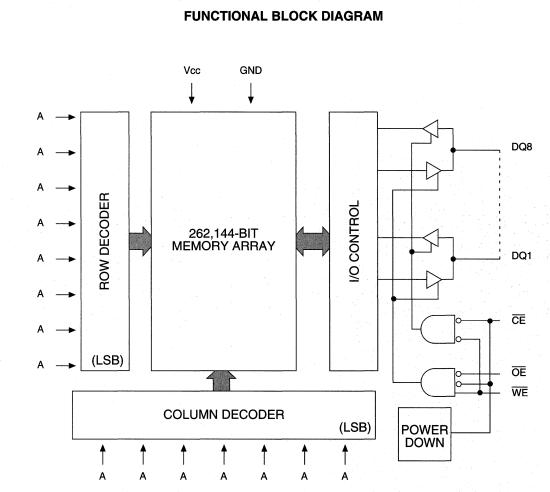

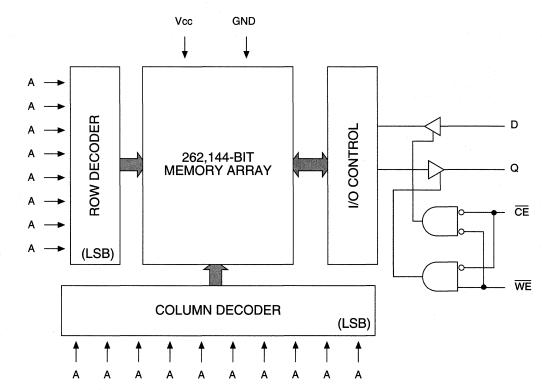

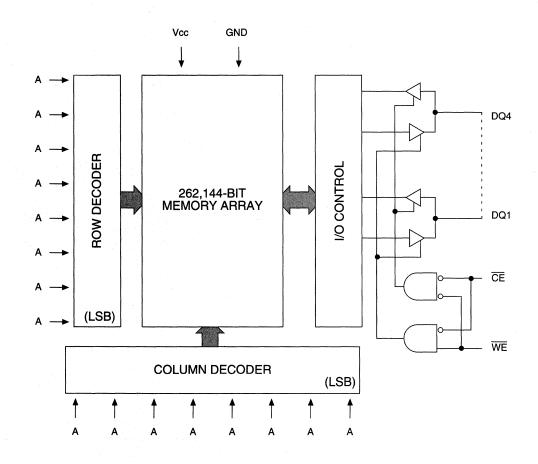

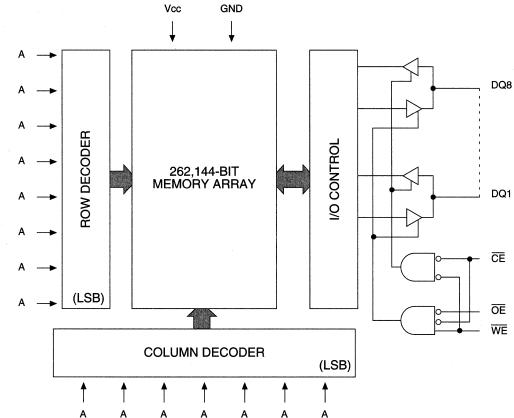

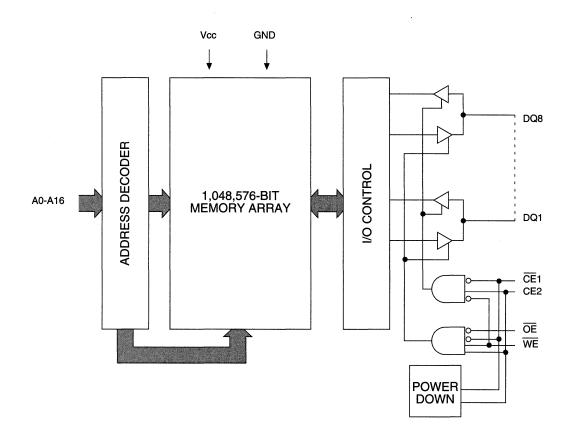

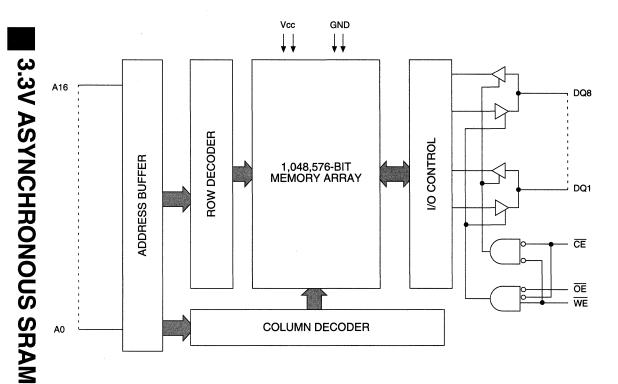

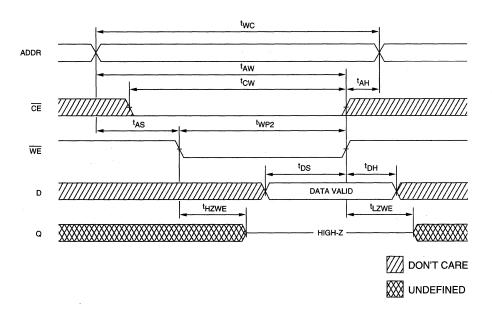

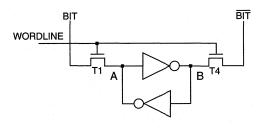

The MT5C2561 is organized as a 262,144 x 1 SRAM using a four-transistor memory cell with a high-speed, low-power CMOS process. Micron SRAMs are fabricated using doublelayer metal, double-layer polysilicon technology.

For flexibility in high-speed memory applications, Micron offers chip enable (CE) with all organizations. This enhancement can place the outputs in High-Z for additional flexibility in system design. The x1 configuration features separate data input and output.

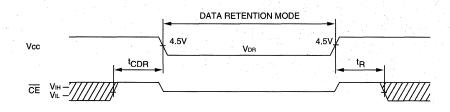

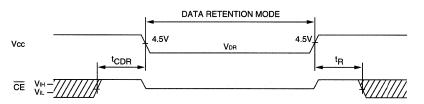

Writing to these devices is accomplished when write enable ( $\overline{WE}$ ) and  $\overline{CE}$  inputs are both LOW. Reading is accomplished when  $\overline{WE}$  remains HIGH and  $\overline{CE}$  goes LOW. The device offers a reduced power standby mode when

disabled. This allows system designers to meet low standby power requirements.

Vss 🕻 12

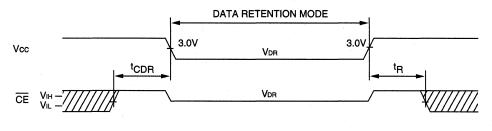

The "P" version provides a reduction in both operating current (Icc) and TTL standby current (ISB1). The latter is achieved through the use of gated inputs on the  $\overline{WE}$  and address lines, which also facilitates the design of battery backed systems. That is, the gated inputs simplify the design effort and circuitry required to protect against inadvertent battery current drain during power-down, when inputs may be at undefined levels.

All devices operate from a single +5V power supply and all inputs and outputs are fully TTL-compatible.

MT5C2561 256K x 1 SRAM

#### **TRUTH TABLE**

| MODE    | CE | WE | INPUT      | OUTPUT | POWER   |

|---------|----|----|------------|--------|---------|

| STANDBY | н  | X  | DON'T CARE | HIGH-Z | STANDBY |

| READ    | L  | Н  | DON'T CARE | Q      | ACTIVE  |

| WRITE   | L  | L  | DATA-IN    | HIGH-Z | ACTIVE  |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on VCC Supply Relative to Vss | 1V to +7V      |

|---------------------------------------|----------------|

| Storage Temperature (plastic)         | 55°C to +150°C |

| Short Circuit Output Current          | 50mA           |

| Voltage on Any Pin Relative to Vss    | 1V to Vcc +1V  |

| Junction Temperature**                | +150°C         |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\*Maximum junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow. See technical note TN-05-14 for more information.

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \le T_{A} \le 70^{\circ}C; Vcc = 5V \pm 10\%)$

| DESCRIPTION                  | CONDITIONS                            | SYMBOL | MIN  | MAX    | UNITS | NOTES |

|------------------------------|---------------------------------------|--------|------|--------|-------|-------|

| Input High (Logic 1) Voltage |                                       | Vін    | 2.2  | Vcc +1 | V     | 1     |

| Input Low (Logic 0) Voltage  |                                       | VIL    | -0.5 | 0.8    | V     | 1, 2  |

| Input Leakage Current        | $0V \le VIN \le VCC$                  | IL:    | -5   | 5      | μA    |       |

| Output Leakage Current       | Output(s) disabled<br>0V ≤ Vou⊤ ≤ Vcc | ILo    | -5   | 5      | μA    |       |

| Output High Voltage          | Іон = -4.0mA                          | Vон    | 2.4  |        | V     | 1     |

| Output Low Voltage           | IoL = 8.0mA                           | Vol    |      | 0.4    | V     | 1     |

| Supply Voltage               |                                       | Vcc    | 4.5  | 5.5    | V     | . 1   |

|                                    |                                                                                                                                                  |        |     | -<br> | · · · ·      | MAX |     |     | ]     |       |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------|--------------|-----|-----|-----|-------|-------|

| DESCRIPTION                        | CONDITIONS                                                                                                                                       | SYMBOL | ТҮР | -10†  | -12†         | -15 | -20 | -25 | UNITS | NOTES |

| Power Supply<br>Current: Operating | CE ≤ VIL; Vcc = MAX<br>f = MAX = 1/ <sup>t</sup> RC<br>outputs open                                                                              | lcc    | 130 | 200   | 180          | 165 | 150 | 140 | mA    | 3, 13 |

|                                    | P version                                                                                                                                        | lcc    | 100 | -     | -            | 140 | 125 | 120 | mA    | 3, 13 |

| Power Supply<br>Current: Standby   | CE ≥ VIH; Vcc = MAX<br>f = MAX = 1/ <sup>t</sup> RC<br>outputs open                                                                              | ISB1   | 24  | 55    | 50           | 45  | 40  | 35  | mA    | 13    |

|                                    | P version                                                                                                                                        | ISB1   | 1.4 | -     | -            | 4   | 4   | 4   | mA    | 13    |

|                                    | $\label{eq:cell} \overline{CE} \geq Vcc \ -0.2V; \ Vcc = MAX \\ V_{IN} \leq Vss \ +0.2V \ or \\ V_{IN} \geq Vcc \ -0.2V; \ f = 0 \\ \end{array}$ | ISB2   | 0.6 | 5     | 5            | 5   | 5   | 5   | mA    | 13    |

|                                    | P version                                                                                                                                        | ISB2   | 0.4 | -     | <sup>-</sup> | 3   | 3   | 3   | mA    | 13    |

<sup>†</sup>P version not available with this speed.

### CAPACITANCE

| DESCRIPTION        | CONDITIONS                       | SYMBOL | MAX | UNITS | NOTES |

|--------------------|----------------------------------|--------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C; f = 1 MHz | Сі     | 6   | pF    | 4     |

| Output Capacitance | Vcc = 5V                         | Co     | 6   | pF    | 4     |

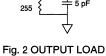

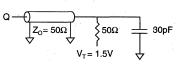

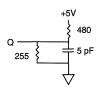

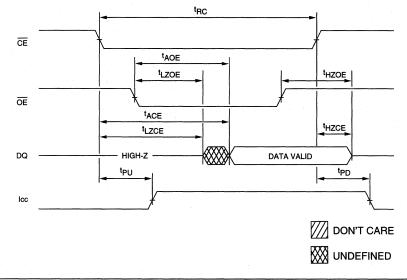

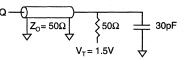

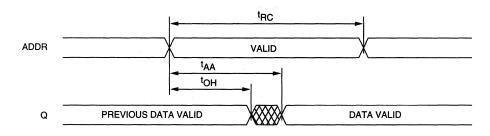

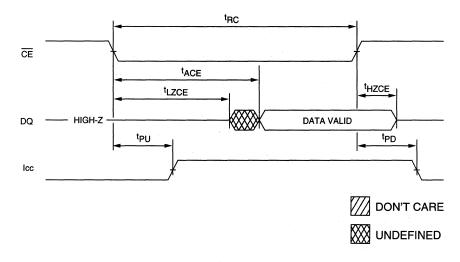

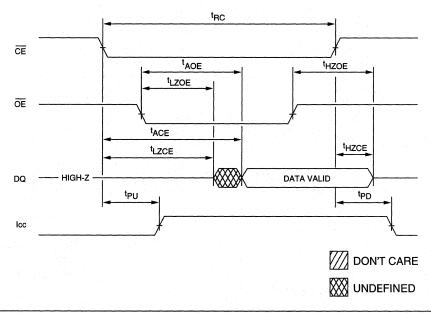

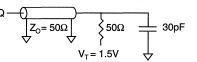

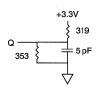

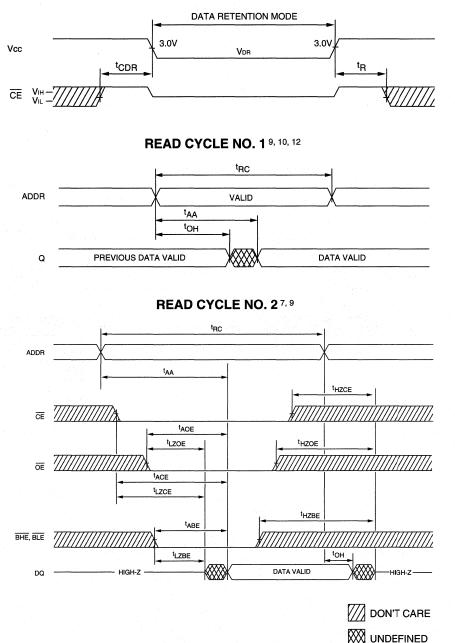

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(Note 5) ( $0^{\circ}C \le T_A \le 70^{\circ}C$ ; Vcc = 5V ±10%)

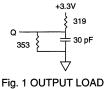

|                                                  | :                 | -10 -12 |     | -15 |     | -20 |     |       | 25  |     |          |       |       |

|--------------------------------------------------|-------------------|---------|-----|-----|-----|-----|-----|-------|-----|-----|----------|-------|-------|

| DESCRIPTION                                      | SYM               | MIN     | MAX | MIN | MAX | MIN | MAX | MIN   | MAX | MIN | MAX      | UNITS | NOTES |

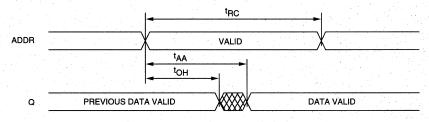

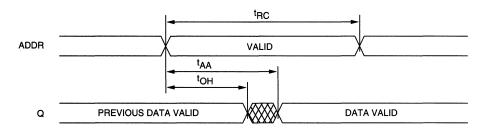

| READ Cycle                                       |                   |         |     |     |     |     |     |       |     |     |          |       |       |

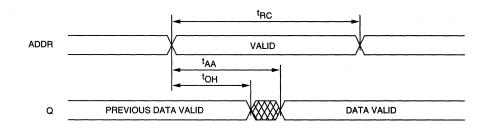

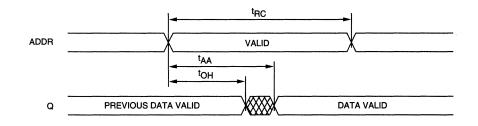

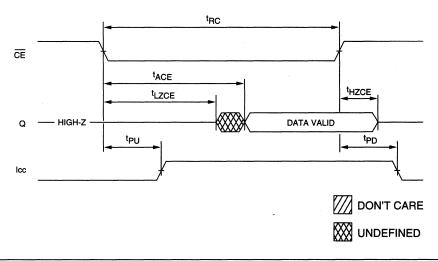

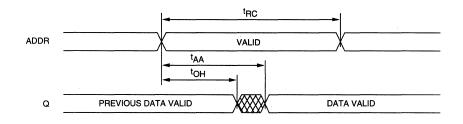

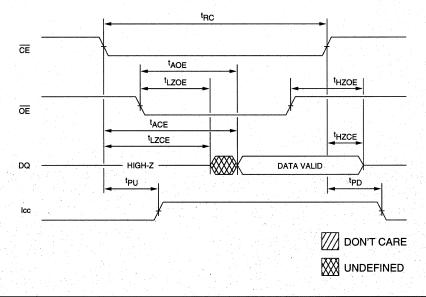

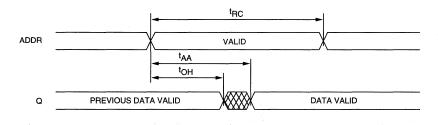

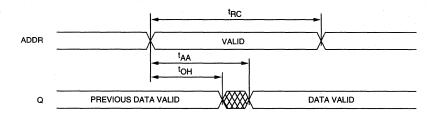

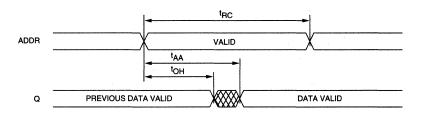

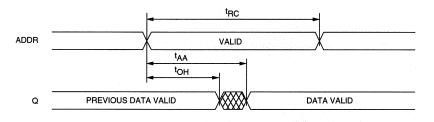

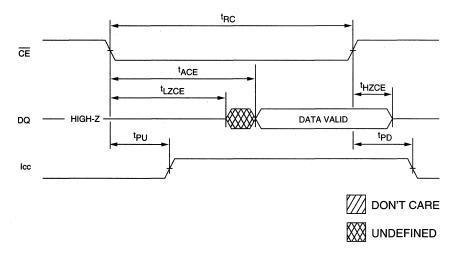

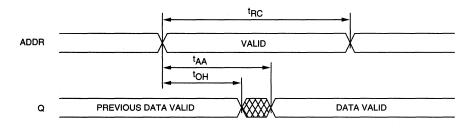

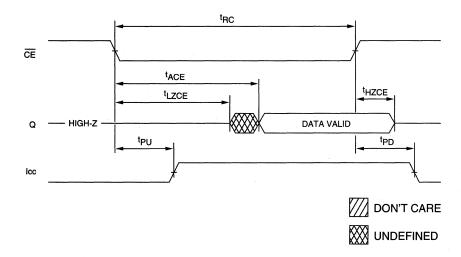

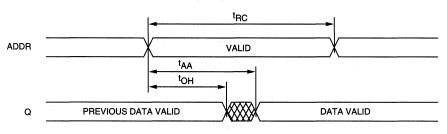

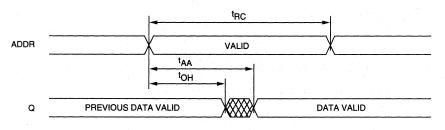

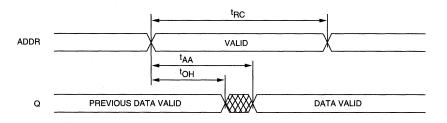

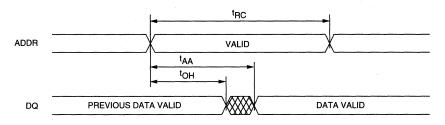

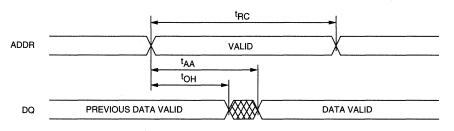

| READ cycle time                                  | <sup>t</sup> RC   | 10      |     | 12  |     | 15  |     | 20    |     | 25  |          | ns    |       |

| Address access time                              | <sup>t</sup> AA   | 1.1     | 10  |     | 12  |     | 15  |       | 20  |     | 25       | ns    |       |

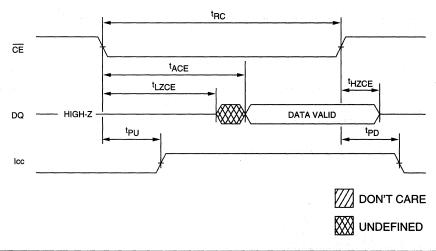

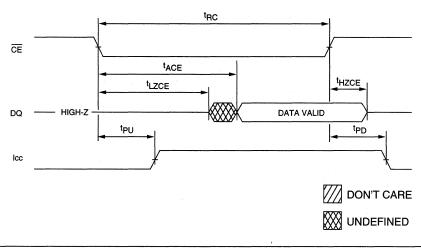

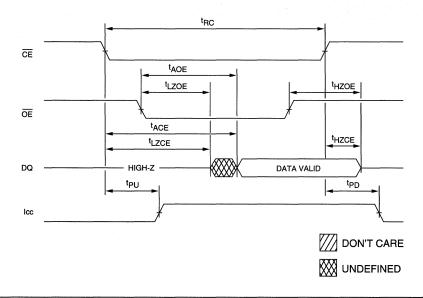

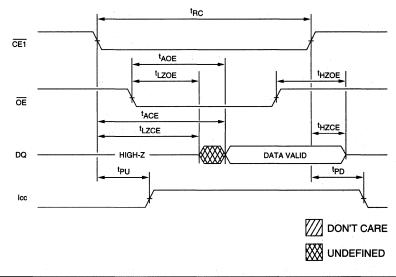

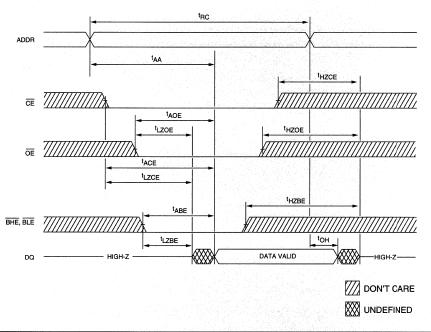

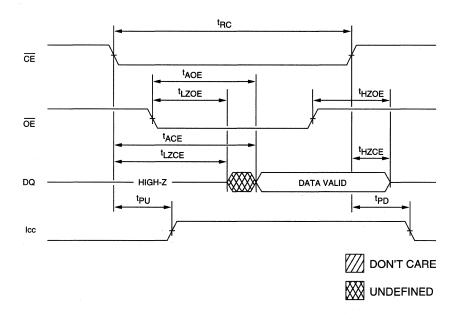

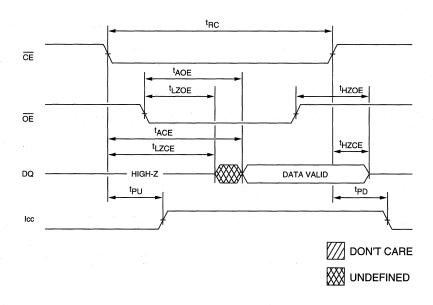

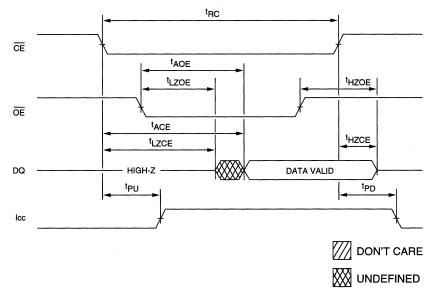

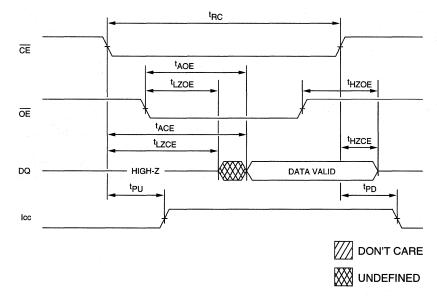

| Chip Enable access time                          | <sup>t</sup> ACE  | 1.1     | 10  |     | 12  |     | 15  |       | 20  |     | 25       | ns    |       |

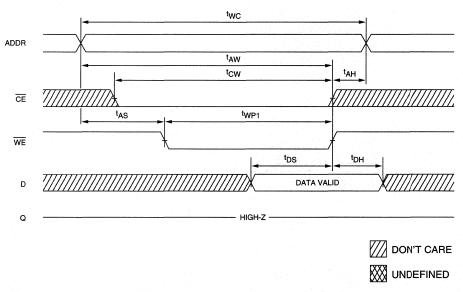

| Output hold from address change                  | tOH               | 3       |     | 3   |     | 3   |     | 3     |     | 3   |          | ns    |       |

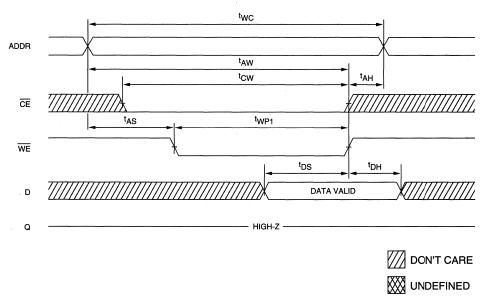

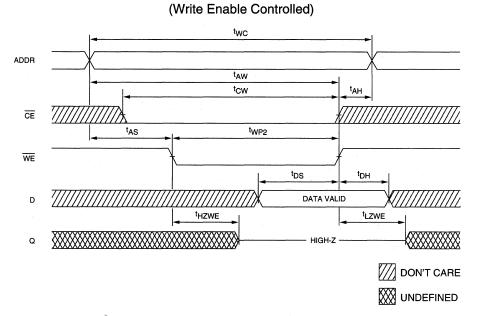

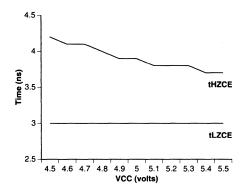

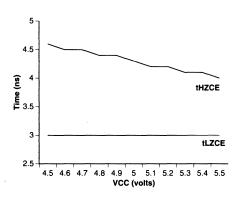

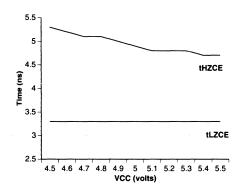

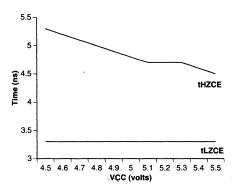

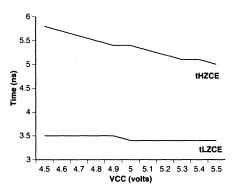

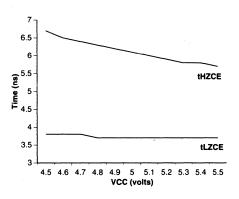

| Chip Enable to output in Low-Z                   | <sup>1</sup> LZCE | 3       |     | 3   |     | 3   |     | 3     |     | 3   |          | ns    | 7     |

| Chip disable to output in High-Z                 | <sup>t</sup> HZCE |         | 5   |     | 6   |     | 8   | 1. T. | 9   |     | 9        | ns    | 6, 7  |

| Chip Enable to power-up time                     | tPU               | 0       |     | 0   |     | 0   |     | 0     |     | 0   |          | ns    | 4     |

| Chip disable to power-down time                  | <sup>t</sup> PD   |         | 10  |     | 12  |     | 15  |       | 20  |     | 25       | ns    | 4     |

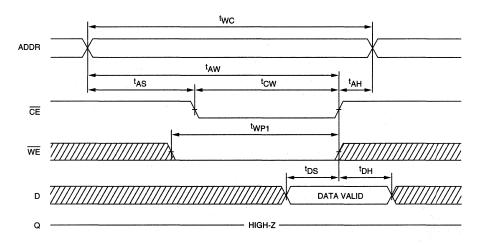

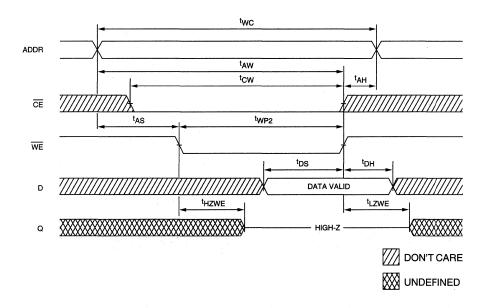

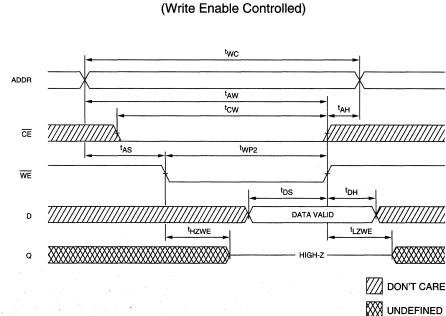

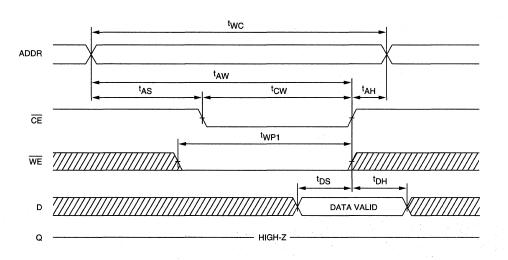

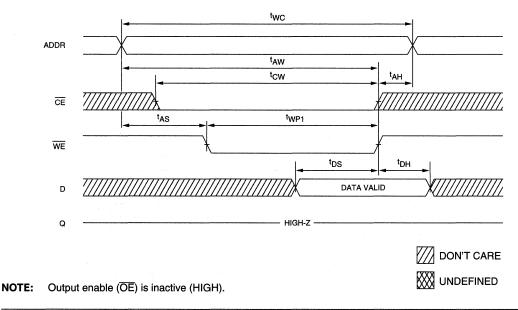

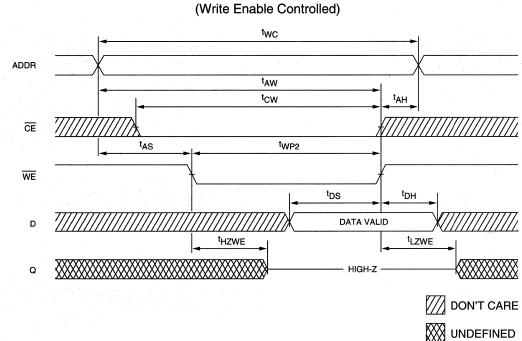

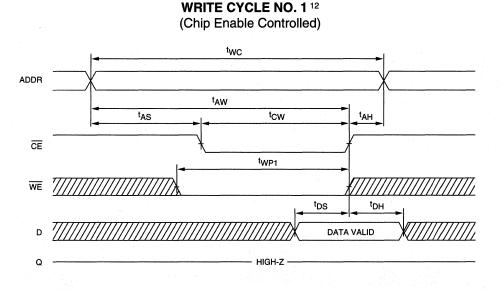

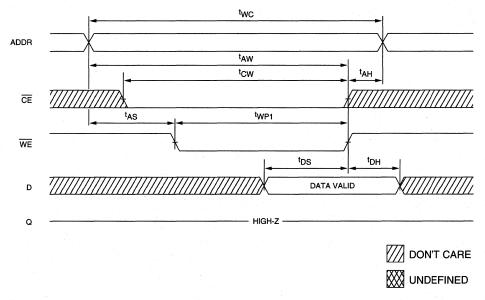

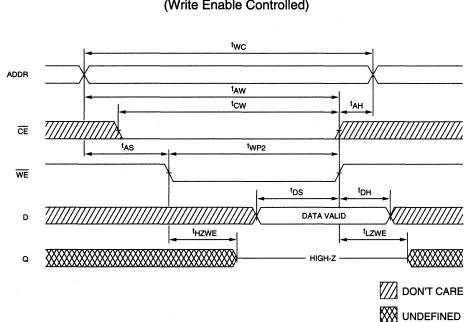

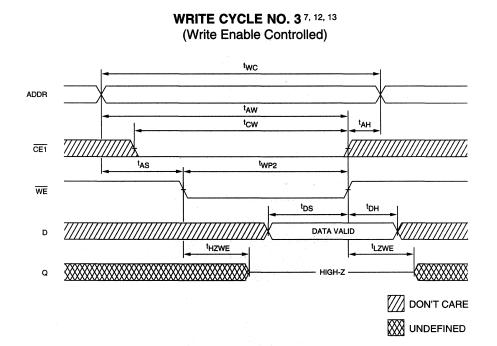

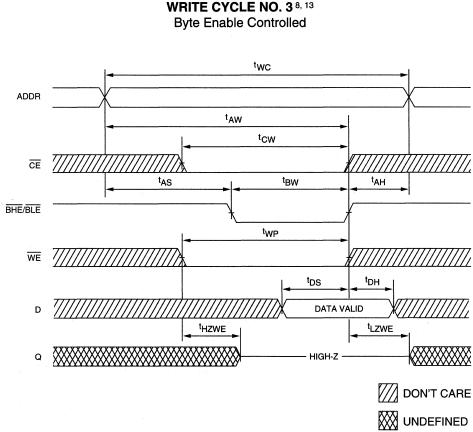

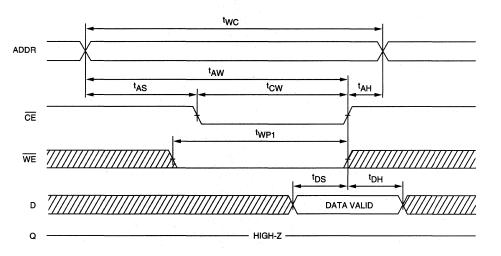

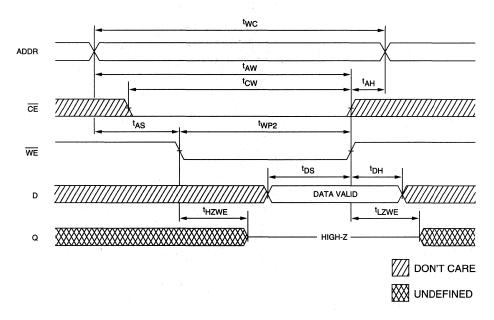

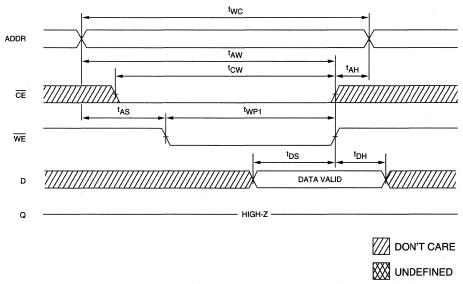

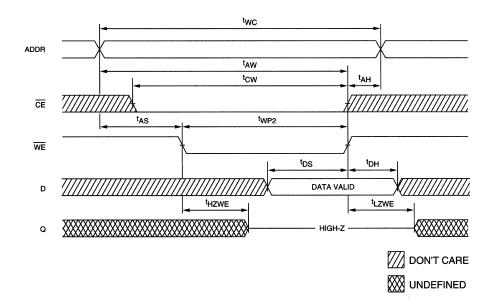

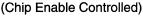

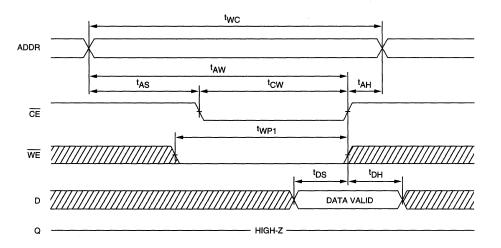

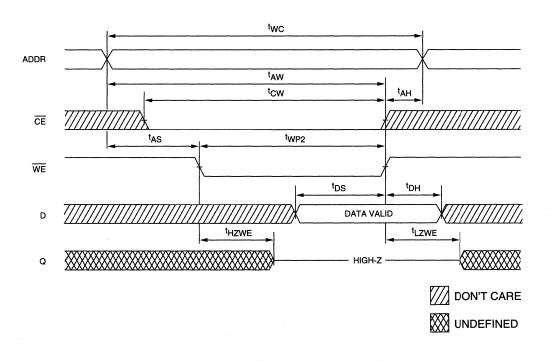

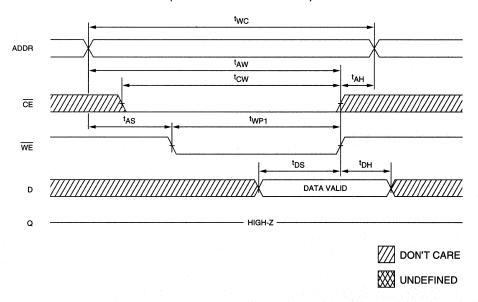

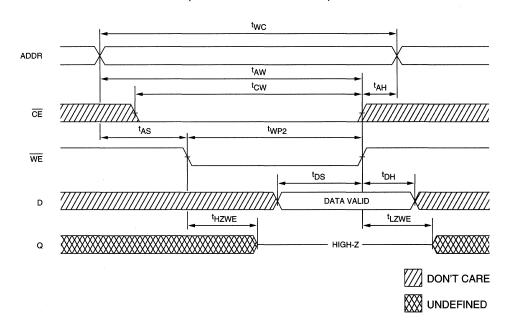

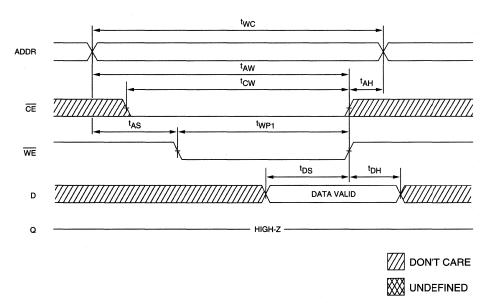

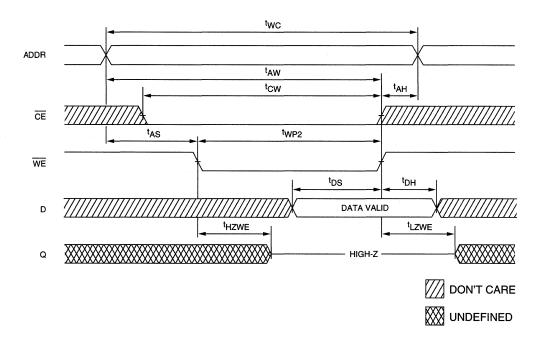

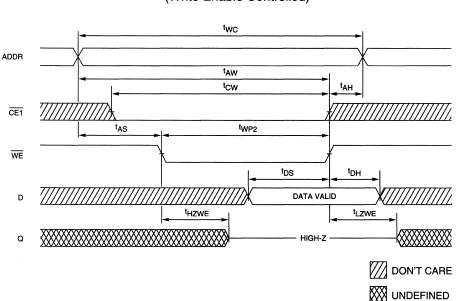

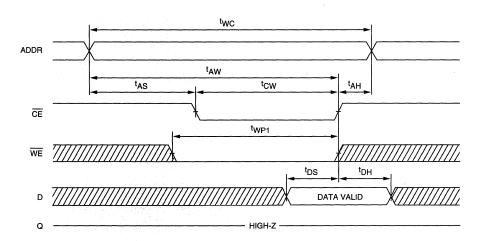

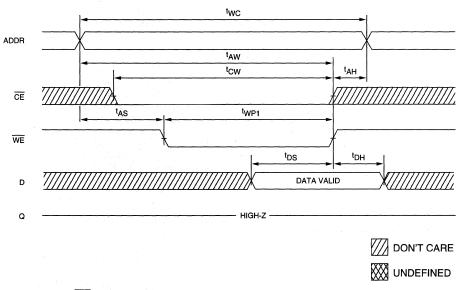

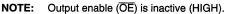

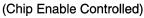

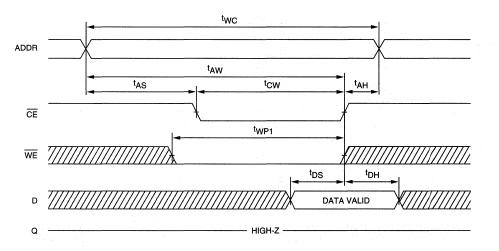

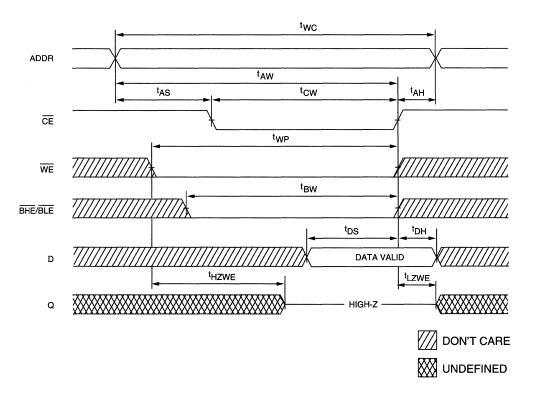

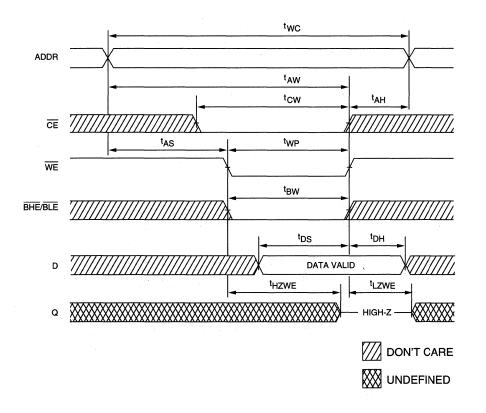

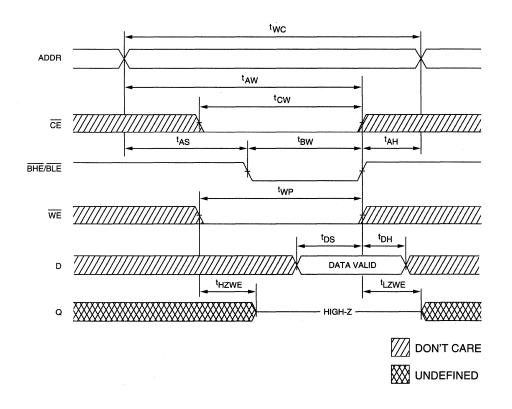

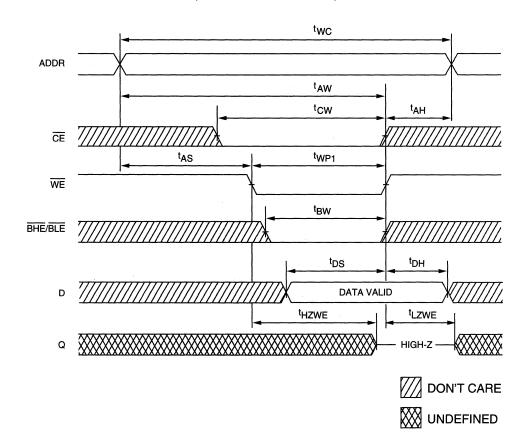

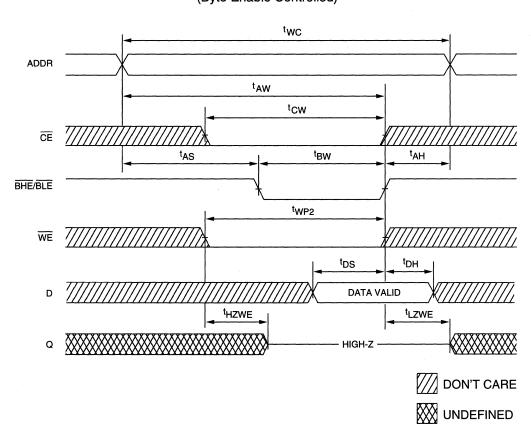

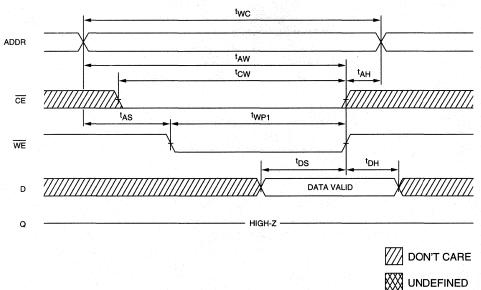

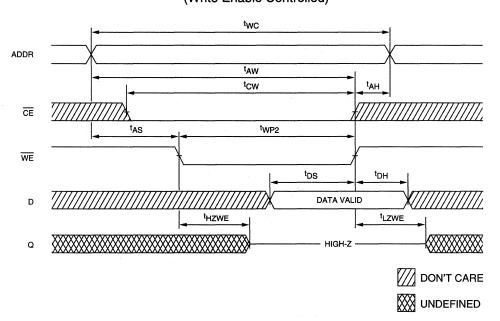

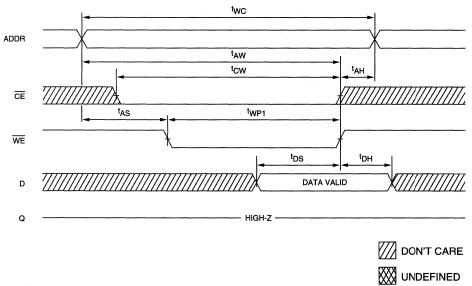

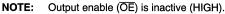

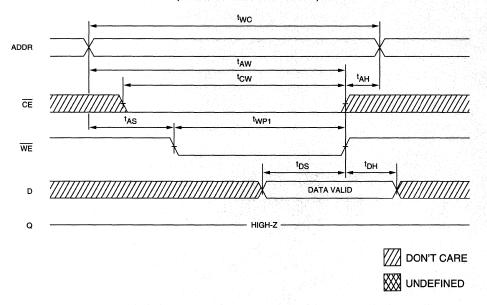

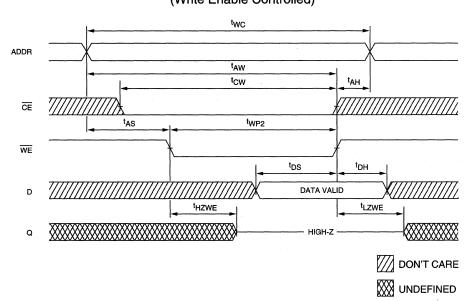

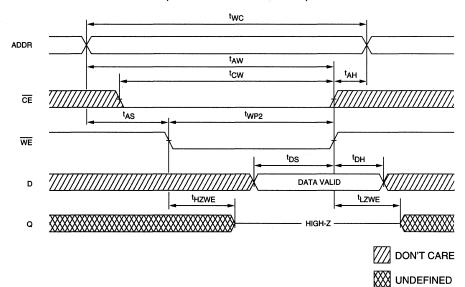

| WRITE Cycle                                      |                   |         |     |     |     |     |     |       |     |     |          |       |       |

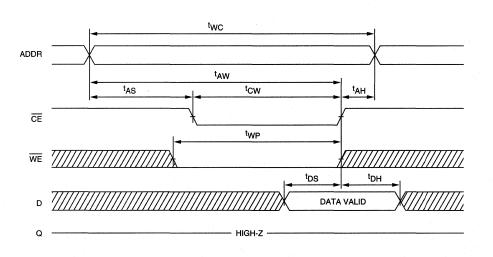

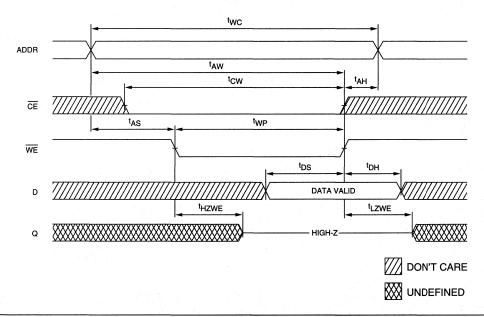

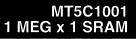

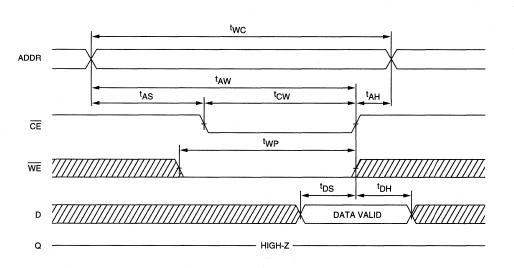

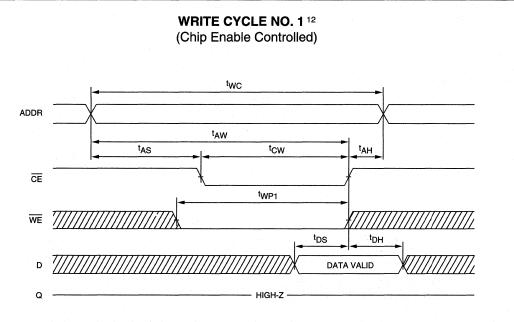

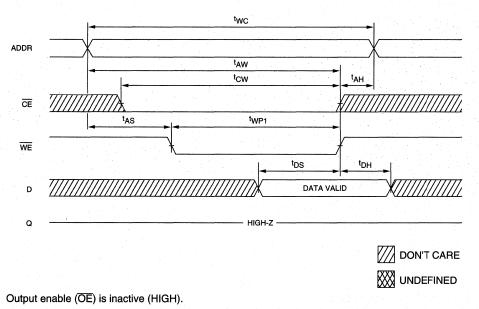

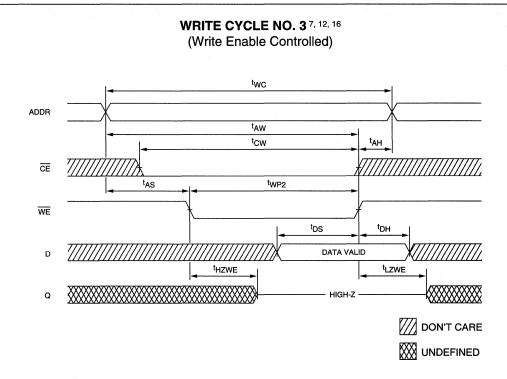

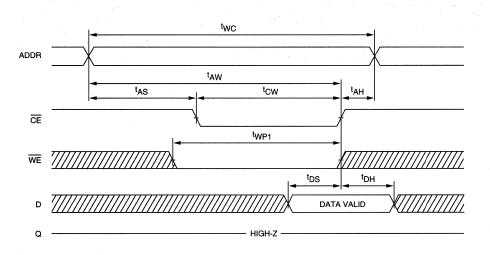

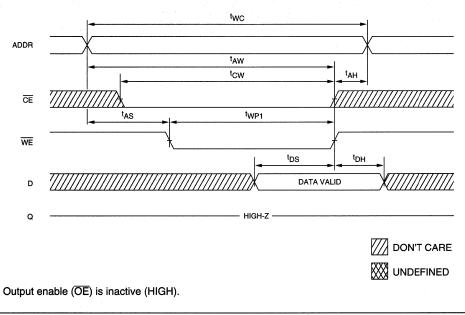

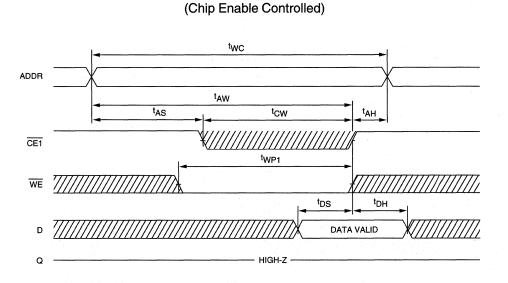

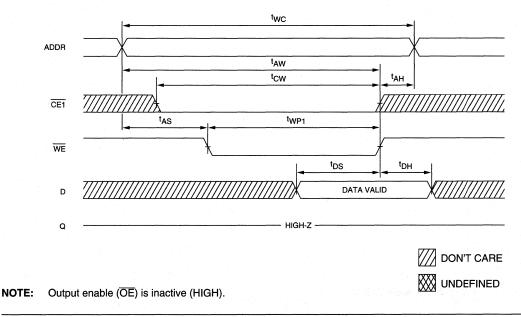

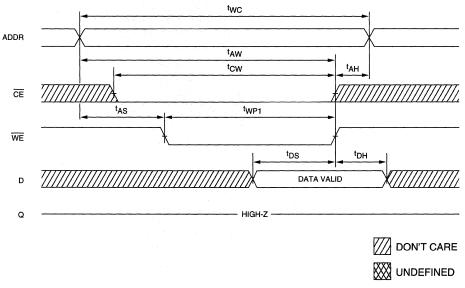

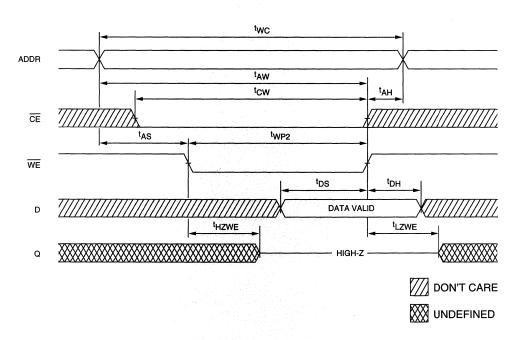

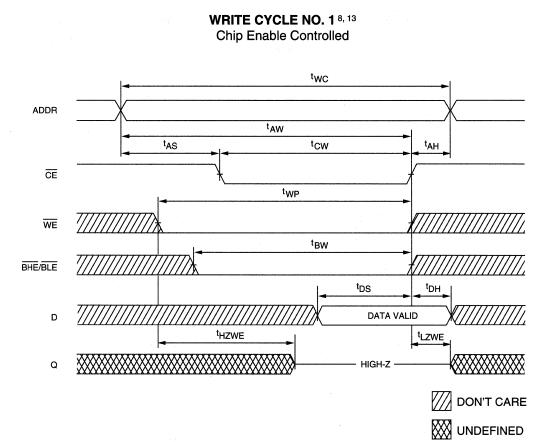

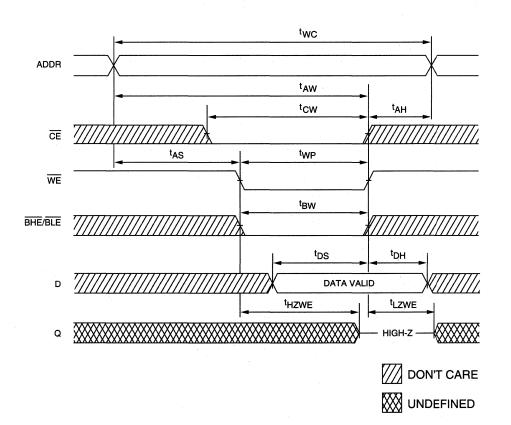

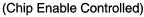

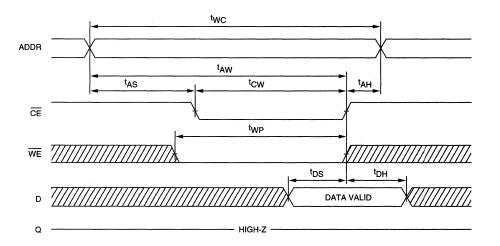

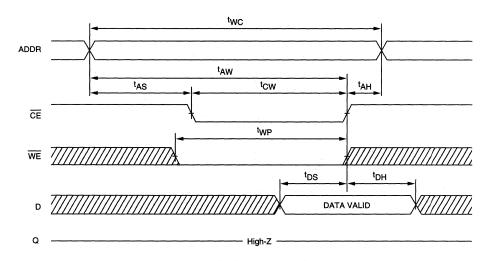

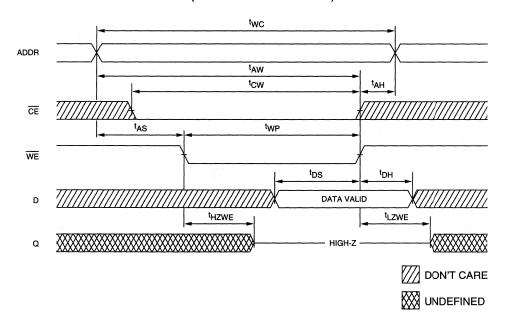

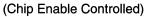

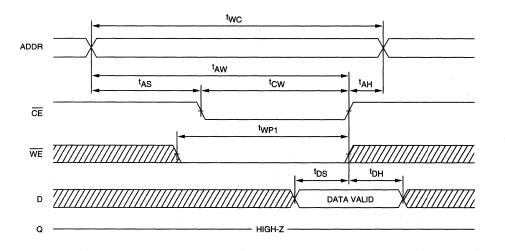

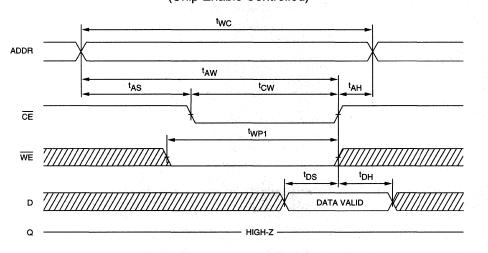

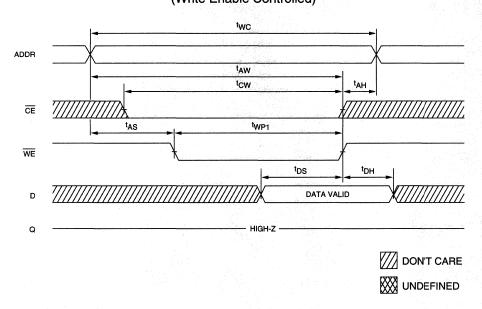

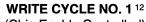

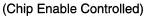

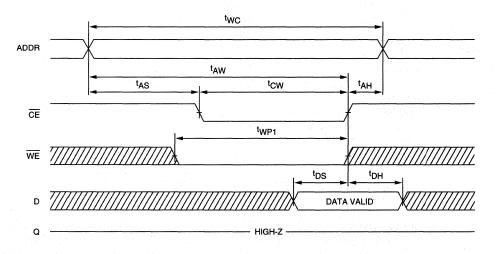

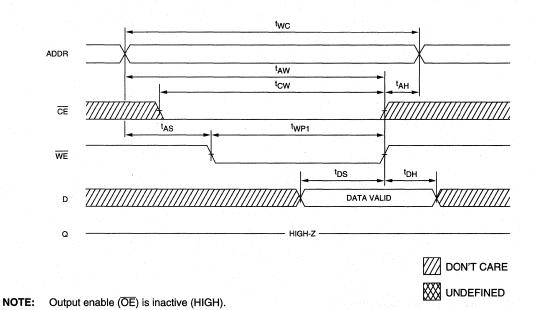

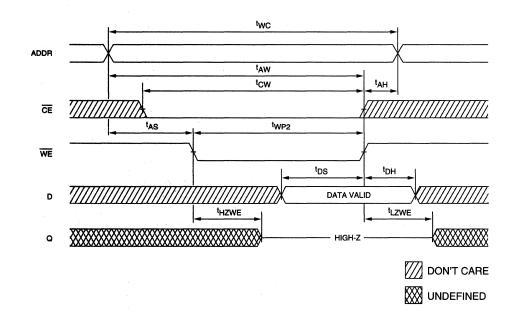

| WRITE cycle time                                 | tWC               | 10      |     | 12  | 1.1 | 15  |     | 20    |     | 25  |          | ns    |       |

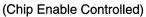

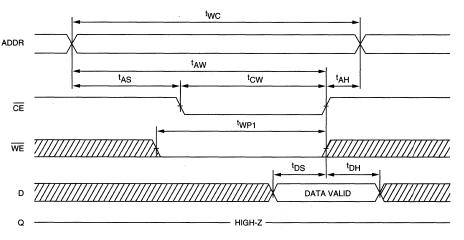

| Chip Enable to end of write                      | tCW               | 7       |     | 8   |     | 10  |     | 12    |     | 15  |          | ns    | 1.4   |

| Chip Enable to end of write (P and LP version)   | tCW               | -       |     | -   |     | 12  |     | 12    |     | 15  |          | ns    |       |

| Address valid to end of write                    | tAW               | 7       |     | 8   |     | 10  |     | 12    | ·   | 15  |          | ns    |       |

| Address valid to end of write (P and LP version) | <sup>t</sup> AW   | -       |     | -   |     | 12  |     | 12    |     | 15  |          | ns    |       |

| Address setup time                               | <sup>t</sup> AS   | 0       |     | 0   |     | 0   |     | 0     |     | 0   |          | ns    |       |

| Address hold from end of write                   | <sup>t</sup> AH   | 1       |     | 1   |     | 1   |     | 1     |     | 1   | 1947 - L | ns    | 1.1   |

| WRITE pulse width                                | tWP               | 7       |     | 8   |     | 10  |     | 12    |     | 15  |          | ns    |       |

| Data setup time                                  | <sup>t</sup> DS   | 6       |     | 7   |     | 7   |     | 10    |     | 10  |          | ns    |       |

| Data hold time                                   | <sup>t</sup> DH   | 0       |     | 0   |     | 0   |     | 0     |     | 0   |          | ns    |       |

| Write disable to output in Low-Z                 | <sup>t</sup> LZWE | 2       |     | 2   |     | 2   |     | 2     |     | 2   |          | ns    | 7     |

| Write Enable to output in High-Z                 | <sup>t</sup> HZWE |         | 5   |     | 6   |     | 7   |       | 8   |     | 10       | ns    | 6, 7  |

### **INDUSTRIAL TEMPERATURE SPECIFICATIONS (IT)**

The following specifications are to be used for Industrial Temperature (IT) MT5C2561 SRAMs. (-40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C - AT) (-55°C  $\leq$  T<sub>A</sub>  $\leq$  125°C - XT)

| · · · · · · · · · · · · · · · · · · · |                                                                                                 |        |     |     | MAX |     | al de la companya de<br>La companya de la comp |       |       |

|---------------------------------------|-------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| DESCRIPTION                           | CONDITIONS                                                                                      | SYMBOL | -10 | -12 | -15 | -20 | -25                                                                                                                                                                                                                                | UNITS | NOTES |