# Desktop 4th Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family, Desktop Intel<sup>®</sup> Pentium<sup>®</sup> Processor Family, and Desktop Intel<sup>®</sup> Celeron<sup>®</sup> Processor Family

**Specification Update**

December 2013 Revision 007

Reference Number: 328899-007

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm.

Code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit: http://www.intel.com/go/virtualization.

Intel<sup>®</sup> Turbo Boost Technology requires a system with Intel<sup>®</sup> Turbo Boost Technology. Intel Turbo Boost Technology and Intel Turbo Boost Technology 2.0 are only available on select Intel<sup>®</sup> processors. Consult your PC manufacturer. Performance varies depending on hardware, software, and system configuration. For more information, visit: http://www.intel.com/go/turbo.

Intel<sup>®</sup> Hyper-Threading Technology requires an Intel<sup>®</sup> HT Technology enabled system, check with your PC manufacturer. Performance will vary depending on the specific hardware and software used. Not available on Intel<sup>®</sup> Core™ i5-750. For more information including details on which processors support HT Technology, visit http://www.intel.com/info/hyperthreading.

Intel<sup>®</sup> 64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific hardware and software you use. Consult your PC manufacturer for more information. For more information, visit: http://www.intel.com/info/em64t.

Intel, Intel Core, Intel386, Intel486, Pentium, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2013, Intel Corporation. All rights reserved.

### Contents

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 6  |

| Summary Tables of Changes    | 8  |

| Identification Information   | 14 |

| Errata                       | 17 |

| Specification Changes        | 47 |

| Specification Clarifications | 48 |

| Documentation Changes        | 49 |

#### §§

# **Revision History**

| Revision | Description                                                                                                                                                                | Date          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 001      | Initial Release.                                                                                                                                                           | June 2013     |

| 002      | <ul> <li>No Updates. Revision number added to Revision History to maintain<br/>consistency with NDA Specification Update numbering.</li> </ul>                             | N/A           |

| 003      | <ul> <li>Errata <ul> <li>Added HSD59-99</li> </ul> </li> <li>Updated Identification Information</li> </ul>                                                                 | August 2013   |

| 004      | <ul> <li>No Updates. Revision number added to Revision History to maintain<br/>consistency with NDA Specification Update numbering.</li> </ul>                             | N/A           |

| 005      | <ul> <li>Errata         <ul> <li>Moved previous HSD99 to HSD108</li> <li>Added HSD99-107 and HSD109-115</li> </ul> </li> <li>Updated Identification Information</li> </ul> | November 2013 |

| 006      | <ul> <li>Identification Information         <ul> <li>Updated Desktop Processor Identification table</li> </ul> </li> </ul>                                                 | December 2013 |

| 007      | Errata     Added HSD116-118                                                                                                                                                | December 2013 |

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### **Affected Documents**

| Document Title                                                                                                                                                                                                                                    | Document Number |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Desktop 4th Generation Intel <sup>®</sup> Core <sup>™</sup> Processor Family, Desktop Intel <sup>®</sup> Pentium <sup>®</sup> Processor Family,<br>and Desktop Intel <sup>®</sup> Celeron <sup>®</sup> Processor Family Datasheet – Volume 1 of 2 | 328897          |

| Desktop 4th Generation Intel <sup>®</sup> Core <sup>™</sup> Processor Family, Desktop Intel <sup>®</sup> Pentium <sup>®</sup> Processor Family, and Desktop Intel <sup>®</sup> Celeron <sup>®</sup> Processor Family Datasheet – Volume 2 of 2    | 328898          |

### **Related Documents**

| Document Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Document Number/<br>Location                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| AP-485, Intel <sup>®</sup> Processor Identification and the CPUID Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | http://www.intel.com/<br>design/processor/<br>applnots/241618.htm |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture<br>Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set<br>Reference Manual A-M<br>Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set<br>Reference Manual N-Z<br>Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming<br>Guide<br>Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming<br>Guide<br>Intel <sup>®</sup> 64 and IA-32 Intel Architecture Optimization Reference Manual | http://www.intel.com/<br>products/processor/<br>manuals/index.htm |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual Documentation Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | http://www.intel.com/<br>design/processor/<br>specupdt/252046.htm |

| ACPI Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | www.acpi.info                                                     |

#### Nomenclature

**Errata** are design defects or errors. These may cause the processor behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics such as, core speed, L2 cache size, package type, etc. as described in the processor identification information table. Read all notes associated with each S-Spec number.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

**Note:** Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so on).

# (intel) Summary Tables of Changes

The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the processor. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables uses the following notations.

### **Codes Used in Summary Tables**

#### Stepping

| X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| (No mark)       |                                                                                                               |

| or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

|                 |                                                                                                               |

| (Page):         | Page location of item in this document.                                                                       |

|                 |                                                                                                               |

| Doc:            | Document change or update will be implemented.                                                                |

| Plan Fix:       | This erratum may be fixed in a future stepping of the product.                                                |

| Fixed:          | This erratum has been previously fixed.                                                                       |

| No Fix:         | There are no plans to fix this erratum.                                                                       |

|                 |                                                                                                               |

#### Row

Page

**Status**

Change bar to left of a table row indicates this erratum is either new or modified from the previous version of the document.

### Errata (Sheet 1 of 5)

| Steppings | Chathara |        |                                                                                                                      |

|-----------|----------|--------|----------------------------------------------------------------------------------------------------------------------|

| Number    | C-0      | Status | ERRATA                                                                                                               |

| HSD1      | х        | No Fix | LBR, BTS, BTM May Report a Wrong Address when an Exception/<br>Interrupt Occurs in 64-bit Mode                       |

| HSD2      | х        | No Fix | EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change                             |

| HSD3      | х        | No Fix | MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error                                  |

| HSD4      | Х        | No Fix | LER MSRs May Be Unreliable                                                                                           |

| HSD5      | х        | No Fix | MONITOR or CLFLUSH on the Local XAPIC's Address Space Results in Hang                                                |

| HSD6      | Х        | No Fix | An Uncorrectable Error Logged in IA32_CR_MC2_STATUS May also Result in a System Hang                                 |

| HSD7      | х        | No Fix | #GP on Segment Selector Descriptor that Straddles Canonical Boundary<br>May Not Provide Correct Exception Error Code |

| HSD8      | х        | No Fix | FREEZE_WHILE_SMM Does Not Prevent Event From Pending<br>PEBS During SMM                                              |

| HSD9      | Х        | No Fix | APIC Error "Received Illegal Vector" May be Lost                                                                     |

| HSD10     | х        | No Fix | Changing the Memory Type for an In-Use Page Translation May Lead to Memory-Ordering Violations                       |

| HSD11     | х        | No Fix | Performance Monitor Precise Instruction Retired Event May Present<br>Wrong Indications                               |

| HSD12     | Х        | No Fix | CR0.CD Is Ignored in VMX Operation                                                                                   |

| HSD13     | х        | No Fix | Instruction Fetch May Cause Machine Check if Page Size and Memory Type Was Changed Without Invalidation              |

| HSD14     | х        | No Fix | Execution of VAESIMC or VAESKEYGENASSIST With An Illegal Value for VEX.vvvv May Produce a #NM Exception              |

| HSD15     | Х        | No Fix | Processor May Fail to Acknowledge a TLP Request                                                                      |

| HSD16     | х        | No Fix | Interrupt From Local APIC Timer May Not Be Detectable While Being Delivered                                          |

| HSD17     | х        | No Fix | PCIe* Root-port Initiated Compliance State Transmitter Equalization<br>Settings May be Incorrect                     |

| HSD18     | Х        | No Fix | PCIe* Controller May Incorrectly Log Errors on Transition to RxL0s                                                   |

| HSD19     | Х        | No Fix | Unused PCIe* Lanes May Report Correctable Errors                                                                     |

| HSD20     | х        | No Fix | Accessing Physical Memory Space 0-640K through the Graphics<br>Aperture May Cause Unpredictable System Behavior      |

| HSD21     | Х        | No Fix | PCIe Root Port May Not Initiate Link Speed Change                                                                    |

| HSD22     | Х        | No Fix | Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected                                               |

| HSD23     | х        | No Fix | DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/POP SS is Followed by a Store or an MMX Instruction      |

| HSD24     | Х        | No Fix | VEX.L is Not Ignored with VCVT*2SI Instructions                                                                      |

| HSD25     | х        | No Fix | Certain Local Memory Read / Load Retired PerfMon Events May<br>Undercount                                            |

### Errata (Sheet 2 of 5)

|        | Steppings |        |                                                                                                                    |

|--------|-----------|--------|--------------------------------------------------------------------------------------------------------------------|

| Number | C-0       | Status | ERRATA                                                                                                             |

| HSD26  | х         | No Fix | Specific Graphics Blitter Instructions May Result in Unpredictable Graphics Controller Behavior                    |

| HSD27  | х         | No Fix | Processor May Enter Shutdown Unexpectedly on a Second Uncorrectable Error                                          |

| HSD28  | х         | No Fix | Modified Compliance Patterns for 2.5 GT/s and 5 GT/s Transfer Rates Do Not Follow PCIe* Specification              |

| HSD29  | Х         | No Fix | Performance Monitor Counters May Produce Incorrect Results                                                         |

| HSD30  | Х         | No Fix | Performance Monitor UOPS_EXECUTED Event May Undercount                                                             |

| HSD31  | Х         | No Fix | MSR_PERF_STATUS May Report an Incorrect Core Voltage                                                               |

| HSD32  | х         | No Fix | PCIe* Atomic Transactions From Two or More PCIe Controllers May Cause Starvation                                   |

| HSD33  | х         | No Fix | The Corrected Error Count Overflow Bit in IA32_MC0_STATUS is Not Updated After a UC Error is Logged                |

| HSD34  | х         | No Fix | An AVX Gather Instruction That Causes an EPT Violation May Not<br>Update Previous Elements                         |

| HSD35  | Х         | No Fix | PLATFORM_POWER_LIMIT MSR Not Visible                                                                               |

| HSD36  | Х         | No Fix | LPDDR Memory May Report Incorrect Temperature                                                                      |

| HSD37  | Х         | No Fix | PCIe* Host Bridge DID May Be Incorrect                                                                             |

| HSD38  | Х         | No Fix | TSC May be Incorrect After a Deep C-State Exit                                                                     |

| HSD39  | х         | No Fix | PCIe* Controller May Initiate Speed Change While in DL_Init State<br>Causing Certain PCIe Devices to Fail to Train |

| HSD40  | Х         | No Fix | Spurious VT-d Interrupts May Occur When the PFO Bit is Set                                                         |

| HSD41  | Х         | No Fix | N/A. Erratum has been removed.                                                                                     |

| HSD42  | х         | No Fix | AVX Gather Instruction That Causes a Fault or VM Exit May Incorrectly<br>Modify Its Destination Register           |

| HSD43  | х         | No Fix | Inconsistent NaN Propagation May Occur When Executing (V)DPPS Instruction                                          |

| HSD44  | Х         | No Fix | Display May Flicker When Package C-States Are Enabled                                                              |

| HSD45  | х         | No Fix | Certain Combinations of AVX Instructions May Cause Unpredictable System Behavior                                   |

| HSD46  | Х         | No Fix | Processor May Incorrectly Estimate Peak Power Delivery Requirements                                                |

| HSD47  | Х         | No Fix | IA32_PERF_CTL MSR is Incorrectly Reset                                                                             |

| HSD48  | Х         | No Fix | Processor May Hang During a Function Level Reset of the Display                                                    |

| HSD49  | Х         | No Fix | AVX Gather Instruction That Should Result in #DF May Cause<br>Unexpected System Behavior                           |

| HSD50  | х         | No Fix | Throttling and Refresh Rate Maybe be Incorrect After Exiting Package C-State                                       |

| HSD51  | Х         | No Fix | Processor May Livelock During On Demand Clock Modulation                                                           |

| HSD52  | х         | No Fix | IA32_DEBUGCTL.FREEZE_PERFMON_ON_PMI is Incorrectly Cleared by SMI                                                  |

| HSD53  | Х         | No Fix | The From-IP for Branch Tracing May be Incorrect                                                                    |

| HSD54  | Х         | No Fix | TM1 Throttling May Continue indefinitely                                                                           |

### Errata (Sheet 3 of 5)

|        | Steppings |        |                                                                                                       |

|--------|-----------|--------|-------------------------------------------------------------------------------------------------------|

| Number | C-0       | Status | ERRATA                                                                                                |

| HSD55  | х         | No Fix | Internal Parity Errors May Incorrectly Report Overflow in The IA32_MCi_STATUS MSR                     |

| HSD56  | х         | No Fix | Performance Monitor Events OTHER_ASSISTS.AVX_TO_SSE And OTHER_ASSISTS.SSE_TO_AVX May Over Count       |

| HSD57  | Х         | No Fix | Processor May Run at Incorrect P-State                                                                |

| HSD58  | х         | No Fix | Performance Monitor Event DSB2MITE_SWITCHES.COUNT May Over Count                                      |

| HSD59  | х         | No Fix | Performance Monitor Register UNC_PERF_GLOBAL_STATUS Not<br>Restored on Package C7 Exit                |

| HSD60  | х         | No Fix | Processor May Not Enter Package C6 or Deeper C-states When PCIe*<br>Links Are Disabled                |

| HSD61  | х         | No Fix | Performance Monitor Event For Outstanding Offcore Requests And Snoop Requests May Over Count          |

| HSD62  | х         | No Fix | Some Performance Monitor Event Counts May be Inaccurate During SMT Mode                               |

| HSD63  | Х         | No Fix | Timed MWAIT May Use Deadline of a Previous Execution                                                  |

| HSD64  | Х         | No Fix | The Upper 32 Bits of CR3 May be Incorrectly Used With 32-Bit Paging                                   |

| HSD65  | х         | No Fix | Performance Monitor Events HLE_RETIRED.ABORTED_MISC4 And RTM_RETIRED.ABORTED_MISC4 May Over Count     |

| HSD66  | Х         | No Fix | A PCIe* LTR Update Message May Cause The Processor to Hang                                            |

| HSD67  | Х         | No Fix | GETSEC Does Not Report Support For S-CRTM                                                             |

| HSD68  | Х         | No Fix | EPT Violations May Report Bits 11:0 of Guest Linear Address Incorrectly                               |

| HSD69  | Х         | No Fix | APIC Timer Might Not Signal an Interrupt While in TSC-Deadline Mode                                   |

| HSD70  | х         | No Fix | IA32_VMX_VMCS_ENUM MSR (48AH) Does Not Properly Report The Highest Index Value Used For VMCS Encoding |

| HSD71  | х         | No Fix | Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be<br>Observed                             |

| HSD72  | х         | No Fix | VT-d Hardware May Perform STRP And SIRTP Operations on a Package C7 Exit                              |

| HSD73  | Х         | No Fix | General-Purpose Performance Counters Can Unexpectedly Increment                                       |

| HSD74  | х         | No Fix | Performance Monitoring Events May Report Incorrect Number of Load<br>Hits or Misses to LLC            |

| HSD75  | х         | No Fix | Performance Monitoring Event INSTR_RETIRED.ALL May Generate<br>Redundant PEBS Records For an Overflow |

| HSD76  | Х         | No Fix | Locked Load Performance Monitoring Events May Under Count                                             |

| HSD77  | х         | No Fix | Graphics Processor Ratio And C-State Transitions May Cause a System Hang                              |

| HSD78  | х         | No Fix | Certain Performance Monitoring Events May Over Count Software<br>Demand Loads                         |

| HSD79  | х         | No Fix | Accessing Nonexistent Uncore Performance Monitoring MSRs May Not Signal a #GP                         |

| HSD80  | Х         | No Fix | Call Stack Profiling May Produce Extra Call Records                                                   |

| HSD81  | Х         | No Fix | Warm Reset May Fail or Lead to Incorrect Power Regulation                                             |

## Errata (Sheet 4 of 5)

| Number | Steppings |        |                                                                                                      |

|--------|-----------|--------|------------------------------------------------------------------------------------------------------|

| Number | C-0       | Status | ERRATA                                                                                               |

| HSD82  | Х         | No Fix | PCIe* Host Bridge DID May Be Incorrect                                                               |

| HSD83  | Х         | No Fix | Transactional Abort May Produce an Incorrect Branch Record                                           |

| HSD84  | х         | No Fix | SMRAM State-Save Area Above the 4GB Boundary May Cause Unpredictable System Behavior                 |

| HSD85  | х         | No Fix | DMA Remapping Faults for the Graphics VT-d Unit May Not Properly Report Type of Faulted Request      |

| HSD86  | х         | No Fix | AVX Gather Instructions Page Faults May Report an Incorrect Faulting Address                         |

| HSD87  | Х         | No Fix | Intel® TSX Instructions May Cause Unpredictable System behavior                                      |

| HSD88  | Х         | No Fix | Event Injection by VM Entry May Use an Incorrect B Flag for SS                                       |

| HSD89  | Х         | No Fix | A Fault in SMM May Result in Unpredictable System Behavior                                           |

| HSD90  | х         | No Fix | Processor Frequency is Unexpectedly Limited Below Nominal P1 When cTDP Down is Enabled               |

| HSD91  | х         | No Fix | PMI May be Signaled More Than Once For Performance Monitor Counter Overflow                          |

| HSD92  | х         | No Fix | Execution of FXSAVE or FXRSTOR With the VEX Prefix May Produce a #NM Exception                       |

| HSD93  | х         | No Fix | RDRAND Execution in a Transactional Region May Cause a System Hang                                   |

| HSD94  | Х         | No Fix | Uncore Clock Frequency Changes May Cause Audio/Video Glitches                                        |

| HSD95  | х         | No Fix | Processor May Experience a Spurious LLC-Related Machine Check<br>During Periods of High Activity     |

| HSD96  | Х         | No Fix | The Processor May Not Enter Package C7 When Using a PSR Display                                      |

| HSD97  | Х         | No Fix | Video/Audio Distortion May Occur                                                                     |

| HSD98  | Х         | No Fix | System May Hang When Audio is Enabled During Package C3                                              |

| HSD99  | Х         | No Fix | INVPCID May Not Cause #UD in VMX Non-Root Operation                                                  |

| HSD100 | х         | No Fix | Non-Compliant PFAT Module Base Address May Cause Unpredictable System Behavior                       |

| HSD101 | х         | No Fix | Incorrect LBR Source Address May be Reported For a Transactional Abort                               |

| HSD102 | х         | No Fix | Address Translation Faults for Intel® VT-d May Not be Reported for<br>Display Engine Memory Accesses |

| HSD103 | х         | No Fix | L3 Cache Corrected Error Count May be Inaccurate After Package C7<br>Exit                            |

| HSD104 | Х         | No Fix | PCIe* Device's SVID is Not Preserved Across The Package C7 C-State                                   |

| HSD105 | Х         | No Fix | Warm Reset Does Not Stop GT Power Draw                                                               |

| HSD106 | Х         | No Fix | Unused PCIe* Lanes May Remain Powered After Package C7                                               |

| HSD107 | Х         | No Fix | BMI1 And BMI2 Instruction Groups Are Not Available                                                   |

| HSD108 | х         | No Fix | Virtual-APIC Page Accesses With 32-Bit PAE Paging May Cause a System Crash                           |

| HSD109 | Х         | No Fix | Processor Energy Policy Selection May Not Work as Expected                                           |

### Errata (Sheet 5 of 5)

| Number | Steppings | Status | ERRATA                                                                         |

|--------|-----------|--------|--------------------------------------------------------------------------------|

| Number | C-0       |        | ERRATA                                                                         |

| HSD110 | х         | No Fix | A PEBS Record May Contain Processor State for an Unexpected Instruction        |

| HSD111 | Х         | No Fix | MSR_PP1_ENERGY_STATUS Reports Incorrect Energy Data                            |

| HSD112 | х         | No Fix | x87 FPU DP May be Incorrect After Instructions That Save FP State to<br>Memory |

| HSD113 | Х         | No Fix | Processor May Hang During Package C7 Exit                                      |

| HSD114 | Х         | No Fix | Intel® TSX Instructions May Cause Unpredictable System behavior                |

| HSD115 | Х         | No Fix | Spurious LLC Machine Check May Occur                                           |

| HSD116 | Х         | No Fix | Page Fault May Report Incorrect Fault Information                              |

| HSD117 | Х         | No Fix | CATERR# Pin Assertion is Not Cleared on a Warm Reset                           |

| HSD118 | х         | No Fix | Uncorrectable Machine Check Error During Core C6 Entry May Not be Signaled     |

### **Specification Changes**

| Number | SPECIFICATION CHANGES                                |

|--------|------------------------------------------------------|

|        | None for this revision of this specification update. |

### Specification Clarifications

| Number | SPECIFICATION CLARIFICATIONS                         |

|--------|------------------------------------------------------|

|        | None for this revision of this specification update. |

### **Documentation Changes**

| Number | DOCUMENTATION CHANGES                              |

|--------|----------------------------------------------------|

| HSD1   | "On-Demand Clock Modulation Feature Clarification" |

# (intel)

# **Identification Information**

### **Component Identification using Programming Interface**

The processor stepping can be identified by the following register contents.

## Table 1.Desktop 4th Generation Intel<sup>®</sup> Core™ Processor Family Component<br/>Identification

| Reserved | Extended<br>Family | Extended<br>Model | Reserved | Processor<br>Type | Family<br>Code | Model<br>Number | Stepping<br>ID |

|----------|--------------------|-------------------|----------|-------------------|----------------|-----------------|----------------|

| 31:28    | 27:20              | 19:16             | 15:14    | 13:12             | 11:8           | 7:4             | 3:0            |

|          | 00000000b          | 0011b             |          | 00b               | 0110b          | 1100b           | xxxxb          |

#### Notes:

- The Extended Family, Bits [27:20] are used in conjunction with the Family Code, specified in Bits[11:8], to indicate whether the processor belongs to the Intel386<sup>™</sup>, Intel486<sup>™</sup>, Pentium<sup>®</sup>, Pentium 4, or Intel<sup>®</sup> Core<sup>™</sup> processor family.

- 2. The Extended Model, Bits [19:16] in conjunction with the Model Number, specified in Bits [7:4], are used to identify the model of the processor within the processor's family.

- 3. The Family Code corresponds to Bits [11:8] of the EDX register after RESET, Bits [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register accessible through Boundary Scan.

- ID register accessible through Boundary Scan.

The Model Number corresponds to Bits [7:4] of the EDX register after RESET, Bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register accessible through Boundary Scan.

- 5. The Stepping ID in Bits [3:0] indicates the revision number of that model. See the processor Identification table for the processor stepping ID number in the CPUID information.

When EAX is initialized to a value of '1', the CPUID instruction returns the Extended Family, Extended Model, Processor Type, Family Code, Model Number and Stepping ID value in the EAX register. Note that the EDX processor signature value after reset is equivalent to the processor signature output value in the EAX register.

Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with a 2 in the EAX register.

The processor can be identified by the following register contents.

| Stepping | Vendor ID <sup>1</sup> | Host Device<br>ID <sup>2</sup> | Processor Graphics<br>Device ID <sup>3</sup> | Revision ID <sup>4</sup> | CRID |

|----------|------------------------|--------------------------------|----------------------------------------------|--------------------------|------|

| C-0      | 8086h                  | 0C04h                          | GT2 = 0416h                                  | 06h                      | 06h  |

#### Notes:

1. The Vendor ID corresponds to bits 15:0 of the Vendor ID Register located at offset 00h–01h in the PCI function 0 configuration space.

The Host Device ID corresponds to bits 15:0 of the Device ID Register located at Device 0 offset 02h– 03h in the PCI function 0 configuration space.

4. The Revision Number corresponds to bits 7:0 of the Revision ID Register located at offset 08h in the PCI function 0 configuration space.

The Processor Graphics Device ID (DID2) corresponds to bits 15:0 of the Device ID Register located at Device 2 offset 02h–03h in the PCI function 0 configuration space.

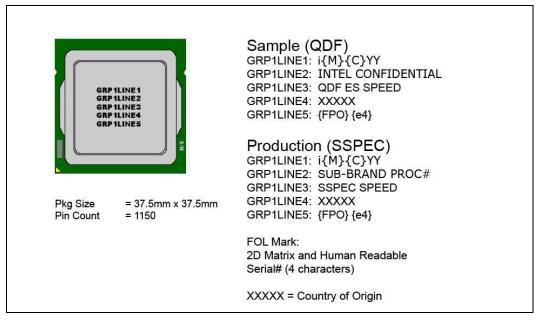

#### **Component Marking Information**

The processor stepping can be identified by the following component markings.

#### Figure 1. Desktop 4th Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family Top-Side Markings

### Table 2.Desktop Processor Identification (Sheet 1 of 2)

| S-Spec<br>Number | Processor<br>Number | Stepping | Cache<br>Size<br>(MB) | Func-<br>tional<br>Core | Integrated<br>Graphics<br>Cores | Max<br>Turbo<br>Freq.<br>Rate<br>(GHz) | Memory<br>(MHz) | Core<br>Freq.<br>(GHz) | Thermal<br>Design<br>Power<br>(W) |

|------------------|---------------------|----------|-----------------------|-------------------------|---------------------------------|----------------------------------------|-----------------|------------------------|-----------------------------------|

| SR147            | I7-4770K            | C-0      | 8                     | 4                       | 2                               | 3.9                                    | 1600            | 3.5                    | 95                                |

| SR149            | I7-4770             | C-0      | 8                     | 4                       | 2                               | 3.9                                    | 1600            | 3.4                    | 95                                |

| SR14A            | I5-4670K            | C-0      | 6                     | 4                       | 2                               | 3.8                                    | 1600            | 3.4                    | 95                                |

| SR14D            | I5-4670             | C-0      | 6                     | 4                       | 2                               | 3.8                                    | 1600            | 3.4                    | 95                                |

| SR14E            | I5-4570             | C-0      | 6                     | 4                       | 2                               | 3.6                                    | 1600            | 3.2                    | 95                                |

| SR14F            | I5-4440             | C-0      | 6                     | 4                       | 2                               | 3.3                                    | 1600            | 3.1                    | 95                                |

| SR14G            | I5-4430             | C-0      | 6                     | 4                       | 2                               | 3.2                                    | 1600            | 3                      | 95                                |

| SR14H            | I7-4770S            | C-0      | 8                     | 4                       | 2                               | 3.9                                    | 1600            | 3.1                    | 65                                |

| SR14J            | I5-4570S            | C-0      | 6                     | 4                       | 2                               | 3.6                                    | 1600            | 2.9                    | 65                                |

| SR14K            | I5-4670S            | C-0      | 6                     | 4                       | 2                               | 3.8                                    | 1600            | 3.1                    | 65                                |

| SR14L            | I5-4440S            | C-0      | 6                     | 4                       | 2                               | 3.3                                    | 1600            | 2.8                    | 65                                |

| SR14M            | I5-4430S            | C-0      | 6                     | 4                       | 2                               | 3.2                                    | 1600            | 2.7                    | 65                                |

| SR14N            | I7-4770T            | C-0      | 8                     | 4                       | 2                               | 3.7                                    | 1600            | 2.5                    | 45                                |

| SR14P            | I5-4670T            | C-0      | 6                     | 4                       | 2                               | 3.3                                    | 1600            | 2.3                    | 45                                |

| SR14Q            | I7-4765T            | C-0      | 8                     | 4                       | 2                               | 3                                      | 1600            | 2                      | 35                                |

| S-Spec<br>Number | Processor<br>Number | Stepping | Cache<br>Size<br>(MB) | Func-<br>tional<br>Core | Integrated<br>Graphics<br>Cores | Max<br>Turbo<br>Freq.<br>Rate<br>(GHz) | Memory<br>(MHz) | Core<br>Freq.<br>(GHz) | Thermal<br>Design<br>Power<br>(W) |

|------------------|---------------------|----------|-----------------------|-------------------------|---------------------------------|----------------------------------------|-----------------|------------------------|-----------------------------------|

| SR18K            | I7-4770R            | C-0      | 6                     | 4                       | 3                               | 3.9                                    | 1600            | 3.2                    | 65                                |

| SR18M            | I5-4670R            | C-0      | 4                     | 4                       | 3                               | 3.7                                    | 1600            | 3                      | 65                                |

| SR18Q            | I5-4570R            | C-0      | 4                     | 4                       | 3                               | 3.2                                    | 1600            | 2.7                    | 65                                |

| SR1BW            | I7-4771             | C-0      | 8                     | 4                       | 2                               | 3.9                                    | 1600            | 3.5                    | 95                                |

| SR1CA            | I5-4570T            | C-0      | 4                     | 2                       | 2                               | 3.6                                    | 1600            | 2.9                    | 35                                |

| SR1CE            | G3430               | C-0      | 3                     | 2                       | 1                               | 3.3                                    | 1600            | 3.3                    | 65                                |

| SR1CG            | G3220               | C-0      | 3                     | 2                       | 1                               | 3                                      | 1333            | 3                      | 65                                |

| SR1CL            | G3220T              | C-0      | 3                     | 2                       | 1                               | 2.6                                    | 1333            | 2.6                    | 35                                |

| SR1NB            | G3420               | C-0      | 3                     | 2                       | 1                               | 3.2                                    | 1333            | 3.2                    | 65                                |

| SR1NK            | I3-4330T            | C-0      | 4                     | 2                       | 2                               | 3                                      | 1600            | 3                      | 35                                |

| SR1NL            | I3-4340             | C-0      | 4                     | 2                       | 2                               | 3.6                                    | 1600            | 3.6                    | 65                                |

| SR1NM            | I3-4330             | C-0      | 4                     | 2                       | 2                               | 3.5                                    | 1600            | 3.5                    | 65                                |

| SR1NN            | I3-4130T            | C-0      | 3                     | 2                       | 2                               | 2.9                                    | 1600            | 2.9                    | 35                                |

| SR1NP            | I3-4130             | C-0      | 3                     | 2                       | 2                               | 3.4                                    | 1600            | 3.4                    | 65                                |

| SR1CN            | Celeron<br>G1820    | C-0      | 2                     | 2                       | 1                               | 2.7                                    | 1333            | 2.7                    | 65                                |

| SR1CP            | Celeron<br>G1820T   | C-0      | 2                     | 2                       | 1                               | 2.4                                    | 1333            | 2.4                    | 35                                |

| SR1NC            | Celeron<br>G1830    | C-0      | 2                     | 2                       | 1                               | 2.8                                    | 1333            | 2.8                    | 65                                |

#### Table 2. Desktop Processor Identification (Sheet 2 of 2)

# Errata

#### HSD1. LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode

- Problem: An exception/interrupt event should be transparent to the LBR (Last Branch Record), BTS (Branch Trace Store) and BTM (Branch Trace Message) mechanisms. However, during a specific boundary condition where the exception/interrupt occurs right after the execution of an instruction at the lower canonical boundary (0x00007FFFFFFFFF) in 64-bit mode, the LBR return registers will save a wrong return address with bits 63 to 48 incorrectly sign extended to all 1's. Subsequent BTS and BTM operations which report the LBR will also be incorrect.

- Implication: LBR, BTS and BTM may report incorrect information in the event of an exception/ interrupt.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

# HSD2. EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change

- Problem: This erratum is regarding the case where paging structures are modified to change a linear address from writable to non-writable without software performing an appropriate TLB invalidation. When a subsequent access to that address by a specific instruction (ADD, AND, BTC, BTR, BTS, CMPXCHG, DEC, INC, NEG, NOT, OR, ROL/ROR, SAL/SAR/SHL/SHR, SHLD, SHRD, SUB, XOR, and XADD) causes a page fault or an EPT-induced VM exit, the value saved for EFLAGS may incorrectly contain the arithmetic flag values that the EFLAGS register would have held had the instruction completed without fault or VM exit. For page faults, this can occur even if the fault causes a VM exit or if its delivery causes a nested fault.

- Implication: None identified. Although the EFLAGS value saved by an affected event (a page fault or an EPT-induced VM exit) may contain incorrect arithmetic flag values, Intel has not identified software that is affected by this erratum. This erratum will have no further effects once the original instruction is restarted because the instruction will produce the same results as if it had initially completed without fault or VM exit.

- Workaround: If the handler of the affected events inspects the arithmetic portion of the saved EFLAGS value, then system software should perform a synchronized paging structure modification and TLB invalidation.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD3. MCi\_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error

- Problem: A single Data Translation Look Aside Buffer (DTLB) error can incorrectly set the Overflow (bit [62]) in the MCi\_Status register. A DTLB error is indicated by MCA error code (bits [15:0]) appearing as binary value, 000x 0000 0001 0100, in the MCi\_Status register.

- Implication: Due to this erratum, the Overflow bit in the MCi\_Status register may not be an accurate indication of multiple occurrences of DTLB errors. There is no other impact to normal processor functionality.

Workaround: None identified.

Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD4. LER MSRs May Be Unreliable

Problem: Due to certain internal processor events, updates to the LER (Last Exception Record) MSRs, MSR\_LER\_FROM\_LIP (1DDH) and MSR\_LER\_TO\_LIP (1DEH), may happen when no update was expected.

- Implication: The values of the LER MSRs may be unreliable.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

- HSD5. MONITOR or CLFLUSH on the Local XAPIC's Address Space Results in Hang

- Problem: If the target linear address range for a MONITOR or CLFLUSH is mapped to the local xAPIC's address space, the processor will hang.

- Implication: When this erratum occurs, the processor will hang. The local xAPIC's address space must be uncached. The MONITOR instruction only functions correctly if the specified linear address range is of the type write-back. CLFLUSH flushes data from the cache. Intel has not observed this erratum with any commercially available software.

- Workaround: Do not execute MONITOR or CLFLUSH instructions on the local xAPIC address space.

- Status: For the steppings affected, see the *Summary Table of Changes*.

# HSD6. An Uncorrectable Error Logged in IA32\_CR\_MC2\_STATUS May also Result in a System Hang

- Problem: Uncorrectable errors logged in IA32\_CR\_MC2\_STATUS MSR (409H) may also result in a system hang causing an Internal Timer Error (MCACOD = 0x0400h) to be logged in another machine check bank (IA32\_MCi\_STATUS).

- Implication: Uncorrectable errors logged in IA32\_CR\_MC2\_STATUS can further cause a system hang and an Internal Timer Error to be logged.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD7. **#GP on Segment Selector Descriptor that Straddles Canonical** Boundary May Not Provide Correct Exception Error Code

- Problem: During a #GP (General Protection Exception), the processor pushes an error code on to the exception handler's stack. If the segment selector descriptor straddles the canonical boundary, the error code pushed onto the stack may be incorrect.

- Implication: An incorrect error code may be pushed onto the stack. Intel has not observed this erratum with any commercially available software.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD8. FREEZE\_WHILE\_SMM Does Not Prevent Event From Pending PEBS During SMM

- Problem: In general, a PEBS record should be generated on the first count of the event after the counter has overflowed. However, IA32\_DEBUGCTL\_MSR.FREEZE\_WHILE\_SMM (MSR 1D9H, bit [14]) prevents performance counters from counting during SMM (System Management Mode). Due to this erratum, if

- 1. A performance counter overflowed before an SMI

- 2. A PEBS record has not yet been generated because another count of the event has not occurred

- 3. The monitored event occurs during SMM

then a PEBS record will be saved after the next RSM instruction.

When  $\mathsf{FREEZE}\_\mathsf{WHILE}\_\mathsf{SMM}$  is set, a PEBS should not be generated until the event occurs outside of SMM.

- Implication: A PEBS record may be saved after an RSM instruction due to the associated performance counter detecting the monitored event during SMM; even when FREEZE\_WHILE\_SMM is set.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD9. APIC Error "Received Illegal Vector" May be Lost

- Problem: APIC (Advanced Programmable Interrupt Controller) may not update the ESR (Error Status Register) flag Received Illegal Vector bit [6] properly when an illegal vector error is received on the same internal clock that the ESR is being written (as part of the write-read ESR access flow). The corresponding error interrupt will also not be generated for this case.

- Implication: Due to this erratum, an incoming illegal vector error may not be logged into ESR properly and may not generate an error interrupt.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

- HSD10. Changing the Memory Type for an In-Use Page Translation May Lead to Memory-Ordering Violations

- Problem: Under complex microarchitectural conditions, if software changes the memory type for data being actively used and shared by multiple threads without the use of semaphores or barriers, software may see load operations execute out of order.

- Implication: Memory ordering may be violated. Intel has not observed this erratum with any commercially available software.

- Workaround: Software should ensure pages are not being actively used before requesting their memory type be changed.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### **HSD11.** Performance Monitor Precise Instruction Retired Event May Present Wrong Indications

- Problem: When the PDIR (Precise Distribution for Instructions Retired) mechanism is activated (INST\_RETIRED.ALL (event COH, umask value 00H) on Counter 1 programmed in PEBS mode), the processor may return wrong PEBS/PMI interrupts and/or incorrect counter values if the counter is reset with a SAV below 100 (Sample-After-Value is the counter reset value software programs in MSR IA32\_PMC1[47:0] in order to control interrupt frequency).

- Implication: Due to this erratum, when using low SAV values, the program may get incorrect PEBS or PMI interrupts and/or an invalid counter state.

- Workaround: The sampling driver should avoid using SAV<100.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD12. CR0.CD Is Ignored in VMX Operation

- Problem: If CR0.CD=1, the MTRRs and PAT should be ignored and the UC memory type should be used for all memory accesses. Due to this erratum, a logical processor in VMX operation will operate as if CR0.CD=0 even if that bit is set to 1.

- Implication: Algorithms that rely on cache disabling may not function properly in VMX operation.

- Workaround: Algorithms that rely on cache disabling should not be executed in VMX root operation.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD13. Instruction Fetch May Cause Machine Check if Page Size and Memory Type Was Changed Without Invalidation

- Problem: This erratum may cause a machine-check error (IA32\_MCi\_STATUS.MCACOD=0150H) on the fetch of an instruction that crosses a 4-KByte address boundary. It applies only if (1) the 4-KByte linear region on which the instruction begins is originally translated using a 4-KByte page with the WB memory type; (2) the paging structures are later modified so that linear region is translated using a large page (2-MByte, 4-MByte, or 1-GByte) with the UC memory type; and (3) the instruction fetch occurs after the paging-structure modification but before software invalidates any TLB entries for the linear region.

- Implication: Due to this erratum an unexpected machine check with error code 0150H may occur, possibly resulting in a shutdown. Intel has not observed this erratum with any commercially available software.

- Workaround: Software should not write to a paging-structure entry in a way that would change, for any linear address, both the page size and the memory type. It can instead use the following algorithm: first clear the P flag in the relevant paging-structure entry (e.g., PDE); then invalidate any translations for the affected linear addresses; and then modify the relevant paging-structure entry to set the P flag and establish the new page size and memory type.

- Status: For the steppings affected, see the *Summary Table of Changes*.

# HSD14. Execution of VAESIMC or VAESKEYGENASSIST With An Illegal Value for VEX.vvvv May Produce a #NM Exception

- Problem: The VAESIMC and VAESKEYGENASSIST instructions should produce a #UD (Invalid-Opcode) exception if the value of the vvvv field in the VEX prefix is not 1111b. Due to this erratum, if CR0.TS is "1", the processor may instead produce a #NM (Device-Not-Available) exception.

- Implication: Due to this erratum, some undefined instruction encodings may produce a #NM instead of a #UD exception.

- Workaround: Software should always set the vvvv field of the VEX prefix to 1111b for instances of the VAESIMC and VAESKEYGENASSIST instructions.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD15. Processor May Fail to Acknowledge a TLP Request

- Problem: When a PCIe root port's receiver is in Receiver LOs power state and the port initiates a Recovery event, it will issue Training Sets to the link partner. The link partner will respond by initiating an LOs exit sequence. Prior to transmitting its own Training Sets, the link partner may transmit a TLP (Transaction Layer Packet) request. Due to this erratum, the root port may not acknowledge the TLP request.

- Implication: After completing the Recovery event, the PCIe link partner will replay the TLP request. The link partner may set a Correctable Error status bit, which has no functional effect.

#### Workaround: None identified.

Status: For the steppings affected, see the *Summary Table of Changes*.

# HSD16. Interrupt From Local APIC Timer May Not Be Detectable While Being Delivered

- Problem: If the local-APIC timer's CCR (current-count register) is 0, software should be able to determine whether a previously generated timer interrupt is being delivered by first reading the delivery-status bit in the LVT timer register and then reading the bit in the IRR (interrupt-request register) corresponding to the vector in the LVT timer register. If both values are read as 0, no timer interrupt should be in the process of being delivered. Due to this erratum, a timer interrupt may be delivered even if the CCR is 0 and the LVT and IRR bits are read as 0. This can occur only if the DCR (Divide Configuration Register) is greater than or equal to 4. The erratum does not occur if software writes zero to the Initial Count Register before reading the LVT and IRR bits.

- Implication: Software that relies on reads of the LVT and IRR bits to determine whether a timer interrupt is being delivered may not operate properly.

- Workaround: Software that uses the local-APIC timer must be prepared to handle the timer interrupts, even those that would not be expected based on reading CCR and the LVT and IRR bits; alternatively, software can avoid the problem by writing zero to the Initial Count Register before reading the LVT and IRR bits.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD17. PCIe\* Root-port Initiated Compliance State Transmitter Equalization Settings May be Incorrect

- Problem: If the processor is directed to enter PCIe Polling.Compliance at 5.0 GT/s or 8.0 GT/s transfer rates, it should use the Link Control 2 Compliance Preset/De-emphasis field (bits [15:12]) to determine the correct de-emphasis level. Due to this erratum, when the processor is directed to enter Polling.Compliance from 2.5 GT/s transfer rate, it retains 2.5 GT/s de-emphasis values.

- Implication: The processor may operate in Polling.Compliance mode with an incorrect transmitter de-emphasis level.

Workaround: None identified.

Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD18. PCIe\* Controller May Incorrectly Log Errors on Transition to RxL0s

- Problem: Due to this erratum, if a link partner transitions to RxL0s state within 20 ns of entering L0 state, the PCIe controller may incorrectly log an error in "Correctable Error Status.Receiver Error Status" field (Bus 0, Device 2, Function 0, 1, 2 and Device 6, Function 0, offset 1D0H, bit 0).

- Implication: Correctable receiver errors may be incorrectly logged. Intel has not observed any functional impact due to this erratum with any commercially available add-in cards.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD19. Unused PCIe\* Lanes May Report Correctable Errors

- Problem: Due to this erratum, during PCIe\* link down configuration, unused lanes may report a Correctable Error Detected in Bus 0, Device 1, Function 0-2, and Device 6, Function 0, Offset 158H, Bit 0.

- Implication: Correctable Errors may be reported by a PCIe controller for unused lanes.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD20. Accessing Physical Memory Space 0-640K through the Graphics Aperture May Cause Unpredictable System Behavior

- Problem: The physical memory space 0-640K when accessed through the graphics aperture may result in a failure for writes to complete or reads to return incorrect results.

- Implication: A hang or functional failure may occur during graphics operation such as OGL or OCL conformance tests, 2D/3D games and graphics intensive application.

- Workaround: It is possible for the BIOS to contain a workaround for this erratum.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD21. PCIe Root Port May Not Initiate Link Speed Change

- Problem: The PCIe Base specification requires the upstream component to maintain the PCIe link at the target link speed or the highest speed supported by both components on the link, whichever is lower. PCIe root port will not initiate the link speed change without being triggered by the software when the root port maximum link speed is configured to be 5.0 GT/s. System BIOS will trigger the link speed change under normal boot scenarios. However, BIOS is not involved in some scenarios such as link disable/re-enable or secondary bus reset and therefore the speed change may not occur unless initiated by the downstream component. This erratum does not affect the ability of the downstream component to initiate a link speed change. All known 5.0Gb/s-capable PCIe downstream components have been observed to initiate the link speed change without relying on the root port to do so.

- Implication: Due to this erratum, the PCIe root port may not initiate a link speed change during some hardware scenarios causing the PCIe link to operate at a lower than expected speed. Intel has not observed this erratum with any commercially available platform.

- Workaround: None identified.

Status: For the steppings affected, see the *Summary Table of Changes*.

# HSD22. Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected

Problem: x87 instructions that trigger #MF normally service interrupts before the #MF. Due to this erratum, if an instruction that triggers #MF is executed while Enhanced Intel SpeedStep<sup>®</sup> Technology transitions, Intel<sup>®</sup> Turbo Boost Technology transitions, or Thermal Monitor events occur, the pending #MF may be signaled before pending interrupts are serviced.

Implication: Software may observe #MF being-signaled before pending interrupts are serviced.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD23. DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/POP SS is Followed by a Store or an MMX Instruction

- Problem: Normally, data breakpoints matches that occur on a MOV SS, r/m or POP SS will not cause a debug exception immediately after MOV/POP SS but will be delayed until the instruction boundary following the next instruction is reached. After the debug exception occurs, DR6.B0-B3 bits will contain information about data breakpoints matched during the MOV/POP SS as well as breakpoints detected by the following instruction. Due to this erratum, DR6.B0-B3 bits may not contain information about data breakpoints matched during the MOV/POP SS when the following instruction is either an MMX instruction that uses a memory addressing mode with an index or a store instruction.

- Implication: When this erratum occurs, DR6 may not contain information about all breakpoints matched. This erratum will not be observed under the recommended usage of the MOV SS,r/m or POP SS instructions (i.e., following them only with an instruction that writes (E/R)SP).

Workaround: None identified.

Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD24. VEX.L is Not Ignored with VCVT\*2SI Instructions

- Problem: The VEX.L bit should be ignored for the VCVTSS2SI, VCVTSD2SI, VCVTTSS2SI, and VCVTTSD2SI instructions, however due to this erratum the VEX.L bit is not ignored and will cause a #UD.

- Implication: Unexpected #UDs will be seen when the VEX.L bit is set to 1 with VCVTSS2SI, VCVTSD2SI, VCVTTSD2SI, and VCVTTSD2SI instructions.

- Workaround: Software should ensure that the VEX.L bit is set to 0 for all scalar instructions.

- Status: For the steppings affected, see the *Summary Table of Changes*.

- HSD25. Certain Local Memory Read / Load Retired PerfMon Events May Undercount

- Problem: Due to this erratum, the Local Memory Read / Load Retired PerfMon events listed below may undercount.

MEM\_LOAD\_RETIRED.L3\_HIT MEM\_LOAD\_RETIRED.L3\_MISS MEM\_LOAD\_L3\_HIT\_RETIRED.XSNP\_MISS MEM\_LOAD\_L3\_HIT\_RETIRED.XSNP\_HIT MEM\_LOAD\_L3\_HIT\_RETIRED.XSNP\_HITM MEM\_LOAD\_L3\_HIT\_RETIRED.XSNP\_NONE MEM\_LOAD\_L3\_MISS\_RETIRED.LOCAL\_DRAM MEM\_LOAD\_L4\_RETIRED.LOCAL\_HIT MEM\_TRANS\_RETIRED.LOAD\_LATENCY

- Implication: The affected events may undercount, resulting in inaccurate memory profiles. Intel has observed undercounts as much as 40%.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

- HSD26. Specific Graphics Blitter Instructions May Result in Unpredictable Graphics Controller Behavior

- Problem: Specific source-copy blitter instructions in Intel<sup>®</sup> HD Graphics 4600 Processor may result in unpredictable behavior when a blit source and destination overlap.

- Implication: Due to this erratum, the processor may exhibit unpredictable graphics controller behavior. Intel has not observed this erratum with any commercially available software.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

- HSD27. Processor May Enter Shutdown Unexpectedly on a Second Uncorrectable Error

- Problem: If an IA32\_MCi\_STATUS MSR contains an uncorrectable error with MCACOD=0x406 and a second uncorrectable error occurs after warm reset but before the first error is cleared by zeroing the IA32\_MCi\_STATUS MSR, a shutdown will occur.

- Implication: When this erratum occurs, the processor will unexpectedly shut down instead of executing the machine check handler.

- Workaround: None identified. Software should clear IA32\_MCi\_STATUS MSRs as early as possible to minimize the possibility of this erratum occurring.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD28. Modified Compliance Patterns for 2.5 GT/s and 5 GT/s Transfer Rates Do Not Follow PCIe\* Specification

Problem: The PCIe controller does not produce the PCIe specification defined sequence for the Modified Compliance Pattern at 2.5 GT/s and 5 GT/s transfer rates. This erratum is not seen at 8 GT/s transfer rates.

Implication: Normal PCIe operation is unaffected by this erratum.

Workaround: None identified.

Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD29. Performance Monitor Counters May Produce Incorrect Results

Problem: When operating with SMT enabled, a memory at-retirement performance monitoring event (from the list below) may be dropped or may increment an enabled event on the corresponding counter with the same number on the physical core's other thread rather than the thread experiencing the event. Processors with SMT disabled in BIOS are not affected by this erratum.

The list of affected memory at-retirement events is as follows: MEM\_UOP\_RETIRED.LOADS MEM UOP RETIRED.STORES MEM UOP RETIRED.LOCK MEM\_UOP\_RETIRED.SPLIT MEM UOP RETIRED.STLB MISS MEM LOAD UOPS RETIRED.HIT LFB MEM\_LOAD\_UOPS\_RETIRED.L1\_HIT MEM\_LOAD\_UOPS\_RETIRED.L2\_HIT MEM LOAD UOPS RETIRED.LLC HIT MEM LOAD UOPS MISC RETIRED.LLC MISS MEM LOAD UOPS LLC HIT RETIRED.XSNP HIT MEM LOAD UOPS LLC HIT RETIRED.XSNP HITM MEM\_LOAD\_UOPS\_LLC\_HIT\_RETIRED.XSNP\_MISS MEM LOAD UOPS LLC HIT RETIRED.XSNP NONE MEM LOAD UOPS RETIRED.LLC MISS MEM LOAD UOPS LLC MISS RETIRED.LOCAL DRAM MEM\_LOAD\_UOPS\_LLC\_MISS\_RETIRED.REMOTE\_DRAM MEM LOAD UOPS RETIRED.L2 MISS

- Implication: Due to this erratum, certain performance monitoring event will produce unreliable results during hyper-threaded operation.

- Workaround: None identified.

Status: For the steppings affected, see the Summary Table of Changes.

#### HSD30. Performance Monitor UOPS\_EXECUTED Event May Undercount

- Problem: The performance monitor event UOPS\_EXECUTED (Event B1H, any Unmask) should count the number of UOPs executed each cycle. However due to this erratum, when eight UOPs execute in one cycle, these UOPs will not be counted.

- Implication: The performance monitor event UOPS\_EXECUTED may reflect a count lower than the actual number of events.

- Workaround: None identified.

#### Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD31. MSR\_PERF\_STATUS May Report an Incorrect Core Voltage

- Problem: The core operating voltage can be determined by dividing MSR\_PERF\_STATUS MSR (198H) bits [47:32] by 2^13. However, due to this erratum, this calculation may report half the actual core voltage.

- Implication: The core operating voltage may be reported incorrectly.

- Workaround: It is possible for the BIOS to contain a workaround for this erratum.

- Status: For the steppings affected, see the *Summary Table of Changes*.

# HSD32. PCIe\* Atomic Transactions From Two or More PCIe Controllers May Cause Starvation

- Problem: On a Processor PCIe controller configuration in which two or more controllers receive concurrent atomic transactions, a PCIe controller may experience starvation which eventually can lead to a completion timeout.

- Implication: Atomic transactions from two or more PCIe controllers may lead to a completion timeout. Atomic transactions from only one controller will not be affected by this erratum. Intel has not observed this erratum with any commercially available device.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD33. The Corrected Error Count Overflow Bit in IA32\_ MC0\_STATUS is Not Updated After a UC Error is Logged

- Problem: When a UC (uncorrected) error is logged in the IA32\_MC0\_STATUS MSR (401H), corrected errors will continue to update the lower 14 bits (bits 51:38) of the Corrected Error Count. Due to this erratum, the sticky count overflow bit (bit 52) of the Corrected Error Count will not get updated after a UC error is logged.

- Implication: The Corrected Error Count Overflow indication will be lost if the overflow occurs after an uncorrectable error has been logged.

- Workaround: None identified.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD34. An AVX Gather Instruction That Causes an EPT Violation May Not Update Previous Elements

Problem: When execution of an AVX gather instruction causes an EPT (extended page table) violation due to a specific element, all previous elements should be complete. Due to this erratum, such an execution may fail to complete previous elements. In addition, the instruction's mask operand is not updated. This erratum applies only if the EPT violation occurs while updating an accessed or dirty flag in a paging-structure entry. Instructions impacted by this erratum are: VGATHERDPS, VGATHERDPD, VGATHERQPS, VGATHERQPD, VPGATHERDD, VPGATHERDQ, VPGATHERQD, and VPGATHERQQ.

Implication: This erratum may prevent a gather instruction from making forward progress.

- Workaround: It is possible for the BIOS to contain a workaround for this erratum.

- Status: For the steppings affected, see the *Summary Table of Changes*.

#### HSD35. PLATFORM\_POWER\_LIMIT MSR Not Visible

- Problem: The PLATFORM\_POWER\_LIMIT MSR (615H) is used to control the PL3 (power limit 3) mechanism of the processor. Due to this erratum, this MSR is not visible to software.