# Non-Volatile Memory Data Book

# NON-VOLATILE MEMORY DATA BOOK

# TABLE OF CONTENTS

# Section 1 Read Only Memories

General Instrument Microelectronics offers a complete line of reliable mask programmed, Read Only Memories, manufactured in both NMOS and CMOS processes. These memory products are fully static and range in density from 16K bits to 1 megabit.

# Section 2 <u>Electrically Erasable Programmable</u> Read Only Memories

General Instrument Microelectronics offers a broad line of highly reliable +5V only, N-channel, utility EEPROMs including parallel access, serial access and Inter-Integrated Circuit (I<sup>2</sup>C) compatible devices. Application - specific EEPROMs, including a nonvolatile counter and a microcomputer with on-board EEPROM memory, are also available in both commercial and industrial temperature ranges.

# Section 3 Sales Offices

Worldwide field sales offices are located throughout the U.S., Europe and Asia. Contact the office nearest you for further information regarding General Instrument Microelectronics products.

# SECTION 1

# READ ONLY MEMORIES

| Description                    | Part<br>Number              | Page<br>Number     |

|--------------------------------|-----------------------------|--------------------|

| 32K ROM organized 4K x 8       | R09432<br>R09433            | 1-3<br>1-6         |

| 64K ROM organized 8K x 8       | R09464<br>R094164<br>R09864 | 1-9<br>1-9<br>1-12 |

| 128K ROM organized 16K x 8     | R09128                      | 1-16               |

| 256K ROM organized 32K x 8     | R09256<br>R0C256            | 1-22<br>1-28       |

| 512K ROM organzied 64K x 8     | R09512X<br>R0C512X          | 1-34<br>1-41       |

| Megabit ROM organized 128K x 8 | R09100X<br>R0C100X          | 1-48<br>1-55       |

# 32,768 BIT STATIC READ ONLY MEMORY

#### FEATURES:

- 4096 x 8 organization

- Fully static operation no clocks required

- Single +5V +10% supply

- 450ns access time: R09432B

- 300ns access time: R094320

- 250ns access time: R09432DS

- 200ns access time: R09432D

- Inputs and outputs TTL compatible

- Three state outputs under the control of two mask programmable chip select inputs

- Output drive capability of 2 TTL loads 100pf

- Low power dissipation

- Totally automated custom programming

- Pin compatible with 2532 EPROM

- ESD protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD883

| PIN CONFIGUE |               |                                   |

|--------------|---------------|-----------------------------------|

| 24 LEAD DUAL | -IN-LINE      |                                   |

|              |               |                                   |

|              | Тор           | View                              |

|              | A7            | 24 <b>0</b> V <sub>CC</sub> (+5V) |

|              | A6 🗖 2        | 23 A8                             |

|              | A5 <b>L</b> 3 | 22 <b>D</b> A9                    |

|              | A4 🗖 4        | 21 CS2/CS2                        |

|              | A305          | 20 CS1/CS1                        |

|              | A2 16         | 19 <b>5</b> A10                   |

|              |               | 18 <b>0</b> A11                   |

|              | AO CB         | 17 08                             |

|              |               | 16 07                             |

|              |               |                                   |

|              |               | 15 06                             |

|              | 03□11         | 14 🗖 05                           |

|              | GND 🗖 12      | 1304                              |

|              | L             |                                   |

|              |               |                                   |

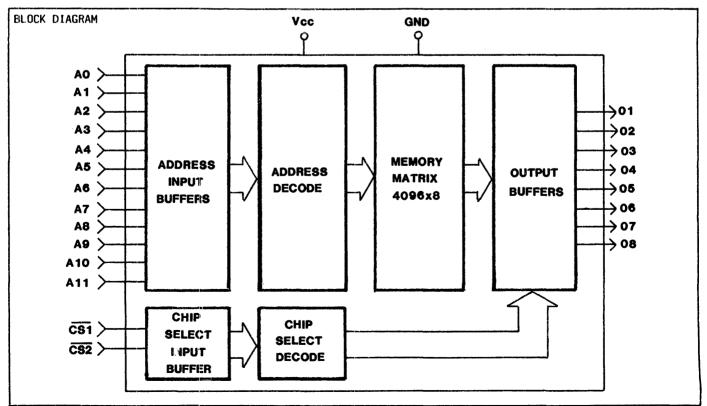

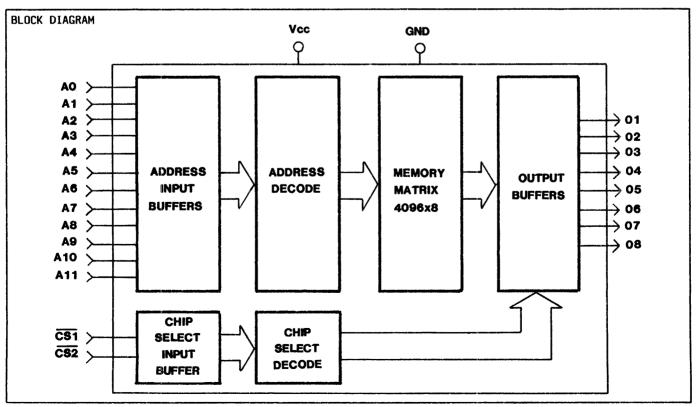

# DESCRIPTION

The R09432 is a 32,768 bit fully static Read Only Memory utilizing MOS N-Channel Silicon Gate Ion Implanted technology. It is organized 4096 words by 8 bits and operates from a single +5 Volt power supply with  $\pm 10\%$  supply tolerance. All inputs are TIL compatible, and the three-state outputs can drive two standard TIL loads each.

# Maximum Ratings\*

$V_{\mbox{CC}}$  and Inut Voltages (with Respect

Storage Temperature..... -65°C to +150°C

Standard Conditions (unless otherwise noted):  $V_{CC} = +5V + 10\%$ Operating Temperature  $T_A = 0^{\circ}C$  to +70°C Output Loading Two TTL Loads +  $C_L$  TOTAL = 100pf

# DC CHARACTERISTICS

\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied - operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics                                                                                                                                              | Sym                                           | Min                          | Тур | Max                                                                  | Units                                     | Conditions                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------|-----|----------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Low Voltage<br>Input High Voltage<br>Input Load Current<br>Output Low Voltage<br>Output High Voltage<br>Output Leakage Current<br>Power Supply Current | VIL<br>VIH<br>IIL<br>VOL<br>VOH<br>ILO<br>ICC | -0.5<br>2.0<br>-<br>2.4<br>- |     | 0.8<br>V <sub>CC</sub><br>10<br>0.40<br>V <sub>CC</sub><br>10<br>100 | ۷<br>۷<br>۹<br>۷<br>۷<br>۹<br>۹<br>۳<br>۹ | $V_{IN} = 0.4V$ to $V_{CC}$<br>$I_{OL} = +3.2mA$<br>$I_{OH} = -200\mu A$<br>$V_{OUT} = 0.4V$ to $V_{CC}$<br>All Inputs +5.5V,<br>Outputs Loaded |

# AC CHARACTERISTICS

|                         |                  | R094 | 432B | R09 | 432C | R094 | 32DS | R09 | 432D |       |                             |

|-------------------------|------------------|------|------|-----|------|------|------|-----|------|-------|-----------------------------|

| Characteristic          | Sym              | Min  | Max  | Min | Max  | Min  | Max  | Min | Max  | Units | Conditions                  |

| Address Access Time     | t <sub>ACC</sub> |      | 450  | -   | 300  | -    | 250  | _   | 200  | ns    |                             |

| Chip Select Access Time |                  | -    | 150  | -   | 100  | -    | 85   | -   | 70   | ns    |                             |

| Chip Deselect Time      | tOFF             | -    | 150  | -   | 100  | -    | 85   | -   | 70   | ns    |                             |

| Output Hold After       |                  |      |      |     |      |      |      |     |      |       |                             |

| Address Change          | t <sub>OH</sub>  | 10   | - 1  | 10  | -    | 10   | -    | 10  | -    | ns    |                             |

| Capacitance**           |                  |      |      |     |      |      |      | ł   |      |       |                             |

| Input Capacitance       | c <sub>in</sub>  | -    | 7    | -   | 7    | -    | 7    | -   | 7    | pf    | T <sub>A</sub> =25°C,F=1MHz |

| Output Capacitance      | с <sub>оит</sub> | -    | 10   | -   | 10   | -    | 10   | -   | 10   | pf    | T <sub>A</sub> =25°C,F=1MHz |

\*\*Capacitance is periodically samples and is not 100% tested.

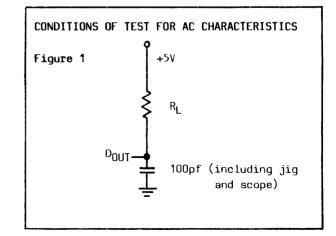

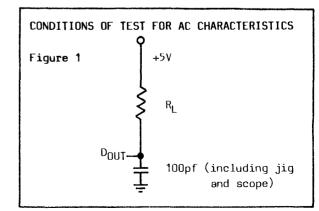

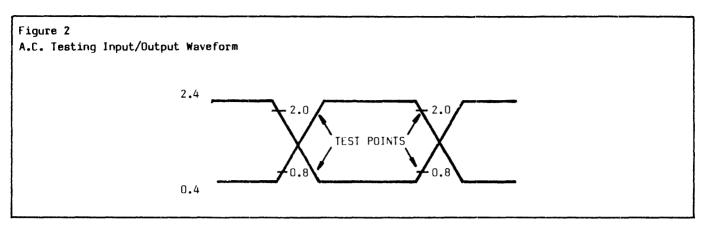

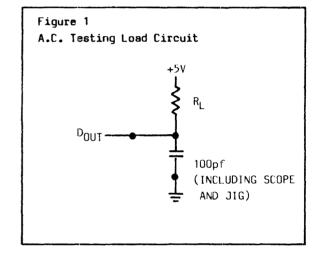

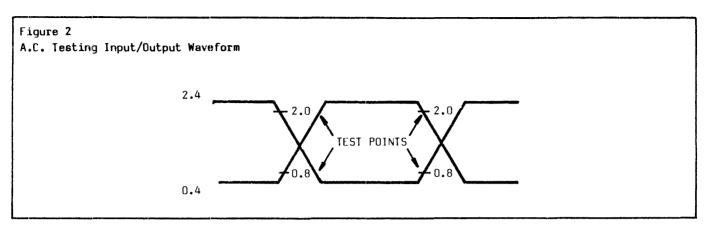

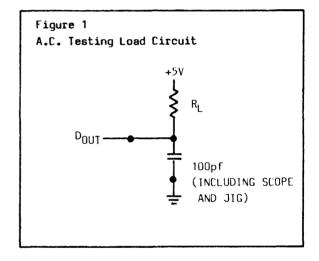

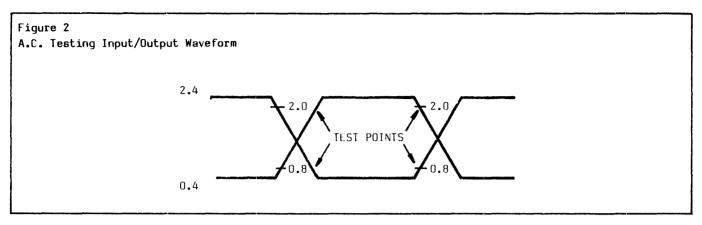

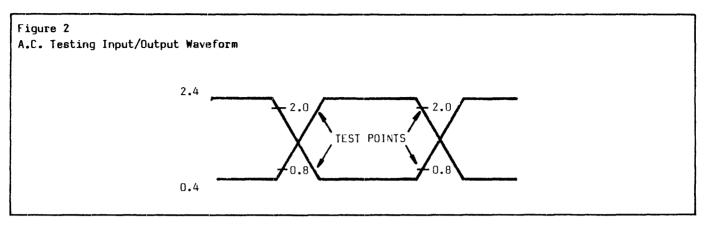

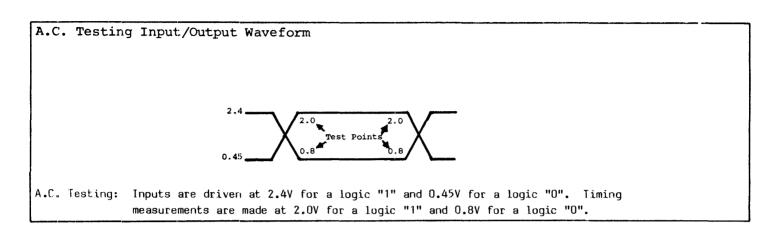

# AC TEST CONDITIONS

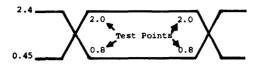

| Input Pulse Levels               | 0.4V to     | 2.4V  |

|----------------------------------|-------------|-------|

| Input Rise and Fall Times        | • • • • • • | 10ns  |

| Timing Measurement Levels:       |             |       |

| Input                            |             | 1.5V  |

| Output                           | 0.8V to     | 2.0V  |

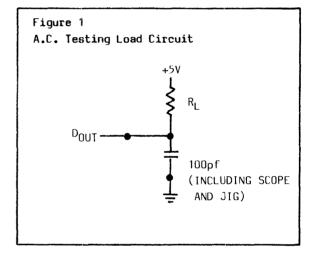

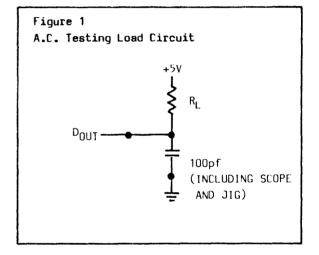

| Output Load 2TTL Loads +100pf (S | ee Figur    | re 1) |

#### 32,768 BIT STATIC READ ONLY MEMORY

### FEATURES:

- 4096 x 8 organization

- Fully static operation no clocks required

- Single +5V +10% supply

- 450ns access time: R09433B

- 300ns access time: R09433C

- 250ns access time: R09433DS

- 200ns access time: R09433D

- Inputs and outputs TTL compatible

- Three state outputs under the control of two mask programmable chip select inputs

- Output drive capability of 2 TTL loads 100pf

- Low power dissipation

- Totally automated custom programming

- Pin compatible with 2732 EPROM

- ESD protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD 883

|             | Top View |                          |

|-------------|----------|--------------------------|

| A7 🗖        | •1       | 24 V <sub>CC</sub> (+5V) |

| A6 🗖        | 2        | 23 🗖 A8                  |

| A5 <b>C</b> | 3        | 22 🗖 A9                  |

| A4 C        | 4        | 21 A11                   |

| A3 <b>C</b> | 5        | 20 CS1/CS1               |

| A2 🕻        | 6        | 19 <b>D</b> A10          |

| A1 <b>C</b> | 7        | 18 CS2/CS2               |

| A0 🖸        | 8        | 17 🗖 08                  |

| 01 <b>C</b> | 9        | 16 🗖 07                  |

| 02 🗖        | 10       | 15 🗖 06                  |

| 030         | 11       | 14 🗖 05                  |

| GND C       | 12       | 1304                     |

#### DESCRIPTION

The R09433 is a 32,768 bit fully static Read Only Memory utilizing MOS N-Channel Silicon Gate Ion Implanted technology. It is organized 4096 words by 8 bits and operates from a single +5 Volt power supply with  $\pm 10\%$  supply tolerance. All inputs are [[L compatible, and the three-state outputs can drive two standard [[L loads each.

# Maximum Ratings\*

V<sub>CC</sub> and Inut Voltages (with Respect to GND)..... -0.5V to +7.0V Storage Temperature..... -65°C to +150°C

**Standard Conditions** (unless otherwise noted):  $V_{CC} = +5V \pm 10\%$ Operating Temperature  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ Output Loading Two TTL Loads  $+ C_L$  TOTAL = 100pf

# DC CHARACTERISTICS

\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied - operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics       | Sym             | Min | Тур | Max             | Units | Conditions                            |

|-----------------------|-----------------|-----|-----|-----------------|-------|---------------------------------------|

| Address, CHIP SELECTS |                 |     |     |                 |       |                                       |

| Inputs                |                 |     |     |                 |       |                                       |

| Logic "1"             | V <sub>IH</sub> | 2.0 | -   | V <sub>CC</sub> | V     |                                       |

| Logic "O"             | ۷ <sub>IL</sub> | 0   | -   | 0.8             | v     |                                       |

| Leakage               | ILI             | -   | -   | 10              | Aىر   | $V_{\rm IN} = 0.4V \ tp \ V_{\rm CC}$ |

| Data Outputs          |                 |     |     |                 |       |                                       |

| Logic "1"             | V <sub>OH</sub> | 2.4 | -   | V <sub>CC</sub> | V     | I <sub>OH</sub> = -200µА              |

| Logic "O"             | V <sub>OL</sub> | -   | -   | 0.4             | v     | $I_{OL} = 3.2 \text{mA}$              |

| Leakage               | ILO             | -   | -   | 10              | Au    | $V_{OUT} = 0.4V$ to $V_{CC}$          |

| Power Supply Current  | ICC             | -   | -   | 100             | mA    | All inputs +5.5V,                     |

|                       |                 |     |     |                 |       | Outputs Unloaded                      |

| AC CHARACTERISTICS              |                  |     |             |      |             |      |      |      |      |       |                             |

|---------------------------------|------------------|-----|-------------|------|-------------|------|------|------|------|-------|-----------------------------|

|                                 |                  | R09 | <u>433B</u> | R094 | <u>433C</u> | R094 | 33DS | R094 | 433D |       |                             |

| Characteristic                  | Sym              | Min | Max         | Min  | Max         | Min  | Max  | Min  | Max  | Units | Conditions                  |

| Address Access Time             | tACC             | -   | 450         | -    | 300         | -    | 250  | _    | 200  | ns    |                             |

| Chip Select Access Time         | t <sub>ACS</sub> |     | 150         | -    | 100         | -    | 85   | -    | 70   | ns    |                             |

| Chip Deselect Time              | tOFF             | -   | 150         | -    | 100         | -    | 85   | -    | 70   | ns    |                             |

| Output Hold After               |                  |     |             |      |             |      |      |      |      |       |                             |

| Address Change<br>Capacitance** | <sup>t</sup> он  | 10  |             | 10   | -           | 10   | -    | 10   | -    | ns    |                             |

| Input Capacitance               | C <sub>IN</sub>  |     | 7           | -    | 7           | -    | 7    | -    | 7    | pf    | T <sub>A</sub> =25°C,F=1MHz |

| Output Capacitance              | C <sub>OUT</sub> | -   | 10          | -    | 10          | -    | 10   |      | 10   | pf    | T <sub>A</sub> =25°C,F=1MHz |

\*\*Capacitance is periodically sampled and is not 100% tested.

# AC TEST CONDITIONS

| Input Pulse Levels 0.4V to 2.4V              |

|----------------------------------------------|

| Input Rise and Fall Times 10ns               |

| Timing Measurement Levels:                   |

| Input 1.5V                                   |

| Output 0.8V to 2.0V                          |

| Output Load 2TTL Loads +100pf (See Figure 1) |

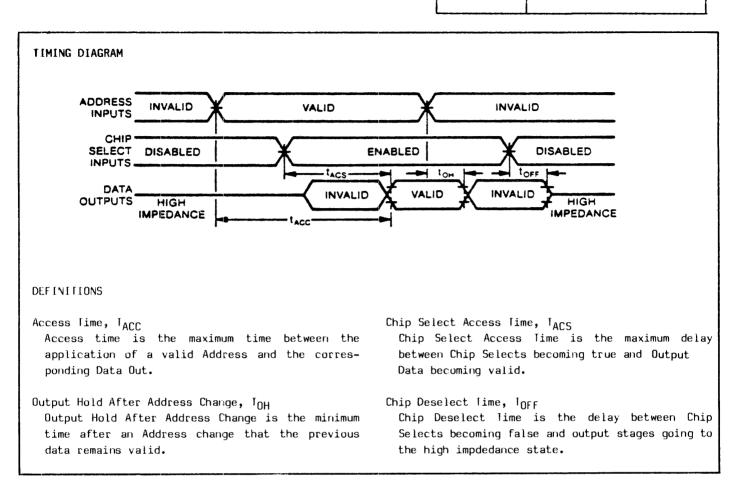

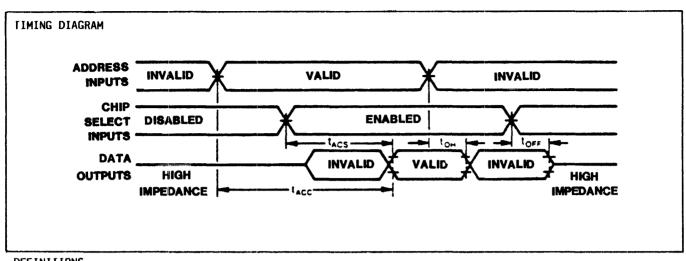

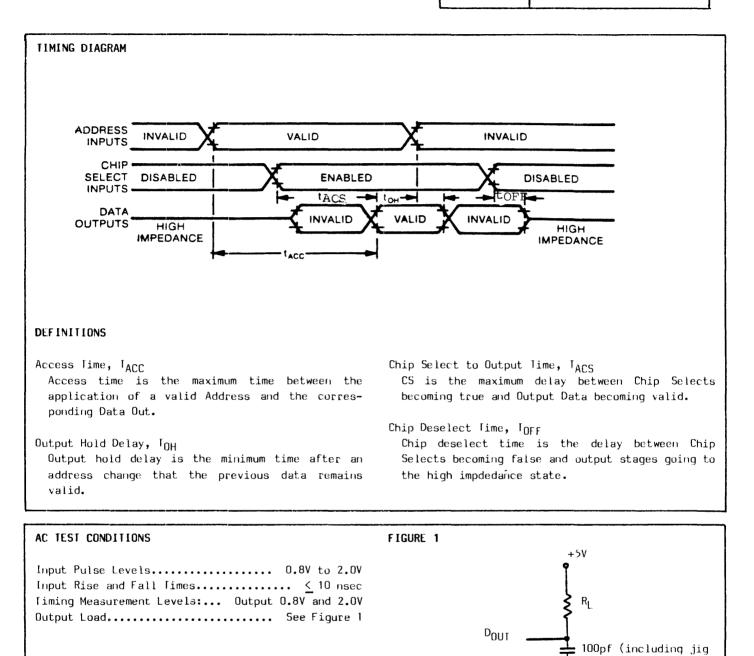

Access Time, TACC

Access time is the maximum time between the application of a valid Address and the corresponding Data Out.

# Output Hold After Address Change, ${\rm T}_{\rm OH}$

Output Hold After Address Change is the minimum time after an Address change that the previous data remains valid. Chip Select Access Time, T<sub>ACS</sub>

Chip Select Access Time is the maximum delay between Chip Selects becoming true and and Output Data becoming valid.

Chip Deselect Time, T<sub>OFF</sub>

Chip Deselect Time is the delay between Chip Selects becoming false and output stages going to the high impdedance state.

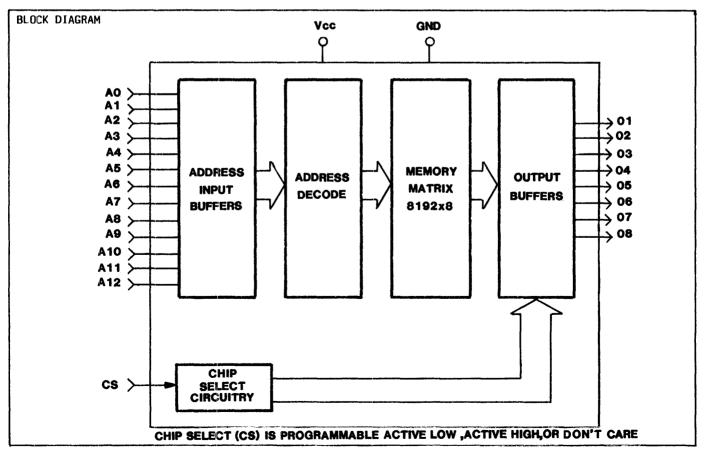

# 65,536 BIT STATIC READ ONLY MEMORY

# FEATURES:

- 8192 x 8 organization

- Fully static operation

- Single +5V ±10% / ±5% supply (R094164)

- Inputs and outputs IIL compatible

- Three state outputs

- Output drive capability of 2 TTL/1 TTL Load and 100pf

- 24 pin JEDEC approved pinout

- LSD protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-SID883

## DESCRIPTION

The General Instrument R09464 and R094164 Series are 65,536 Bit Static Read Only Memories organized as 8192 eight-bit words and are ideally suited for microprocessor memory applications. Fabricated with General Instrument N-Channel Silicon Gate technology, the R09464 and R094164 Series provide the designer with a high performance, easy to use MOS circuit featuring operation from a single +5

| PIN CONFIGURATION    |               |                             |

|----------------------|---------------|-----------------------------|

| 24 LEAD DUAL-IN-LINE |               |                             |

|                      |               |                             |

| R09464/R094164       |               |                             |

| _                    | Top View      |                             |

| A7 <b>C</b> •        | $1  \bigcirc$ | 24 <b>-</b> V <sub>CC</sub> |

| A6 🗖 2               |               | 2 <b>3</b> A8               |

| A5 <b>C</b> 3        | ,             | 22 <b>D</b> A9              |

| A4 <b>C</b> 4        |               | 21 <b>D</b> A12             |

| A3 <b>C</b> 5        |               | 20 <b>–</b> CS              |

| A2 🗖 6               |               | 19 <b>D</b> A10             |

| A1 🗖 7               |               | 18 <b>D</b> A11             |

| AO 🗖 8               | ;             | 170 08                      |

| 01 🗖 9               |               | 160 07                      |

| 02 🗖 1               | 0             | 150 06                      |

| 03 🗖 1               | 1             | 140 05                      |

| GND 🗖 1              | 2             | 130 04                      |

|                      |               |                             |

volt power supply and low power dissipation. The R09464 and R094164 Series offer the best combination of high performance, large bit storage and simple interfacing of any MOS Read Only Memory available today.

1984 General Instrument Corporation

# Maximum Ratings\*

| .0    | und / . |       |      |       |      | •••• |             | 0.71              | 11.01 |

|-------|---------|-------|------|-------|------|------|-------------|-------------------|-------|

| Power | Diss    | ipati | lon. | • • • | •••• | •••  | • • • • • • | • • • • • • • • • | 1.OW  |

**Standard Conditions** (unless otherwise noted): Operating Temperature  $\Gamma_A = 0^{\circ}C$  to  $+70^{\circ}C$  $V_{CC} = +5V \pm 10\% / \pm 5\%$  (R094164) \*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied - operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

# DC CHARACTERISTICS

| Characteristics          | Sym             | Min | Гур | Max             | Units | Conditions                                     |

|--------------------------|-----------------|-----|-----|-----------------|-------|------------------------------------------------|

| Output High Level        | v <sub>он</sub> | 2.4 | -   | v <sub>cc</sub> | v     | I <sub>OH</sub> = –200µA/–100µA (R094164)      |

| Output Low Level         | V <sub>OL</sub> | -   | -   | 0.4             | v     | I <sub>OL</sub> = 3.2mA/1.6mA (R094164)        |

| Input High Level         | VIH             | 2.0 | -   | V <sub>CC</sub> | V     |                                                |

| Input Low Level          | V <sub>IL</sub> | -   | -   | 0.8             | v     |                                                |

| Input Leakage Current    | ILI             | -   | -   | 10              | Aىر   | $V_{\rm IN} = 0.4V$ to $V_{\rm CC}$            |

| Output Leakage Current   | ILO             | -   | -   | 10              | Aىر   | $V_{OUI} = 0.4V$ to $V_{CC}$                   |

| Operating Supply Current | I <sub>CC</sub> | -   | -   | 100             | mA    | Note 1, V <sub>OUF</sub> = 5.5/5.25V (R094164) |

| AC CHARACTERISTICS      |                  | R094 | 64B   | R094 | 64CS  | R094 | 64C                                     | R094 | 64DS |       |                                   |

|-------------------------|------------------|------|-------|------|-------|------|-----------------------------------------|------|------|-------|-----------------------------------|

|                         |                  | R094 | 164B  | R094 | 164CS | R094 | 164C                                    |      |      |       |                                   |

| Characteristics         | Sym              | Min  | Max   | Min  | Max   | Min  | Max                                     | Min  | Max  | Units | Conditions                        |

| Address Access [ime     | tacc             | -    | 450   | -    | 350   | -    | 300                                     | _    | 250  | ns    |                                   |

| Output Hold After       | "ALL             |      | 1.2 0 |      |       |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |      |       |                                   |

| Address Change          | t <sub>OH</sub>  | 10   | -     | 10   | -     | 10   | -                                       | 10   | -    | ns    | Note 2                            |

| Chip Select Access Time | t <sub>ACS</sub> | -    | 150   | -    | 125   | -    | 100                                     | -    | 100  | กร    |                                   |

| Output Disable Time     | tOFF             | -    | 150   | -    | 125   | -    | 100                                     | -    | 100  | ns    |                                   |

| Capacitance**           |                  |      |       |      |       |      |                                         |      |      |       |                                   |

| Input Capacitance       | C1               | -    | 7     | _    | 7     | -    | 7                                       | -    | 7    | pf    | $F=1.0MHz$ , $\Gamma_{A} = +25°C$ |

| Output Capacitance      | с <sub>О</sub>   | -    | 10    | -    | 10    | -    | 10                                      | -    | 10   | pf    | F=1.0MHz, $T_A = +25$ °C          |

\*\*Capacitance is periodically sampled and is not 100% tested.

# NOTES:

1. Measured with device selected and outputs unloaded.

2. This parameter is periodically sampled and is not 100% tested.

| PART NUMBER | MAXIMUM ACCESS TIME | V <sub>CC</sub> SUPPLY TOLERANCE | TTL LOADS |

|-------------|---------------------|----------------------------------|-----------|

| R094164B    | 450ns               | 5%                               | 1         |

| R094164CS   | 350ns               | 5%                               | 1         |

| R094164C    | 300ns               | 5%                               | 1         |

| R09464B     | 450ns               | 10%                              | 2         |

| R09464CS    | 350ns               | 10%                              | 2         |

| R09464C     | 300ns               | 10%                              | 2         |

| R09464DS    | 250ns               | 1 0%                             | 2         |

and scope)

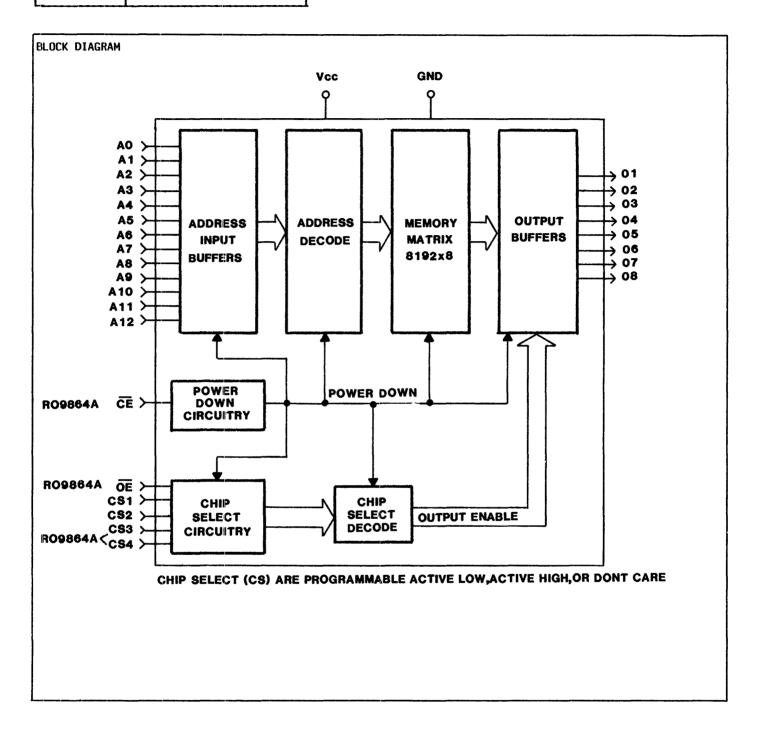

# 65,536 BIT STATIC READ ONLY MEMORY

#### FEATURES:

- 8192 x 8 organization

- Fully static operation

- Single +5V  $\pm$  10% supply

- Inputs and outputs TIL compatible

- Three state outputs

- ~ 28 pin JEDEC approved pinout (R09864A)

- ESD protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD883

# DESCRIPTION

The General Instrument R09864 and R09864A series are 65,536 bit static read only memories organized as 8192 eight-bit words and are ideally suited for microprocessor memory applications fabricated with General Instrument N-channel silicon gate technology, the R09864 and R09864A series provide the designer with a high performance, easy to use MOS circuit featuring operation from a single +5 volt power supply and a low power dissipation. The R09864 and R09864A series offer the best combination of high performance, large bit storage and simple interfacing of any MOS read only memory available today.

The R09864 series provides four fully programmable chip selects (CS3 and CS4 are on Pins 22 and 20 respectively) which enables a memory system to contain up to sixteen R09864s without using any external address decode circuitry.

The R09864A series offers an automatic down feature. Power down is controlled by Pin 20, the Chip Enable (CE) input. When CE goes high, the device will power down and remain in a low power standby mode as long as CE remains high. Pin 22 provides the Output Enable (OE) function allowing additional bus control.

| R09864  | Тор                 | View                             |

|---------|---------------------|----------------------------------|

|         |                     | 28 V <sub>CC</sub>               |

|         |                     | 27 <b>0</b> CS1                  |

|         | A7 0 3              | 26 <b>D</b> CS2                  |

|         | A6 🗖 4              | 25 A8                            |

|         | A5 🗖 5              | 24 🗖 A9                          |

|         | A4 🗖 6              | 23 🗖 A11                         |

|         | A3 🗖 7              | 22 🗖 CS 3                        |

|         | A2 🗖 8              | 21 🗖 A10                         |

|         | A1 🗗 9              | 20 🗖 CS4                         |

|         | AO 🗖 10             | 19 🗖 08                          |

|         | 01 🗖 11             | 1807                             |

|         | 02 🗖 12             | 17 2 06                          |

|         | 03 🗖 13             | 16 🗖 05                          |

|         | GND <b>[</b> 14     | 15 04                            |

| R09864A | Тор                 | View                             |

|         |                     | 28 V <sub>CC</sub>               |

|         | A12 02              | 27 <b>D</b> CS 1                 |

|         | A7 🗖 3              | 26 DCS2                          |

|         | A6 🗖 4              | 25 🗖 A8                          |

|         | A5 🗖 5              | 24 🗖 A9                          |

|         | A4 🗖 6              | 23 <b>D</b> A11                  |

|         | A3 🖸 7              | 22 <mark>-</mark> OE             |

|         | A2 🗖 8              | 21 🗖 A 10                        |

|         | A1 <b>C</b> 9       | 20 D CE                          |

|         |                     | 19 08                            |

|         |                     | 18 07                            |

|         | 02 🗖 12             | 17 06                            |

|         | 0.1.00 1.1          |                                  |

|         | 03 🗖 13<br>GND 🗖 14 | 16 <b>ם</b> 05<br>15 <b>ם</b> 04 |

# Maximum Ratings\*

| Storage Temperature                  | -65°C to +150°C |

|--------------------------------------|-----------------|

| V <sub>CC</sub> and Applied Voltages |                 |

| (with respect to GND)                | -0.5V to +7.0V  |

| Power Dissipation                    | 1.OW            |

**Standard Conditions** (unless otherwise noted): Operating Temperature  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  $V_{CC} = +5V \pm 10\%$  \*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied - operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### DC CHARACTERISTICS

| Characteristics          | Sym             | Min  | Тур | Max             | Units | Conditions                   |

|--------------------------|-----------------|------|-----|-----------------|-------|------------------------------|

| Output High Level        | V <sub>OH</sub> | 2.4  | -   | v <sub>cc</sub> | v     | I <sub>OH</sub> = -200µА     |

| Output Low Level         | V <sub>OL</sub> | -    | -   | 0.4             | V     | $I_{OL} = 3.2 \text{mA}$     |

| Input High Level         | ٧ <sub>IH</sub> | 2.0  | -   | V <sub>CC</sub> | V     |                              |

| Input Low Level          | VIL             | -0.5 | -   | 0.8             | V     |                              |

| Input Leakage Current    | ILI             | - 1  | - 1 | 10              | Aىر   | $V_{IN} = 0.4V$ to $V_{CC}$  |

| Output Leakage Current   | ILO             | -    | -   | 10              | Au    | $V_{OUT} = 0.4V$ to $V_{CC}$ |

| Operating Supply Current | ICC             | -    | -   | 100             | mA    | Note 1                       |

| Standby Supply Current   | ISB             | -    | -   | 12              | mA    | Note 2                       |

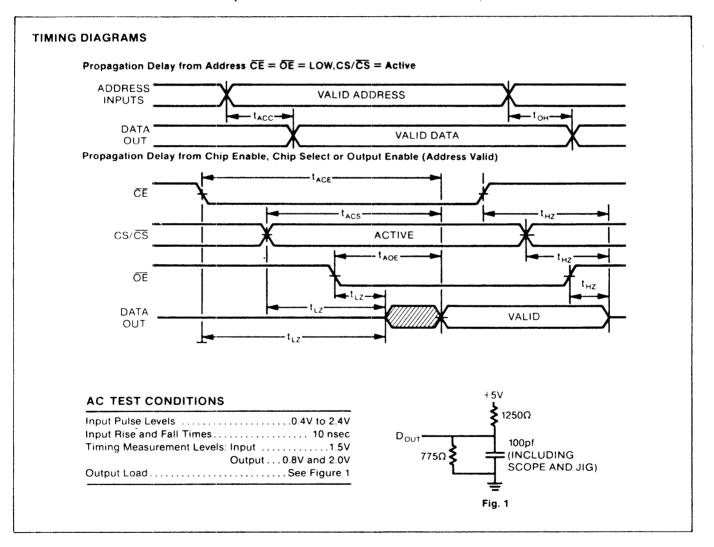

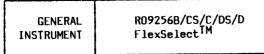

# AC CHARACTERISTICS

|                                          |                 | R098<br>R098 |     | R098<br>R098 | 64CS<br>64ACS | R098<br>R098 |     | R098<br>R098 | 64DS<br>64ADS | R098<br>R098 |     |       |            |

|------------------------------------------|-----------------|--------------|-----|--------------|---------------|--------------|-----|--------------|---------------|--------------|-----|-------|------------|

| Characteristic                           | Sym             | Min          | Max | Min          | Max           | Min          | Max | Min          | Max           | Min          | Max | Units | Conditions |

| Address Access Time<br>Output Hold After | tacc            | -            | 450 | -            | 350           | -            | 300 | -            | 250           | -            | 200 | ns    |            |

| Address Change                           | t <sub>OH</sub> | 10           | -   | 10           | -             | 10           | -   | 10           | -             | 5            | -   | ns    |            |

| Chip Enable Access Time                  | tACE            | -            | 450 | -            | 350           | -            | 300 | -            | 250           | -            | 200 | ns    | Note 3     |

| Chip Select Access Time                  | tACS            | -            | 150 | -            | 125           | -            | 100 | -            | 100           | -            | 85  | ns    |            |

| Output Enable Access Time                | tADE            | -            | 150 | -            | 125           | -            | 100 | -            | 100           | -            | 85  | ns    | Note 3     |

| Output Low Z Delay                       | tLZ             | 10           | -   | 10           | -             | 10           | -   | 10           | -             | 5            | -   | ns    | Note 4     |

| Output High Z Delay                      | t <sub>HZ</sub> | -            | 150 |              | 125           | -            | 100 | -            | 85            | -            | 85  | ns    | Note 5     |

#### NOTES:

1. Measured with device selected and outputs unloaded.

2. Applies to "A" versions only and measured with  $\overline{\text{CE}}$  = 2.0V.

3. Applies to "A" versions only.

- 4. Output low impedance delay ( $t_{LZ}$ ) is measured from  $\overline{CE}$  and  $\overline{OE}$  going low and  $\overline{CS}$  going active, whichever occurs last.

- 5. Output high impedance delay ( $t_{HZ}$ ) is measured from either  $\overline{CE}$  or  $\overline{OE}$  going high or  $\overline{CS}$  going inactive, whichever occurs first.

R09864B/CS/C/DS/D R09864AB/ACS/AC/ADS/AD

| PART<br>NUMBER | MAXIMUM<br>ACCESS TIME | OPERATING<br>CURRENT | STANDBY<br>CURRENT |

|----------------|------------------------|----------------------|--------------------|

|                |                        |                      |                    |

| R098648        | 450ns                  | 100mA                | NA                 |

| R09864CS       | 350ns                  | 100mA                | NA                 |

| R09864C        | 300ns                  | 100mA                | NA                 |

| R09864DS       | 250ns                  | 100mA                | NA                 |

| R09864D        | 200ns                  | 85mA                 | NA                 |

| R09864AB       | 450ns                  | 100mA                | 12mA               |

| R09864ACS      | 350ns                  | 100mA                | 12mA               |

| R098964AC      | 300ns                  | 100mA                | 12mA               |

| R09864ADS      | 250ns                  | 100mA                | 12mA               |

| R09864AD       | 200ns                  | 85mA                 | 12mA               |

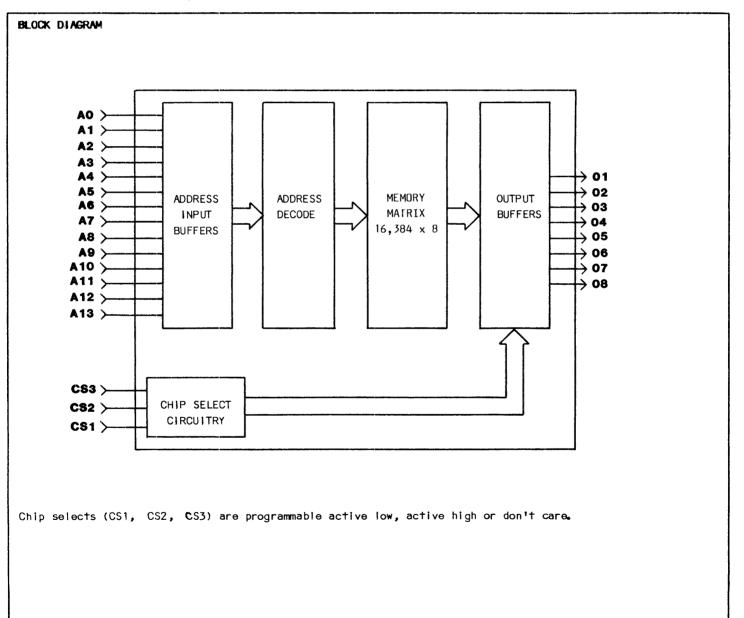

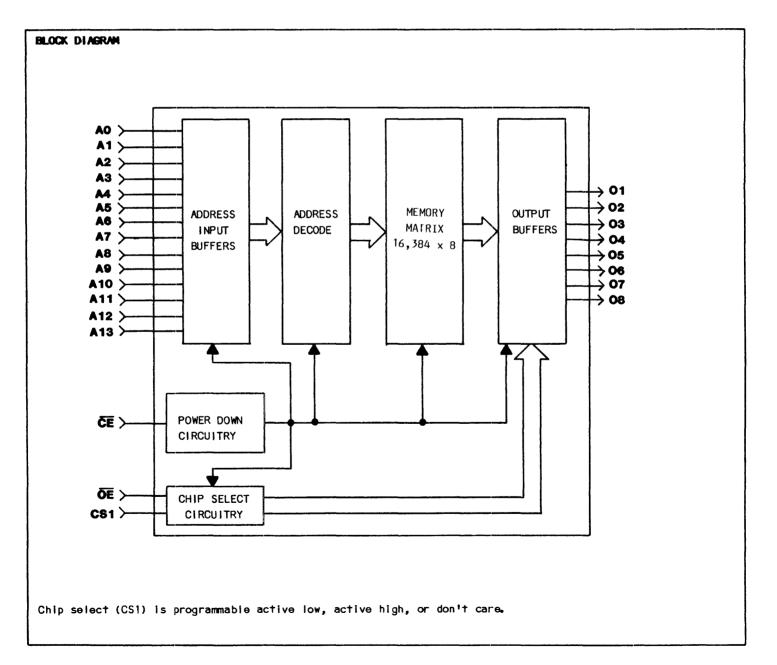

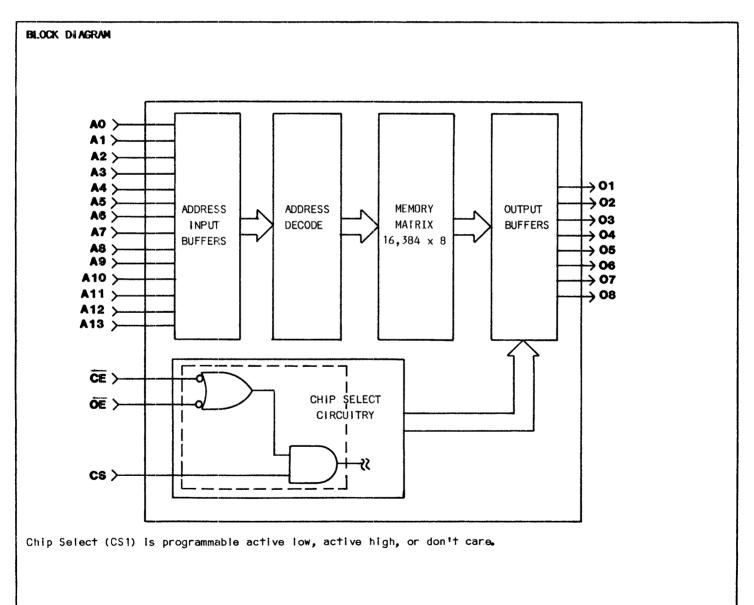

# 131,072 BIT STATIC READ ONLY MEMORY

#### FEATURES

- 16,384 x 8 organization

- Single +5V <u>+</u>10% volt supply

- 450ns max access time: R09128B

- 350ns max access time: R09128CS

- 300ns max access time: R09128C

- 250ns max access time: R09128DS

- 200ns max access time: R09128D

- Totally static operation

- Three state outputs

- All TTL compatible inputs/outputs

- 28 pin JEDEC approved pinout

- Programmable "FlexSelect"<sup>TM</sup> chip enable/disable/ power down capabilities controlled by the chip enable ( $\overline{\text{CE}}$ ) and output enable ( $\overline{\text{OE}}$ ) inputs

- ESD Protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD883B

# DESCRIPTION

The General Instrument R09128 is a 131,072 Bit Static Read Only Memory organized as 16,384 eightbit words and is ideally suited for microprocessor memory applications. Fabricated with General Instrument N-Channel Silicon Gate Technology, the R09128 provides the designer with a high performance, easy to use MOS circuit featuring operation from a single +5 Volt power supply and low power dissipation.

| PIN CONFIGURATION   | · · · · · · · · · · · · |                    |

|---------------------|-------------------------|--------------------|

| 28 LEAD DUAL-IN-LIN | E                       |                    |

|                     | Top View                |                    |

| N.C. C              | o1                      | 28 <b>V</b> CC     |

| A12                 |                         | 27 <b>0</b> CS1    |

| A7 🗖                | 3                       | 26 <b>口</b> A13    |

| A6 🗖                | 4                       | 25 🗖 AB            |

| A5 🗖                | 5                       | 24 🗖 A9            |

| A4 🗖                | 6                       | 23 🗖 A11           |

| A3 🗖                | 7                       | 220E/CS2           |

| A2 🗖                | 8                       | 21 🗖 A 10          |

| A1 🗖                | 9                       | 20 <b>1</b> CE/CS3 |

| A0 🗖                | 10                      | 19 08              |

| 01 🗖                | 11                      | 18 07              |

| 02 🖸                | 12                      | 17006              |

| 03 🖸                | 13                      | 16 05              |

| GND 🗖               | 14                      | 15 🗖 04            |

|                     |                         |                    |

The R09128 offers a programmable "Flexselect"<sup>TM</sup> chip enable/disable/power down feature controlled by the chip enable ( $\overline{\text{CE}}$ ), output enable ( $\overline{\text{OE}}$ ) and chip select (CS) inputs. These inputs can be programmed to implement various logic functions which provides the designer with a flexible and easy means of "chip selecting" and/or "powering down" the device. The chip select options are as shown on the following pages.

DS10017B-1

I) \*Standard Chip Select requirements - Non-Power Down

```

CS1 = 0,1 or don't care (Pin 27)

CS2 = 0,1 or don't care (Pin 22)

CS3 = 0,1 or don't care (Pin 20)

```

Logic Function  $1(CS1) \cdot 1(CS2) \cdot 1(CS3) = Chip Selected$

```

1 Programmed in active state

"." = Logical "AND"

```

\*Not available on "D" speed devices

- II) Standard Chip Select requirements Power Down

- CS1 = 0,1 or don't care (Pin 27)

- $\overline{\text{OE}}$  (Pin 22) When  $\overline{\text{CE}}$  goes high, the device will automatically power down and remain in a low power  $\overline{\text{CE}}$  (Pin 20) standby mode as long as  $\overline{\text{CE}}$  remains high.  $\overline{\text{OE}}$  and CS functions eliminate bus contention in multiple memory device systems.

Logic Function:  $1(CS1) \cdot (\overline{CE}) \cdot (\overline{OE}) = Chip Selected$

<sup>1</sup>Programmed in active state "." = LOGICAL "AND"

III) \*\*"ORED" chip select requirement (chip selects at pins 20 (CE) and 22 (OE) function as a logical "OR").

- \* This is ideally suited for applications that have limited chip select decoding capabilities.

- CS1 = 0,1 or don't care (Pin 27)

- Logic Function: 1(CS). (CE + OE) = Chip Selected

- <sup>1</sup>Programmed in active state

- "." = LOGICAL "AND" "+" = LOGICAL "OR"

- \*\*Not available on "D" speed devices

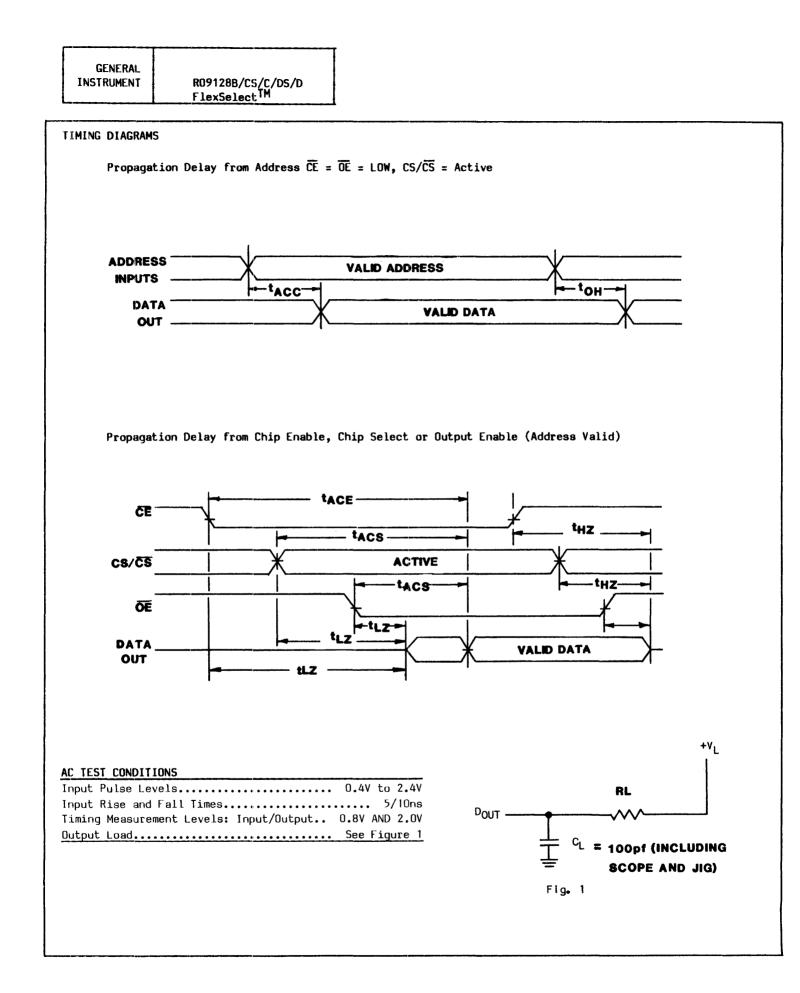

| GENERAL    |                          |

|------------|--------------------------|

| INSTRUMENT | R09128B/CS/C/DS/D        |

|            | FlexSelect <sup>IM</sup> |

# Maximum Ratings\*

V<sub>CC</sub> and Input Voltages

(with Respect to GND)...... -0.5V to +7.0V Storage Temperature...... -65°C to + 150°C

Standard Conditions (unless otherwise noted):

$V_{\rm CC} = 5V + 10\%$

Operating Temperature  $T_A = 0^{\circ}C$  to + 70°C

Output Loading: Two TTL Loads, CL TOTAL = 100pf

\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied -- operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### DC CHARACTERISTICS

| Characteristics              | Sym             | Min | Тур | Max             | Units | Conditions                                |

|------------------------------|-----------------|-----|-----|-----------------|-------|-------------------------------------------|

| Address, CE/CS3, OE/CS2, CS1 |                 |     |     |                 |       |                                           |

| Inputs                       |                 | 2   |     |                 |       |                                           |

| Logic "1"                    | V <sub>IH</sub> | 2.0 | -   | ۷ <sub>CC</sub> | V     |                                           |

| Logic "O"                    | ٧ <sub>IL</sub> | 0   | -   | 0.8             | v     |                                           |

| Leakage                      | ILI             | -10 | -   | +10             | Aپ    | $V_{IN}=0.4V$ to $V_{CC}$                 |

| Data Outputs                 |                 |     |     |                 |       |                                           |

| Logic "1"                    | V <sub>ОН</sub> | 2.4 | -   | V <sub>CC</sub> | V     | Ι <sub>ΟΗ</sub> =-200μΑ                   |

| Logic "O"                    | V <sub>OL</sub> | -   | -   | 0.4             | V     | $I_{OL} = 3.2 \text{ mA}$                 |

| Leakage                      | ILO             | -10 | -   | +10             | μA    | V <sub>OUT</sub> =0.4V to V <sub>CC</sub> |

| Power Supply Current         |                 |     |     |                 |       |                                           |

| I <sub>CC</sub> (Active)     | -               | -   | -   | 100             | mA    | Note 1                                    |

| I <sub>CC</sub> (Standby)    | -               | -   | - 1 | 15              | mA    | Note 2,6                                  |

| I <sub>CC</sub> (Standby)    | -               | -   | -   | 50              | mA    | Note 7                                    |

| AC CHARACTERISTICS  |                  | R09 | 128B | R09 | 128CS | R09 | 128C | R09 | 128DS | R09 | 128D |       |                                            |

|---------------------|------------------|-----|------|-----|-------|-----|------|-----|-------|-----|------|-------|--------------------------------------------|

| Characteristics     | Sym              | Min | Max  | Min | Max   | Min | Max  | Min | Max   | Min | Max  | Units | Conditions                                 |

| Address Access Time | tACC             | -   | 450  | -   | 350   | -   | 300  | -   | 250   | -   | 200  | ns    |                                            |

| Address Hold After  |                  |     |      |     |       | 1   |      |     |       |     |      |       |                                            |

| Address Change      | t <sub>OH</sub>  | 10  | -    | 10  | -     | 5   | -    | 5   |       | 5   | -    | ns    | Note 3                                     |

| Chip Enable Time    | tACE             | -   | 450  | -   | 350   | -   | 300  | -   | 250   | -   | 208  | ns    |                                            |

| Chip Select, Output |                  |     |      |     |       |     |      |     |       | 1   |      |       |                                            |

| Enable Access Time  | t <sub>ACS</sub> | -   | 150  | -   | 125   | -   | 100  | -   | 85    | -   | 70   | ns    | Note 4                                     |

| Output Disable Time | tOFF             | -   | 150  | -   | 125   | - 1 | 100  | -   | 85    | -   | 70   | ns    |                                            |

| Output Low Z Delay  | tLZ              | 10  | -    | 10  | -     | 5   | ~    | 5   |       | 5   | 70   | ns    | Note 3                                     |

| Output High Z Delay | t <sub>HZ</sub>  | -   | 150  | -   | 125   | -   | 100  | -   | 85    | 1 - | 70   |       |                                            |

| Capacitance***      |                  |     |      |     |       |     |      |     |       | 1   |      |       |                                            |

| Input Capacitance   | CI               | -   | 7    | -   | 7     | -   | 7    | -   | 7     | -   | 7    | pf    | F=1MH <sub>Z</sub> , T <sub>A</sub> =+25°C |

| Output Capacitance  | с <sub>о</sub>   | -   | 10   | -   | 10    | -   | 10   | -   | 10    | -   | 10   | pf    | F=1MH <sub>Z</sub> , T <sub>A</sub> =+25°C |

\*\*\*Capacitance is periodically sampled and is not 100% tested.

# NOTES:

1. Measured with device selected and outputs unloaded.

2. Device disabled with  $\overline{CE} \ge 2.0V$  ("Power Down" programmed parts only).

3. These parameters are periodically sampled and are not 100% tested.

4. Access time to valid data measured from CS1 going active and/or  $\overline{OE}$  going low which ever occurs last/first.

- 5. Output high impedance delay  $(t_{HZ})$  is measured from  $\overline{CE}$  and/or  $\overline{OE}$  going high or CS1 going active, which ever occurs last/first.

- 6. Applies to B, CS, and C speeds only.

7. Applies to DS, D speeds only.

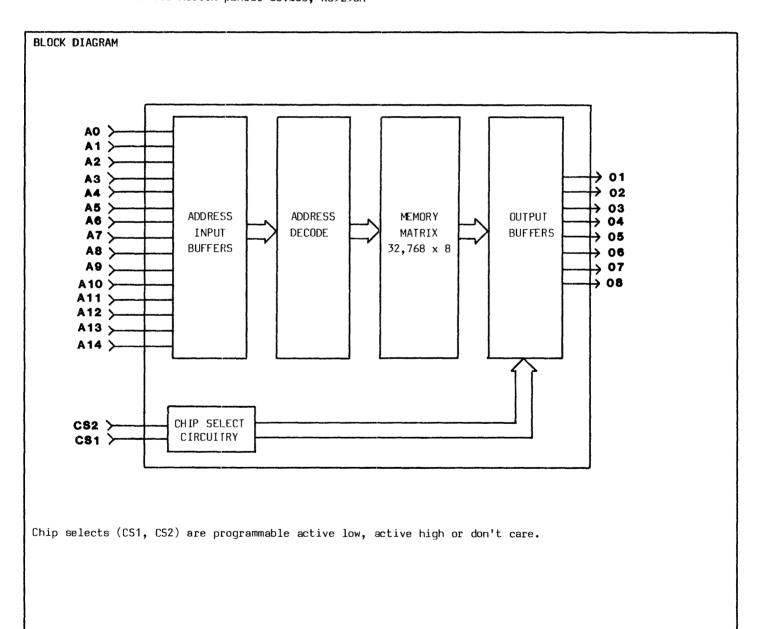

# 262,144 BIT STATIC READ ONLY MEMORY

#### FEATURES:

- 32,768 x 8 organization

- Single +5V <u>+</u>10% supply

- 450ns max access time: R09256B

- 350ns max access time: R09256CS

- 300ns max access time: R09256C

- 250ns max access time: R09256DS

- 200ns max access time: R09256D

- Totally static operation

- Three state outputs

- All ITL compatible input/outputs

- 28 Pin JEDEC approved pinout: R09256

- Programmable "FlexSelect"<sup>TM</sup> chip enable/disable/power down capabilities controlled by the chip enable (CE) and output enable (OE) inputs

- ESD Protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD883B

- Alternate 28 pin Mostek compatible pinout (R09256A) available for DS/D speeds only

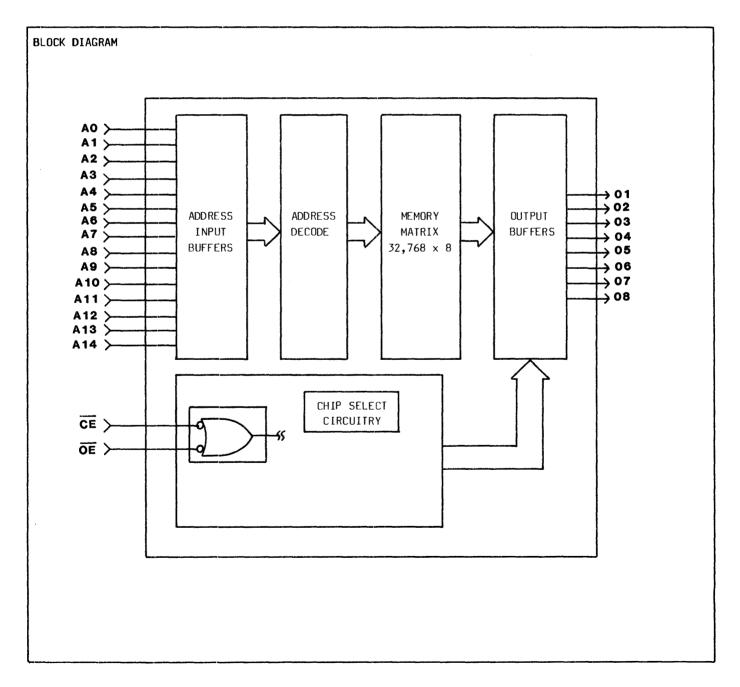

#### DESCRIPTION

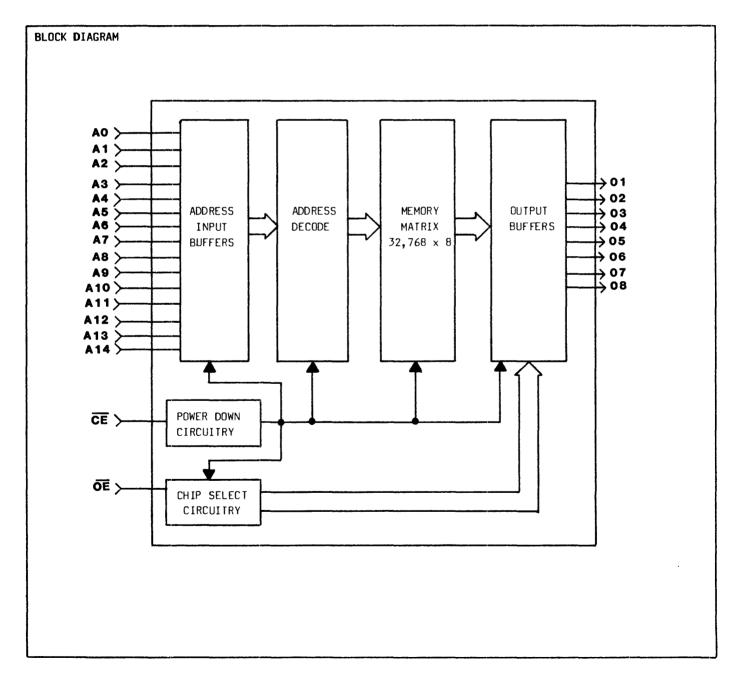

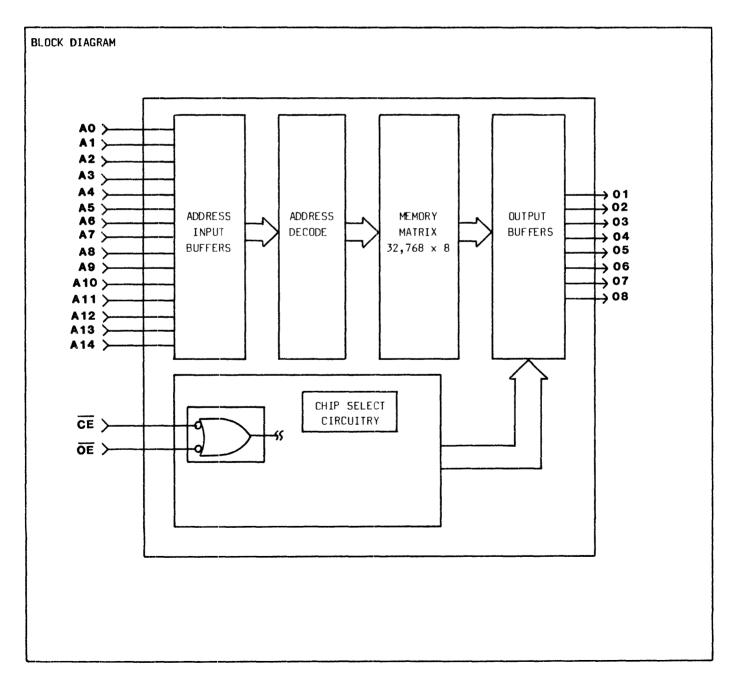

The General Instrument R09256 is a 262,144 Bit Static Read Only Memory organized as 32,768 eightbit words and is ideally suited for microprocessor memory applications. Fabricated with General Instrument N-Channel Silicon Gate Technology, the R09256 provides the designer with a high performance, easy to use MOS circuit featuring operation from a single +5 Volt power supply and low power dissipation.

#### Operation

#### Address (AO-A14)

The address-valid interval determines the device cycle time. The 15-bit positive logic address is decoded on-chip to select on the 32,768 words of 8bit length in the memory array. AO is the leastsignificant bit and A14 the most significant bit of the word address.

# Chip Select

Chip enable/disable/power down "FlexSelect"<sup>TM</sup>. These inputs can be programmed during mask fabrication to implement various logic functions which provides the designer with a flexible and easy means of "chip selecting" and/or "powering down" the device. The "FlexSelect"<sup>TM</sup> options are on the following pages.

| R09256         |                                            | Top View         |                                             |

|----------------|--------------------------------------------|------------------|---------------------------------------------|

| 10/2/0         | N.C. <b>C</b>                              |                  | 28 V <sub>CC</sub>                          |

|                | A12 2                                      |                  | 27 A 14                                     |

|                | A7 <b>C</b> 3                              |                  | 26 A13                                      |

|                | A6 🗖 4                                     |                  | 25 AB                                       |

|                | A5 🗖 5                                     |                  | 24 A9                                       |

|                | A4 <b>匚</b> 6                              |                  | 23 🗖 A11                                    |

|                | A3C 7                                      |                  | 22 DE/CS1                                   |

|                | A2 <b>C</b> 8                              |                  | 21 <b> </b> ] A10                           |

|                | A1 <b>C</b> 9                              |                  | 20 CE/CS2                                   |

|                | AO <b>C</b> 1                              | 0                | 19 08                                       |

|                | 0101                                       | 1                | 18 07                                       |

|                | 02                                         |                  | 17 06                                       |

|                | 03 <b>C</b> 1                              |                  | 16 05                                       |

|                |                                            | 4                | 15 04                                       |

| <u>R09256A</u> | A14                                        | Top View         | 28 V <sub>CC</sub>                          |

|                | A120 2                                     |                  | 27 <b>D</b> N.C.                            |

|                | A70 3                                      |                  | 26 A13                                      |

|                | A6 <b>C</b> 4                              |                  | 25 <b>D</b> A8                              |

|                | A5 <b>C</b> 5                              |                  | 24 <b>D</b> A9                              |

|                | A4C 6                                      |                  | 23 A11                                      |

|                |                                            |                  | 220 OE                                      |

|                | A3C 7                                      |                  |                                             |

|                | A2C 8                                      |                  | 21 <b>1</b> A10                             |

|                | 1                                          |                  | 21 <b>1</b> A10<br>20 <b>1</b> CE           |

|                | A2C 8                                      |                  | 21 A10<br>20 CE<br>19 08                    |

|                | A2C 8<br>A1C 9<br>AOC 1<br>01C 1           | D<br>1           | 21 A10<br>20 CE<br>19 08<br>18 07           |

|                | A2C 8<br>A1C 9<br>A0C 11<br>01C 1<br>02C 1 | D<br>1<br>2      | 21 A 10<br>20 CE<br>19 08<br>18 07<br>17 06 |

|                | A2C 8<br>A1C 9<br>AOC 1<br>01C 1           | D<br>1<br>2<br>3 | 21 A10<br>20 CE<br>19 08<br>18 07           |

- I) Standard Chip Select requirements Non-Power Down

- CS1 = 0,1 or don't care (Pin 22) CS2 = 0,1 or don't care (Pin 20)

- Logic Function  $^{1}(CS1) \cdot ^{1}(CS2)$  = Chip Selected

- 1 Programmed in active state

"." = Logical "AND"

- \* Not available for "D" speed devices \*\*Not available for Mostek pinout device, R09256A

- II) Standard Chip Select requirements Power Down

- $\overline{\text{OE}}$  (Pin 22) When  $\overline{\text{CE}}$  goes high, the device will automatically power down and remain in a low power  $\overline{\text{CE}}$  (Pin 20) standby mode as long as  $\overline{\text{CE}}$  remains high. The  $\overline{\text{OE}}$  function eliminates bus contention in multiple memory device systems.

Logic Function:  $(\overline{CE}) \cdot (\overline{OE}) = Chip Selected$

"." = LOGICAL "AND"

III) "ORED" chip select requirement (chip selects at pins 20 ( $\overline{CE}$ ) and 22 ( $\overline{OE}$ ) function as a logical "OR"). \*This is ideally suited for applications that have limited chip select decoding capabilities.

Logic Function:  $(\overline{CE} + \overline{OE}) = Chip Selected$

"+" = LOGICAL "OR"

\*\* Not available for D speed devices

\*\*\*Not available for Mostek pinout device, R09256A

#### Maximum Ratings\*

| V <sub>CC</sub> and | Input Voltages  |       |      |       |

|---------------------|-----------------|-------|------|-------|

| (with               | Respect to GND) | 0.5   | V to | +7.0V |

| Storage             | Temperature     | -65°C | to + | 150°C |

Standard Conditions (unless otherwise noted):  $V_{CC} = 5V \pm 10\%$ Operating Temperature  $T_A = 0^{\circ}C$  to + 70°C Output Loading: Two TTL Loads,  $C_L$  TOTAL = 100pf

# DC CHARACTERISTICS

\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied -- operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics                        | Sym             | Min | Тур | Max             | Units | Conditions                          |

|----------------------------------------|-----------------|-----|-----|-----------------|-------|-------------------------------------|

| Address, CE/CS2, OE/CS1                |                 |     |     |                 |       |                                     |

| Inputs                                 |                 |     |     |                 |       |                                     |

| Logic "1"                              | V <sub>IH</sub> | 2.0 | -   | V <sub>CC</sub> | v     |                                     |

| Logic "O"                              | VIL             | 0   | -   | 0.8             | v     |                                     |

| Leakage                                | ILI             | -10 | -   | +10             | Au    | $V_{\rm IN} = 0.4V$ to $V_{\rm CC}$ |

| Data Outputs                           |                 |     |     |                 |       |                                     |

| Logic "1"                              | V <sub>OH</sub> | 2.4 | -   | ٧ <sub>CC</sub> | v     | AبرI <sub>OH</sub> = –400A          |

| Logic "O"                              | VOL             | -   | -   | 0.4             | v     | $I_{OL} = 3.2 \text{mA}$            |

| Leakage                                | ILO             | -10 | -   | +10             | Au    | $V_{OUT} = 0.4V$ to $V_{CC}$        |

| Power Supply Current                   |                 |     |     |                 |       |                                     |

| I <sub>CC</sub> (Active)               | -               | -   | -   | 100             | mA    | Note 1                              |

| I <sub>CC</sub> (Standby)              | -               | -   | -   | 20              | mA,   | Note 2                              |

| I <sub>CC</sub> (Standby) D-speed only | -               | -   | -   | 50              | mA    | Note 2                              |

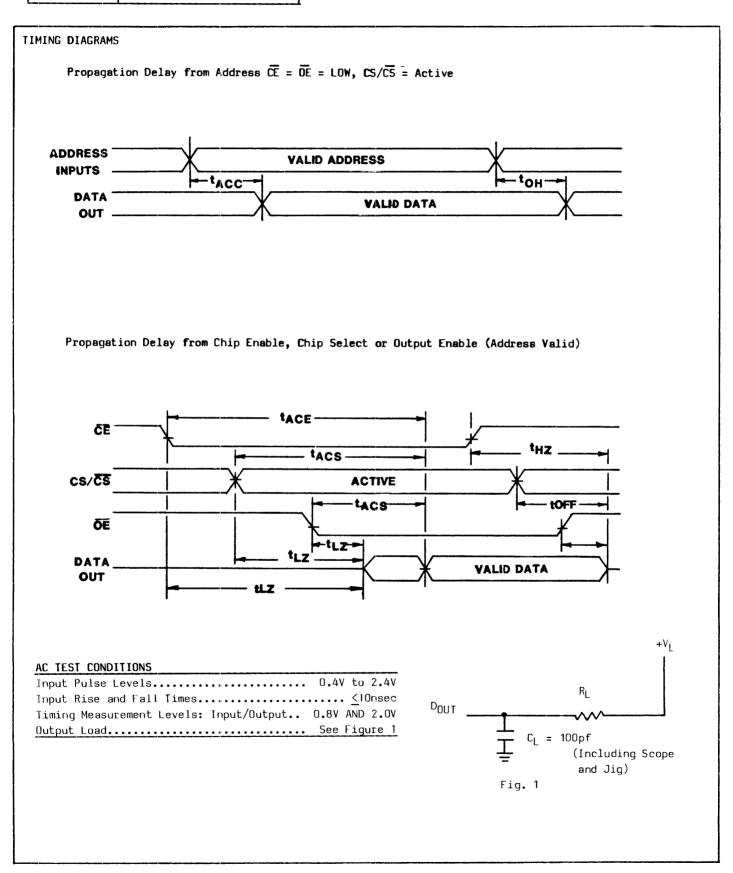

| AC CHARACTERISTICS  |                  | R092 | 2568 | R092 | 56CS | R092 | 256C | R092 | 256DS | R092 | 256D |       |                                 |

|---------------------|------------------|------|------|------|------|------|------|------|-------|------|------|-------|---------------------------------|

| Characteristics     | Sym              | Min  | Max  | Min  | Max  | Min  | Max  | Min  | Max   | Min  | Max  | Units | Conditions                      |

| Address Access Time | tACC             | -    | 450  | -    | 350  | -    | 300  | -    | 250   | -    | 200  | ns    |                                 |

| Address Hold After  |                  |      |      |      |      |      |      |      |       |      |      |       |                                 |

| Address Change      | t <sub>OH</sub>  | 10   | -    | 10   | -    | 5    | -    | 5    | -     | 5    | -    | ns    | Note 3                          |

| Chip Enable Time    | tACE             | -    | 450  | -    | 350  | -    | 300  | -    | 250   | -    | 200  | ns    |                                 |

| Chip Select, Output |                  |      |      |      |      |      |      |      |       |      |      |       |                                 |

| Enable Access Time  | t <sub>ACS</sub> | -    | 150  | -    | 125  | -    | 100  | -    | 85    | -    | 70   | ns    | Note 4                          |

| Output Disable Time | tOFF             | -    | 150  | -    | 125  | -    | 100  | -    | 85    | -    | 70   | ns    |                                 |

| Output Low Z Delay  | τ <sub>LZ</sub>  | 10   | -    | 10   | -    | 5    | -    | 5    | -     | 5    | -    | ns    | Note 3                          |

| Output High Z Delay | t <sub>HZ</sub>  | -    | 150  | -    | 125  | -    | 100  | -    | 85    | -    | 70   | ns    | Note 5                          |

| Capacitance***      |                  |      |      |      |      |      |      |      |       |      |      |       |                                 |

| Input Capacitance   | CI               | -    | 7    | -    | 7    | -    | 7    | -    | 7     | -    | 7    | pf    | $F = 1MH_Z, T_A = +25^{\circ}C$ |

| Output Capacitance  | C <sub>O</sub>   | -    | 10   | -    | 10   | -    | 10   | -    | 10    | -    | 10   | pf    | $F = 1MH_Z, T_A = +25°C$        |

\*\*\*Capacitance is periodically sampled and is not 100% tested.

#### NOTES:

1. Measured with device selected and outputs unloaded.

2. Device disabled with  $\overline{CE} \ge 2.0V$  ("Power Down" programmed parts only).

3. These parameters are periodically sampled and not 100% tested.

- 4. Access time to valid data measured from CS1 going active and/or OE going low whichever occurs last/first.

- 5. Output high impedance delay ( $t_{HZ}$ ) is measured from CE and/or OE going high or CS1 going active,

which ever occurs first/last.

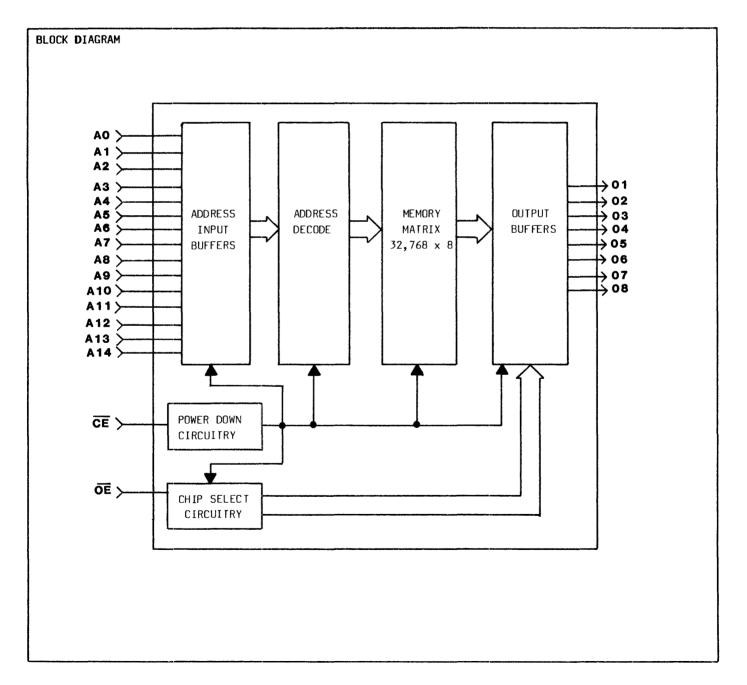

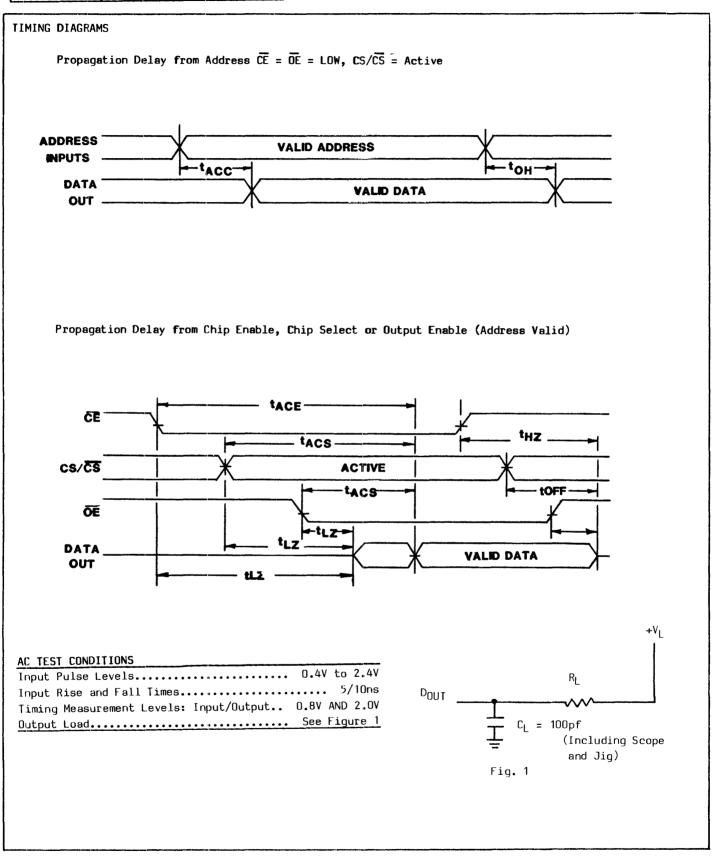

# 262,144 BIT STATIC READ ONLY MEMORY

#### FEATURES:

- 32,768 x 8 organization

- Single +5 /Volt Supply

- 450ns max access time: ROC256B

- 350ns max access time: ROC256CS

- 300ns max access time: ROC256C

- 250ns max access time: ROC256DS

- 200ns max access time: ROC256D

- Totally static operation

- Three state outputs

- All TTL compatible input/outputs

- 28 Pin JEDEC approved pinout

- Programmable "FlexSelect"<sup>TM</sup> chip enable/disable/power down capabilities controlled by the chip enable ( $\overline{CE}$ ) and output enable ( $\overline{OE}$ ) inputs

- ESD Protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD883B

- Low Power Dissipation:

- $I_{CC}$  (Active) max @ 5.5V, 0°C = 40mA,  $I_{CC}$  (Standby) max @ 5.5V, 0°C = 1mA

# DESCRIPTION

The General Instrument ROC256 is a 262,144 Bit CMOS Static Read Only Memory organized as 32,768 eightbit words and is ideally suited for microprocessor memory applications. Fabricated with General Instrument CMOS Silicon Gate Technology, the ROC256 provides the designer with a high performance, easy to use CMOS circuit featuring operation from a single +5 Volt power supply and low power dissipation.

#### Operation

#### Address (AD-A14)

The address-valid interval determines the device cycle time. The 15-bit positive logic address is decoded on-chip to select on the 32,768 words of 8bit length in the memory array. AO is the leastsignificant bit and A14 the most significant bit of the word address.

| 28 LEAD DUAL-IN-LINE |                      |

|----------------------|----------------------|

| Тор                  | View                 |

| N.C. <b>D</b> •1     | 28 🗖 V <sub>CC</sub> |

| A12 🗖 2              | 27 <b>D</b> A14      |

| A7 🗖 3               | 26 🗖 A 1 3           |

| A6 <b>C</b> 4        | 25 🗖 A8              |

| A5 🗖 5               | 24 🗖 A9              |

| A4 <b>C</b> 6        | 23 <b>D</b> A11      |

| A3 🗖 7               | 22 DOE/CS1           |

| A2 <b>C</b> 8        | 21 🗖 A10             |

| A1 <b>C</b> 9        | 20 CE/CS2            |

| AO 🕻 10              | 19 🗖 08              |

| 01 <b>C</b> 11       | 18 🗖 07              |

| 02 🖬 12              | 17 🗖 06              |

| 03 🖬 13              | 16 <b>口</b> 05       |

| GND <b>C</b> 14      | 15 🗖 04              |

# Chip Select

Chip enable/disable/power down "FlexSelect"<sup>TM</sup>. These inputs can be programmed during mask fabrication to implement various logic functions which provides the designer with a flexible and easy means of "chip selecting" and/or "powering down" the device. The "FlexSelect"<sup>TM</sup> options are explained on the following pages. I) Standard Chip Select requirements - Non-Power Down

CS1 = 0,1 or don't care (Pin 22) CS2 = 0,1 or don't care (Pin 20)

Logic Function  $^{1}(CS1) \cdot ^{1}(CS2) = Chip Selected$

1 Programmed in active state

"." = Logical "AND"

- II) Standard Chip Select requirements Power Down

- OE (Pin 22) When CE goes high, the device will automatically power down and remain in a low power CE (Pin 20) standby mode as long as CE remains high. The OE function eliminates bus contention in multiple memory device systems.

Logic Function:  $(\overline{CE}) \cdot (\overline{OE}) = Chip Selected$

"." = LOGICAL "AND"

III) "ORED" chip select requirement (chip selects at pins 20 ( $\overline{CE}$ ) and 22 ( $\overline{OE}$ ) function as a logical "OR"). \*This is ideally suited for applications that have limited chip select decoding capabilities. Logic Function: ( $\overline{CE} + \overline{OE}$ ) = Chip Selected

"+" = LOGICAL "OR"

GENERAL ROC256B/CS/C/DS/D INSTRUMENT FlexSelect<sup>TM</sup>

#### ELECTRICAL CHARACTERISTICS

#### Maximum Ratings\*

$V_{\mbox{\scriptsize CC}}$  and Input Voltages

Standard Conditions (unless otherwise noted):

$V_{CC} = 5V \pm 10\%$

Operating Temperature  $T_A = 0^{\circ}C$  to + 70°C

Output Loading: Two TTL Loads, C<sub>L</sub> TOTAL = 100pf

\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied -- operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

#### DC CHARACTERISTICS

| Characteristics           | Sym             | Min | Тур | Max             | Units | Conditions                   |

|---------------------------|-----------------|-----|-----|-----------------|-------|------------------------------|

| Address, CE/CS2, OE/CS1   |                 |     |     |                 |       |                              |

| Inputs                    |                 |     |     |                 |       |                              |

| Logic "1"                 | ۷ <sub>IH</sub> | 2.0 | -   | V <sub>CC</sub> | v     |                              |

| Logic "O"                 | ٧ <sub>IL</sub> | 0   | -   | 0.8             | v     |                              |

| Leakage                   | ILI             | -10 | -   | +10             | μA    | $V_{IN} = 0.4V$ to $V_{CC}$  |

| Data Outputs              |                 |     |     |                 |       |                              |

| Logic "1"                 | V <sub>OH</sub> | 2.4 | -   | V <sub>CC</sub> | v     | I <sub>OH</sub> = -400µA     |

| Logic "O"                 | V <sub>OL</sub> | -   | -   | 0.4             | v     | $I_{OL} = 3.2 \text{mA}$     |

| Leakage                   | ILO             | -10 | -   | +10             | μA    | $V_{OUT} = 0.4V$ to $V_{CC}$ |

| Power Supply Current      |                 |     |     |                 |       |                              |

| I <sub>CC</sub> (Active)  | -               | -   | -   | 40              | mA    | Note 1                       |

| I <sub>CC</sub> (Standby) | -               | -   | -   | 1               | mA    | Note 2                       |

| AC CHARACTERISTICS  |                  | ROC 2 | 56B | ROC 2 | 56CS | ROC2 | 56C | ROC2 | 56DS | ROC 2 | 56D |       |                                 |

|---------------------|------------------|-------|-----|-------|------|------|-----|------|------|-------|-----|-------|---------------------------------|

| Characteristics     | Sym              | Min   | Max | Min   | Max  | Min  | Max | Min  | Max  | Min   | Max | Units | Conditions                      |

| Address Access Time | tACC             | -     | 450 | -     | 350  | 1    | 300 | -    | 250  | -     | 200 | ns    |                                 |

| Address Hold After  |                  |       |     |       |      |      |     |      |      |       |     |       |                                 |

| Address Change      | t <sub>OH</sub>  | 10    | -   | 10    | -    | 5    | -   | 5    | -    | 5     | -   | ns    | Note 3                          |

| Chip Enable Time    | tACE             | -     | 450 | -     | 350  | -    | 300 | -    | 250  | -     | 200 | ns    |                                 |

| Chip Select, Output |                  |       |     |       |      |      |     |      |      |       |     |       |                                 |

| Enable Access Time  | t <sub>ACS</sub> | -     | 150 | -     | 125  | -    | 100 | -    | 85   | -     | 70  | ns    | Note 4                          |

| Output Disable Time | tOFF             | -     | 150 | -     | 125  | -    | 100 | -    | 85   | -     | 70  | ns    |                                 |

| Output Low Z Delay  | tLZ              | 10    | -   | 10    | -    | 5    | -   | 5    | -    | 5     | -   | ns    | Note 3                          |

| Output High Z Delay | t <sub>HZ</sub>  | -     | 150 | -     | 125  | -    | 100 | -    | 85   | -     | 70  | ns    | Note 5                          |

| Capacitance***      |                  |       |     |       |      |      |     |      |      |       |     |       |                                 |

| Input Capacitance   | CI               | -     | 7   | -     | 7    | -    | 7   | -    | 7    | -     | 7   | pf    | $F = 1MH_Z, T_A = +25^{\circ}C$ |

| Output Capacitance  | CO               | -     | 10  | -     | 10   | -    | 10  |      | 10   | -     | 10  | pf    | $F = 1MH_Z, T_A = +25^{\circ}C$ |

| ·····               |                  |       |     |       | L    |      |     |      | I    |       |     | l     |                                 |

\*\*\*Capacitance is periodically sampled and is not 100% tested.

# NOTES:

1. Measured with device selected and outputs unloaded.

2. Device disabled with  $\overline{CE} \ge 2.0V$  ("Power Down" programmed parts only).

3. These parameters are periodically sampled and not 100% tested.

4. Access time to valid data measured from CS1 going active and/or DE going low whichever occurs last/first.

5. Output high impedance delay ( $t_{HZ}$ ) is measured from  $\overline{CE}$  and/or  $\overline{OE}$  going high or CS1 going active, which ever occurs first/last.

#### PRELIMINARY INFORMATION

PIN CONFIGURATION

# 524,288 STATIC READ ONLY MEMORY

# FEATURES:

- Mask programmable storage providing 64K x 8 bit words with programmable "VariPage"<sup>TM</sup> memory array organization

- Single 64K Byte Pages: R095120

- Two 32K Byte Pages: R095121

- Four 16K Byte Pages: R095122

- One programmable chip select (CS); R09512X, or: power down feature (CE); R09512XA

- 250ns max access time: R09512XDS, R09512XADS

- 200ns max access time: R09512XD, R09512XAD

- 150ns max access time: R09512XES, R09512XAES

- Fully static operation

- Single +5V +10% supply

- Inputs and outputs TTL compatible

- Three state outputs under the control of one mask programmable chip select input

- Low power dissipation

- 28 pin JEDEC approved pinout

- ESD Protection: Inputs are designed to meet 2.3KV per test method 3015.1, MIL-STD 8838

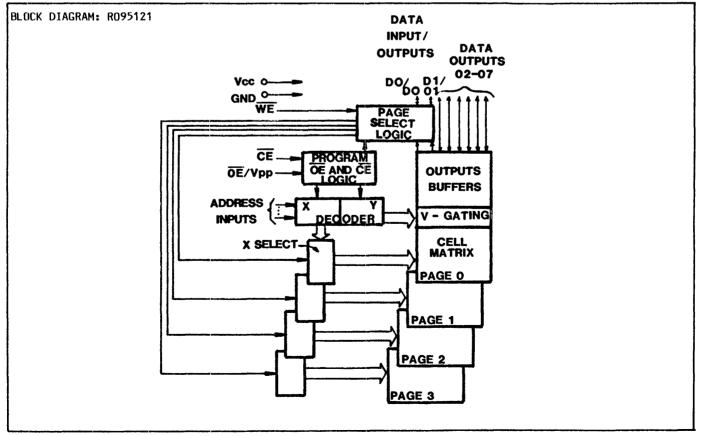

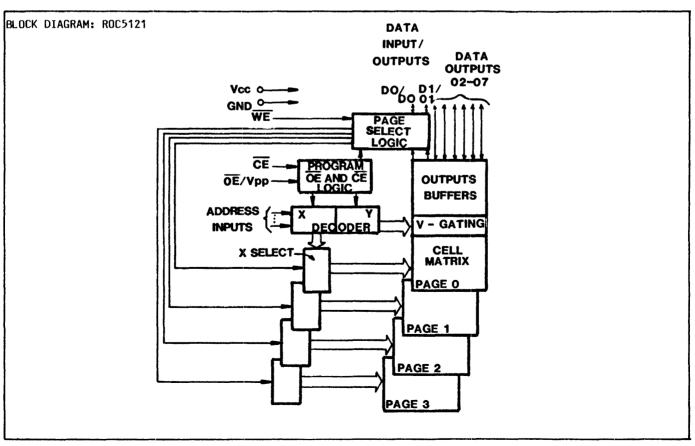

#### DESCRIPTION

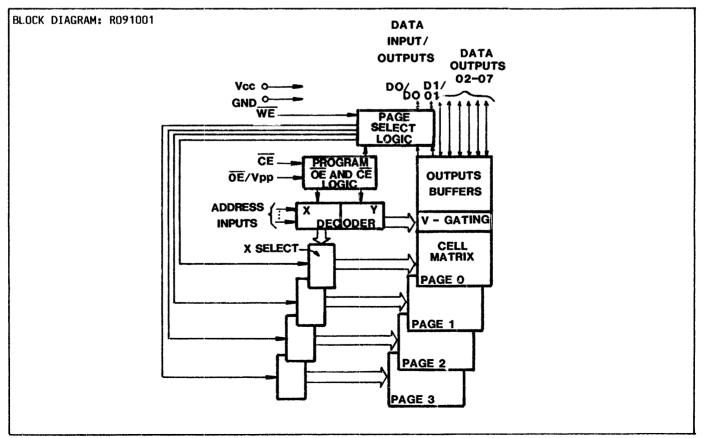

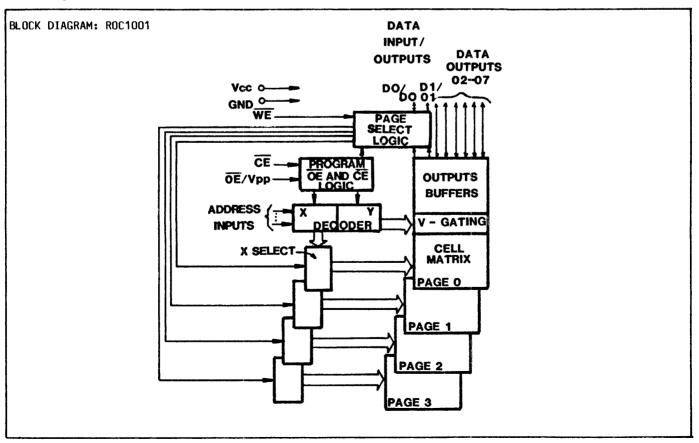

The General Instrument R09512X is a 524,288 bit static read only memory capable of variable page organization. Fabricated with General Instrument's N-Channel Silicon Gate Technology, the R09512X provides the designer with a high performance, flexible NMOS memory circuit featuring operation from a single +5V power supply and low power dissipation.

#### Memory Organization

The R09512X is designed to offer a mask programmable option of choosing page sizes consistent with specific addressing limitations. For example, if only fifteen address lines are available, the R09512X could be programmed to "bank select" on 256K page boundaries (i.e. two 32K x 8 pages), see block diagram.

The R09512X in its straight (non-paging) format, will utilize all sixteen address inputs for direct addressing. When programmed to bank select on either 16K or 32K byte page boundaries, page selection is accomplished via the write enable ( $\overline{\text{WE}}$ ) and the three I/O pins.

| 28 LEAD DUAL | IN LINE                        |                                  |

|--------------|--------------------------------|----------------------------------|

| R095120      |                                | VIEW                             |

|              | A15 <b>[</b> ]1                | 28 2 V <sub>CC</sub>             |

| 64 x 8       | A12 <b>[</b> ]2                |                                  |

| organization | А7 <b>С</b> 3<br>Аб <b>С</b> 4 | 26 🗖 A13<br>25 🗖 A8              |

|              | A5 <b>C</b> 5                  | 24 D A9                          |

|              | A4 <b>C</b> 6                  | 23 A11                           |

|              | A3C 7                          |                                  |

|              | A2 <b>L</b> 8                  | 21 <b>D</b> A10                  |

|              | A1 <b>C</b> 9                  | 20 <b>0</b> CS/CE                |

|              | A0 <b>C</b> 10                 | 19 07                            |

|              | 0Ø <b>C</b> 11                 |                                  |

|              | 01 <b>C</b> 12                 |                                  |

|              |                                | 16 <b>日</b> 04<br>15 <b>日</b> 03 |

|              | V <sub>SS</sub> C 14           |                                  |

| R095121                  | TOP VIE | W                    |

|--------------------------|---------|----------------------|

| WE                       | 1       | 28 🗖 V <sub>CC</sub> |

| (2) 32K x 8 A12 <b>(</b> | 2       | 27 🗖 A14             |

| organization A7          | 3       | 26 <b>口</b> A13      |

| A6 <b>(</b>              | 4       | 25 <b>D</b> A8       |

| A5 <b>(</b>              | 5       | 24 🗖 A9              |

| A4(                      | 6       | 23 <b>]</b> A11      |

| A3 <b>(</b>              | 7       | 22 <b>0</b> OE       |

| A2 <b>C</b>              | 8       | 21 <b>D</b> A10      |

| A10                      | 9       | 20 <b>D</b> CS/CE    |

| AO                       | 10      | 19 <b>D</b> 07       |

| 1/0Ø <b>(</b>            | 11      | 18 🗖 06              |

| I/01                     | 12      | 170 05               |

| I/02 <b>(</b>            | 13      | 16 🗖 04              |

| v <sub>SS</sub> t        | 14      | 15 03                |

| R095122      | TOP                         | VIEW               |

|--------------|-----------------------------|--------------------|

|              | NCE 1                       | 28 V <sub>CC</sub> |

| (4) 16K x 8  | A12 <b>C</b> 2              | 27 WE              |

| organization | A7 <b>C</b> 3               | 26 <b>口</b> A13    |

| organizza au | A6 <b>C</b> 4               | 25 <b>D</b> A8     |

|              | A5 <b>C</b> 5               | 24 🗖 A9            |

|              | A4 🗖 6                      | 23 <b>D</b> A11    |

|              | A3C 7                       | 22 <b>日</b> 0E     |

|              | A2 🗖 8                      | 21 <b>D</b> A10    |

|              | A1 <b>C</b> 9               | 20 <b>2</b> CS/CE  |

|              | AO <b>C</b> 10              | 19 07              |

|              | 1/0Ø <b>E</b> 11            | 18 🗖 06            |

|              | 1/01 <b>C</b> 12            | 17 <b>2</b> 05     |

|              | 1/02 <b>C</b> 13            | 16 04              |

|              | ۷ <sub>SS</sub> <b>C</b> 14 | 15 03              |

#### Operation

# Address (AO-A13, A14-A15 optional)

The address valid interval determines the device cycle time. The positive logic address is decoded to select 16K, 32K, or 64K by 8-bit pages. AO is the least significant bit and A15 is the most significant bit of the word address.

#### Chip Select (CS)

This is a programmable chip select which will be sacrificed if the power down option is selected. The address bus will tri-state when CS is in the inactive state.

#### Chip Enable $(\overline{CE})$

The power down feature of the R09512XA is controlled by the chip enable  $(\overline{CE})$  input. If the power down feature is programmed, the device will go into a low current mode when  $\overline{CE}$  is equal to or greater than 2.0 volts. The R09512XA will remain in a low power standby mode as long as CE remains high.

### Output Enable (OE)

The  $\overline{\text{OE}}$  functions as a chip select for the RO95121 and RO95122. The address bus will tri-state when  $\overline{\text{OE}}$  is high.

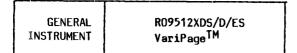

# Write Enable (WE)

The  $\overline{\text{WE}}$  pin allows the R095121 or R095122's RAM to accept a page transition address. The page address is entered via the three I/O pins and latched into the RAM on the rising edge of the  $\overline{\text{WE}}$  signal. The three-bit page address is decoded as follows:

#### PAGE DEFINITIONS

|                | 16K  | x 8 Pa           |                  | 32K  | x 8 Pa           | qes              |

|----------------|------|------------------|------------------|------|------------------|------------------|

| Page           | 1/02 | 1/0 <sup>1</sup> | 1/0 <sup>0</sup> | 1/02 | I/0 <sup>1</sup> | I/0 <sup>0</sup> |

| PO             | 0    | 0                | 0                | 0    | 0                | х                |

| P <sub>1</sub> | 0    | 0                | 1                | 0    | 1                | х                |

| P2             | 0    | 1                | 0                | 1    | 0                | Х                |

| Ρ3             | 0    | 1                | 1                | 1    | 1                | х                |

| P4             | 1    | 0                | 0                | Х    | X                | X                |

| P <sub>5</sub> | 1    | 0                | 1                | X    | х                | Х                |

| P6             | 1    | 1                | 0                | Х    | х                | х                |

| P7             | 1    | 1                | 1                | X    | X                | х                |

|                |      |                  |                  |      |                  |                  |

| L              |      |                  |                  |      |                  |                  |

#### Note:

During power-up, the device will reset to page O. Upon page selection, only the selected page will be powered, the non-selected pages will automatically power down.

#### ELECTRICAL CHARACTERISTICS

#### Maximum Ratings\*

V<sub>CC</sub> and Input Voltages

(with Respect to GND)..... -0.5V to +7.0V

Storage Temperature..... -65°C to + 150°C

**Standard Conditions** (unless otherwise noted):  $V_{CC} = 5V \pm 10\%$ Operating Temperature T<sub>A</sub> = 0°C to + 70°C Output Loading: Two TTL Loads, C<sub>L</sub> TOTAL = 100pf \*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied -- operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

### DC CHARACTERISTICS

| Characteristics                     | Sym             | Min | Тур | Max             | Units | Conditions                   |

|-------------------------------------|-----------------|-----|-----|-----------------|-------|------------------------------|

| Address, CE/CS, OE Inputs           |                 |     |     | 1               |       |                              |

| Logic "1"                           | V <sub>IH</sub> | 2.0 | -   | V <sub>CC</sub> | v     |                              |

| Logic "O"                           | VIL             | 0   | ~   | 0.8             | v     |                              |

| Leakage                             | ILI             | -   | -   | 10              | μA    | $V_{IN}$ = 0.4V to $V_{CC}$  |

| Data Outputs                        |                 |     |     |                 |       |                              |

| Logie "1"                           | V <sub>OH</sub> | 2.4 | -   | V <sub>CC</sub> | v     | $I_{OH} = -400 \mu A$        |

| Logic "O"                           | VOL             | -   |     | 0.4             | V     | $I_{OL} = 2.1 \text{mA}$     |

| Leakage                             | ILO             | -   | -   | 10              | Αبر   | $V_{OUT} = 0.4V$ to $V_{CC}$ |

| Power Supply Current                |                 |     |     |                 |       |                              |

| I <sub>CC</sub> (Active, Non-Paged) | ICC             | -   | -   | 125             | mA    | Note 1                       |

| I <sub>CC</sub> (Active, Paged)     | ICC             | -   | -   | 100             | mA    | Note 2                       |

| I <sub>CC</sub> (Standby)           | ICC             | -   | -   | 30              | mA    | Note 3                       |

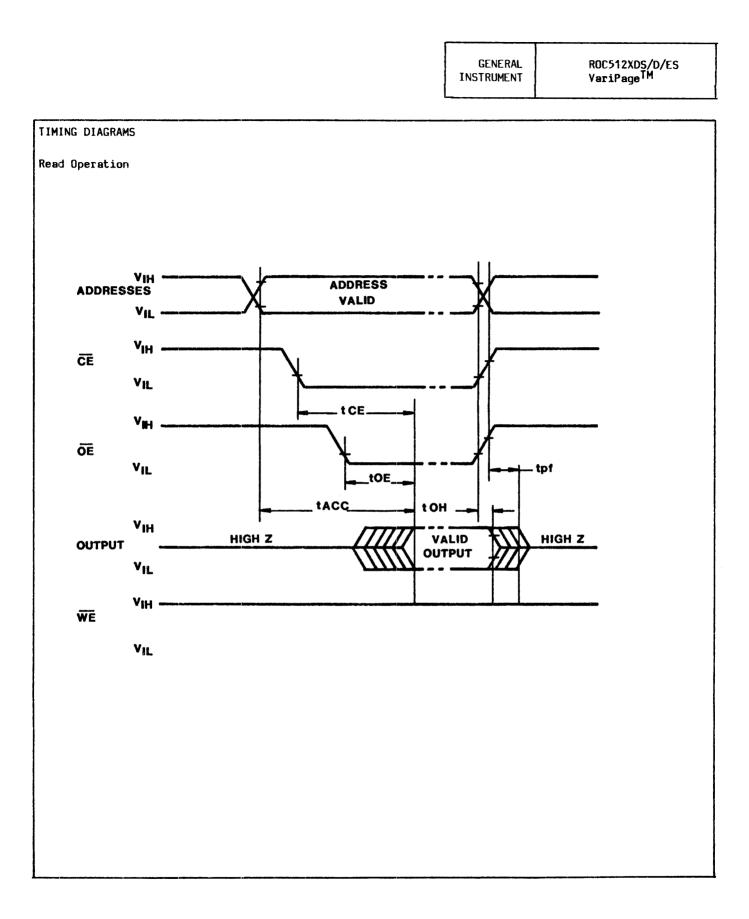

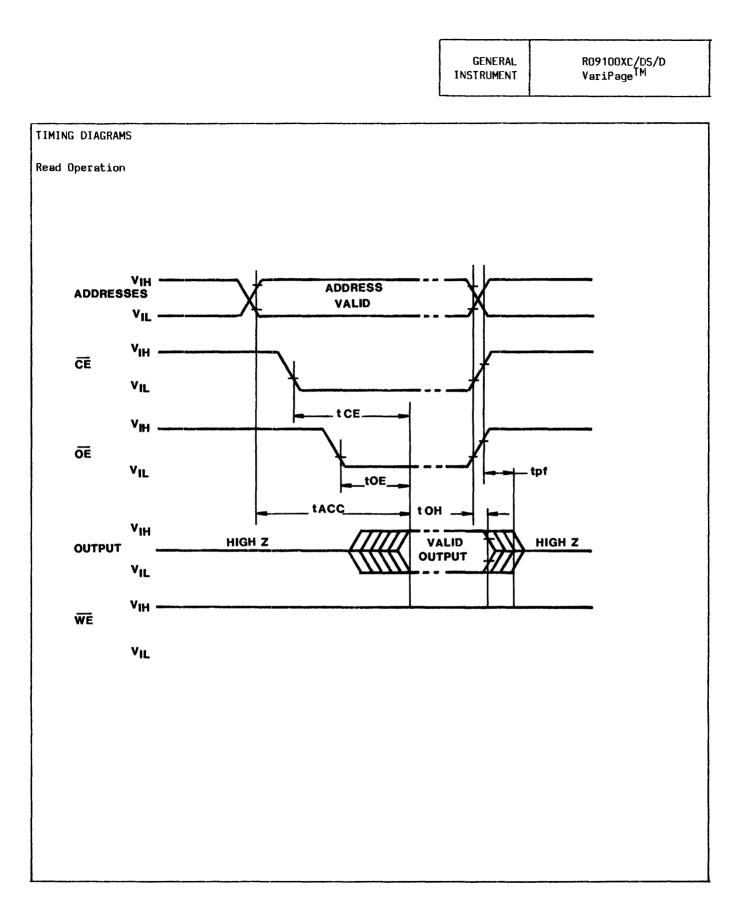

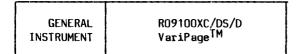

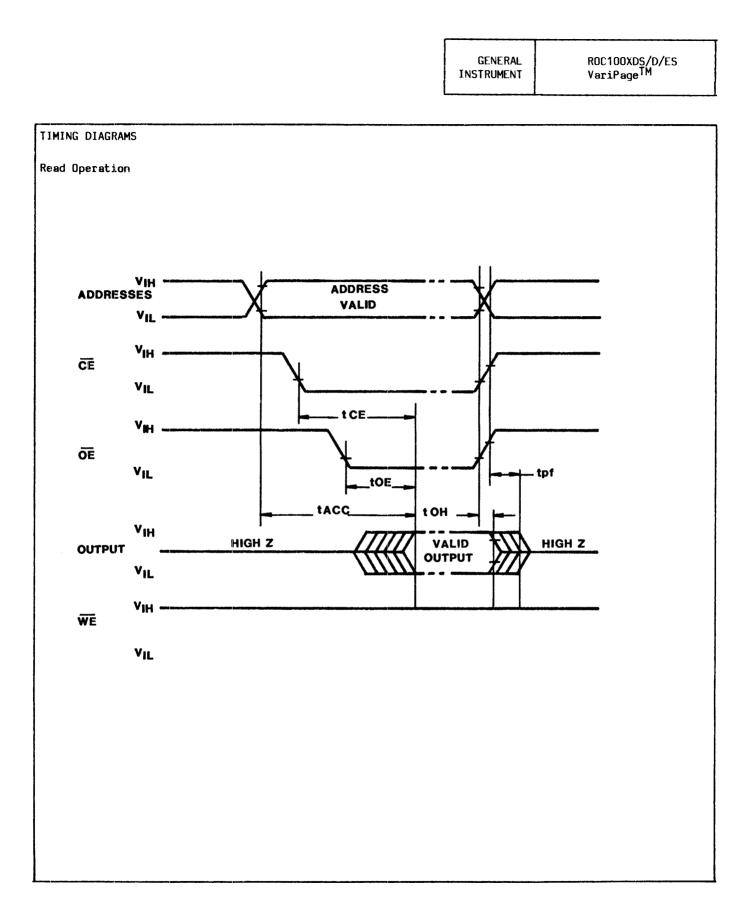

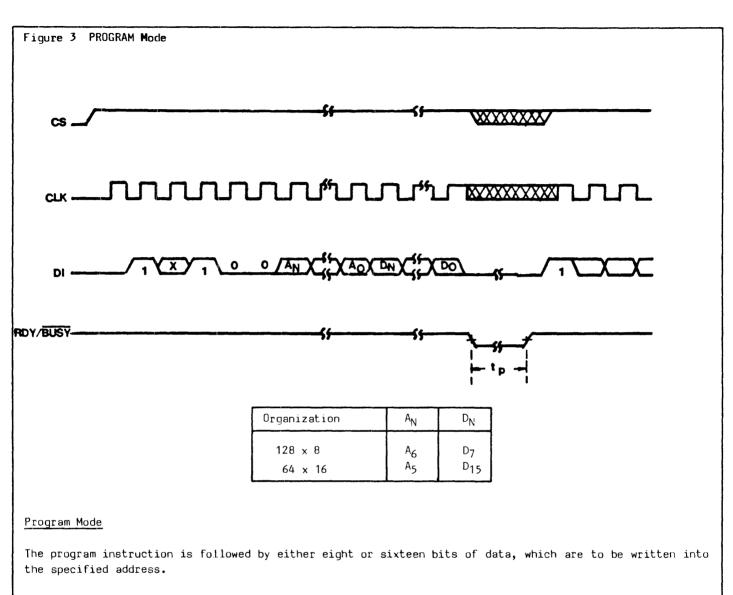

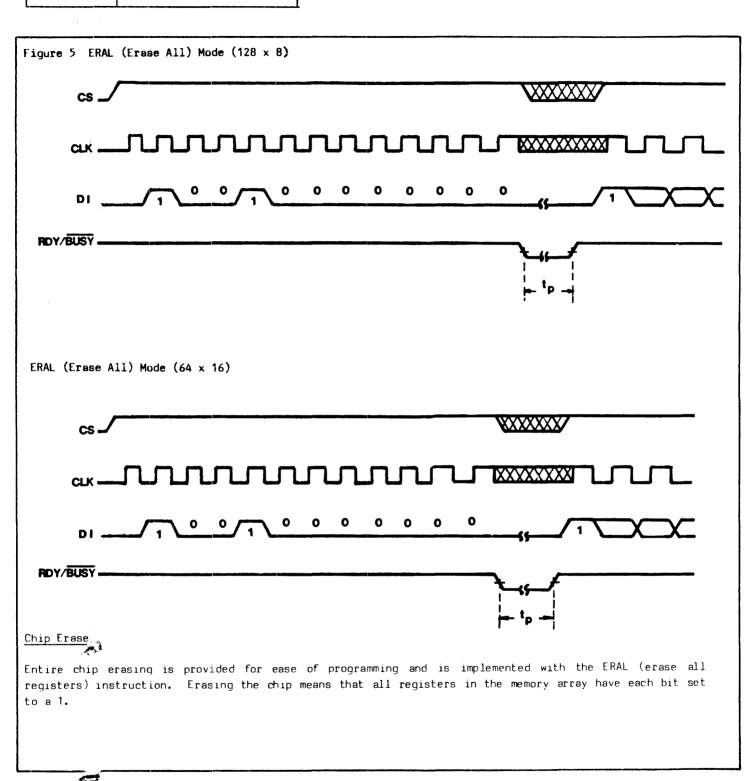

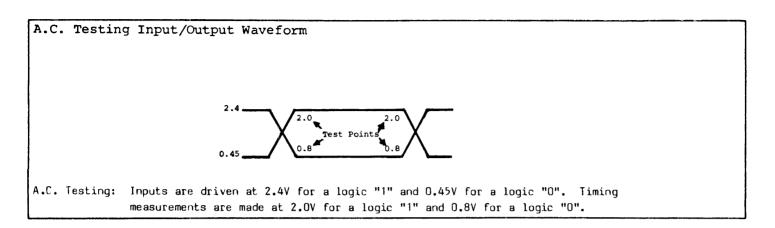

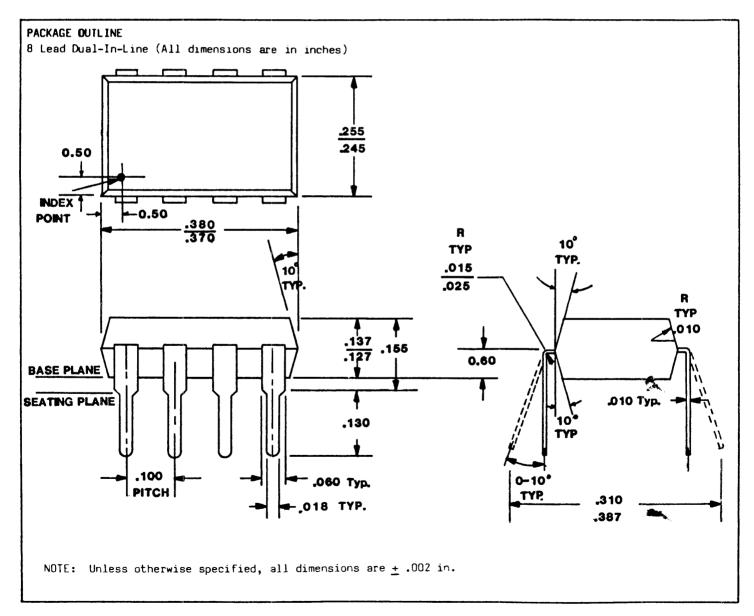

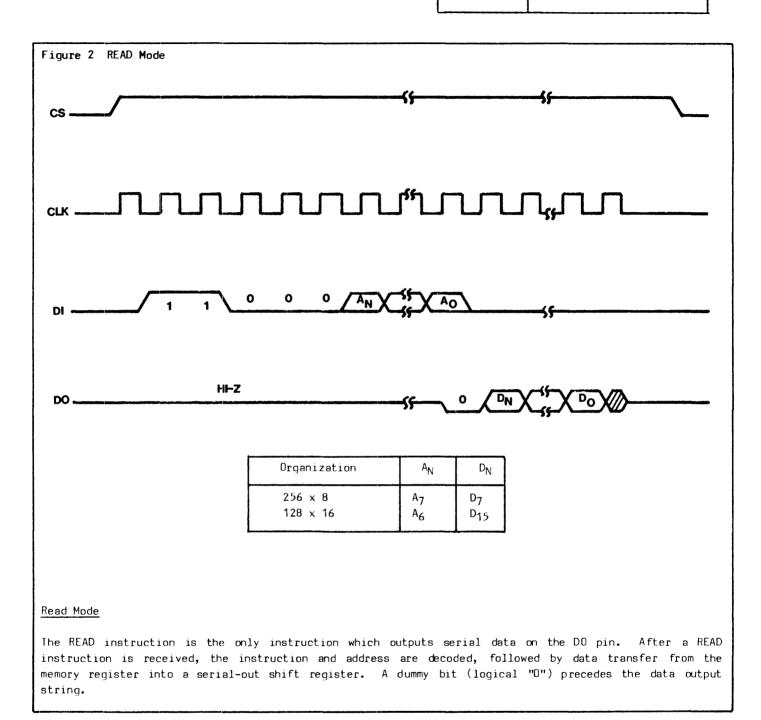

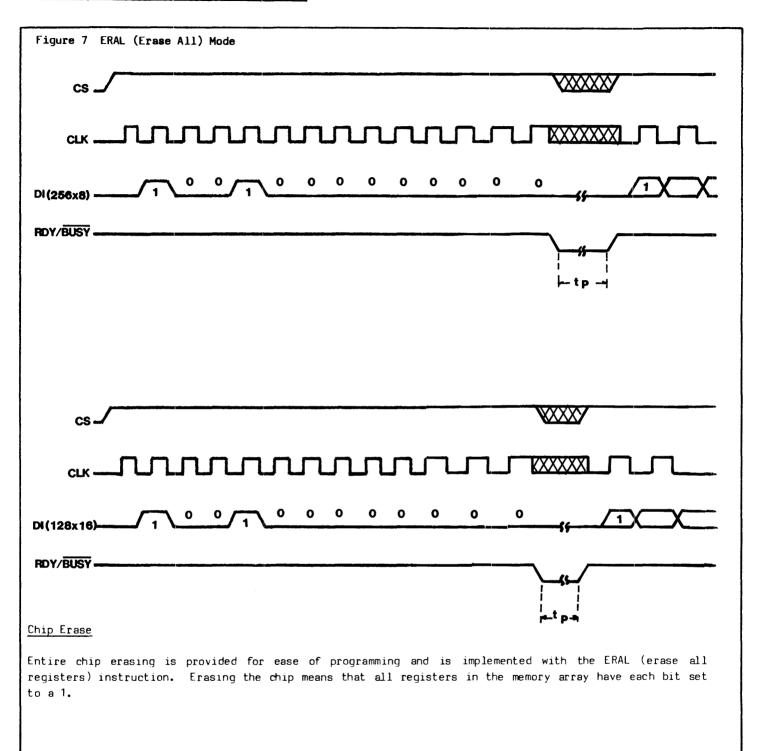

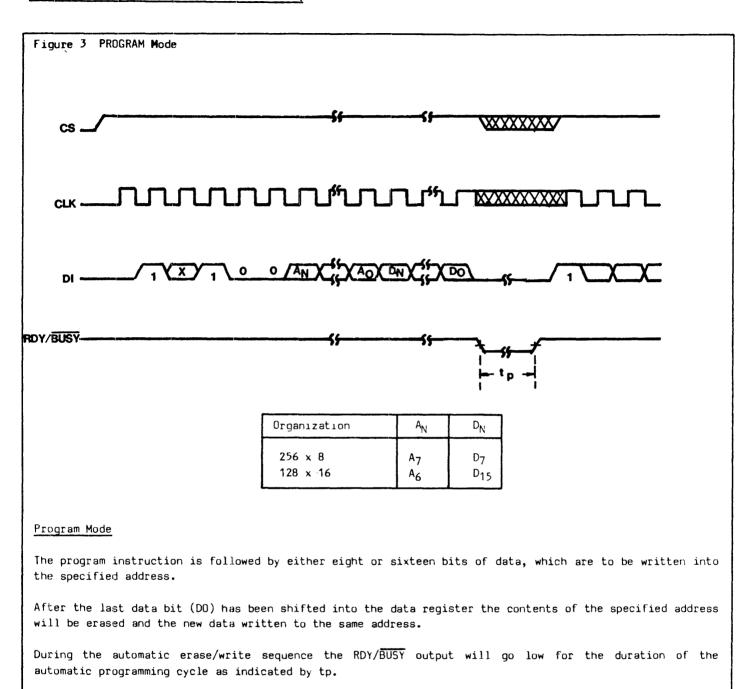

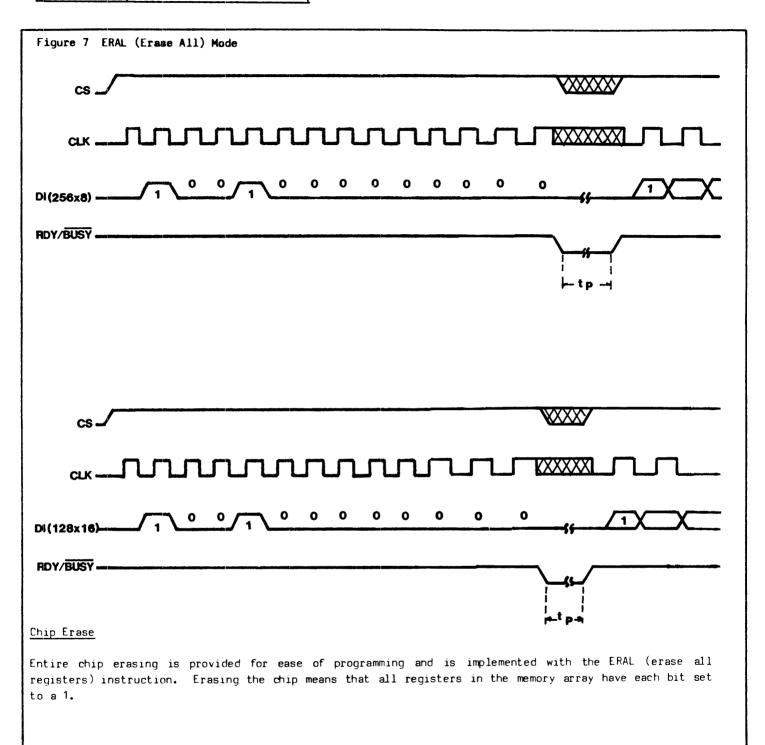

# READ OPERATION