## Microelectronics Data Catalog

## GENERAL

## GENERAL INSTRUMENT

## Microelectronics Data Catalog

### . Index

Part Number Index Functional Index

## 2, ROM

Read Only Memories Keyboard Encoder Character Generators Speech ROMs

### 3. Electrically Alterable Non-Volatile Memory/EANVM

Electrically Alterable Read Only Memories including Industrial/Military EAROMs Non-Volatile Static RAM

## 4. Microcomputer

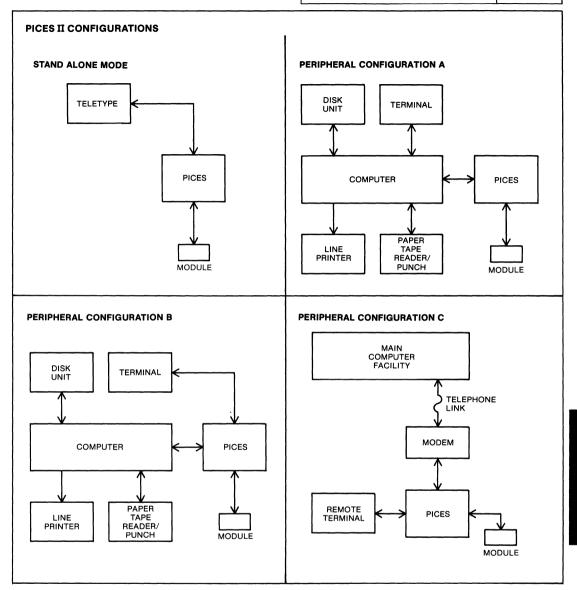

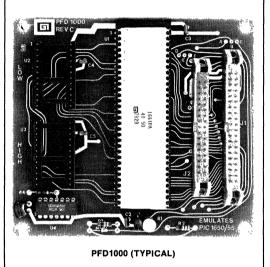

PIC Series PIC Development Series PICAL PICES II = PIC Field Demo Systems PIC Series Options = PIC Series Order Form

## 5. Audio

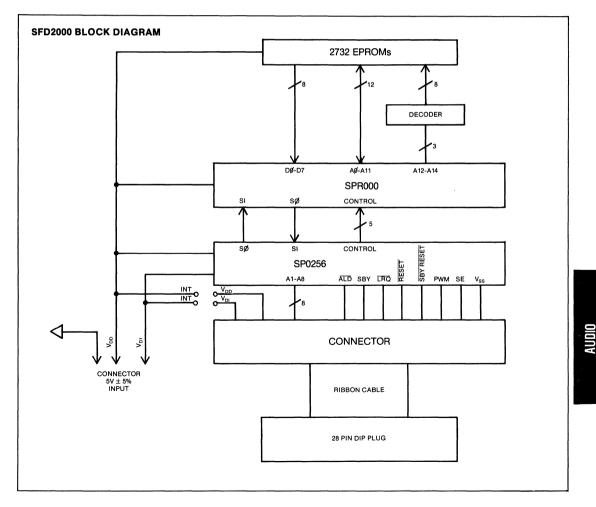

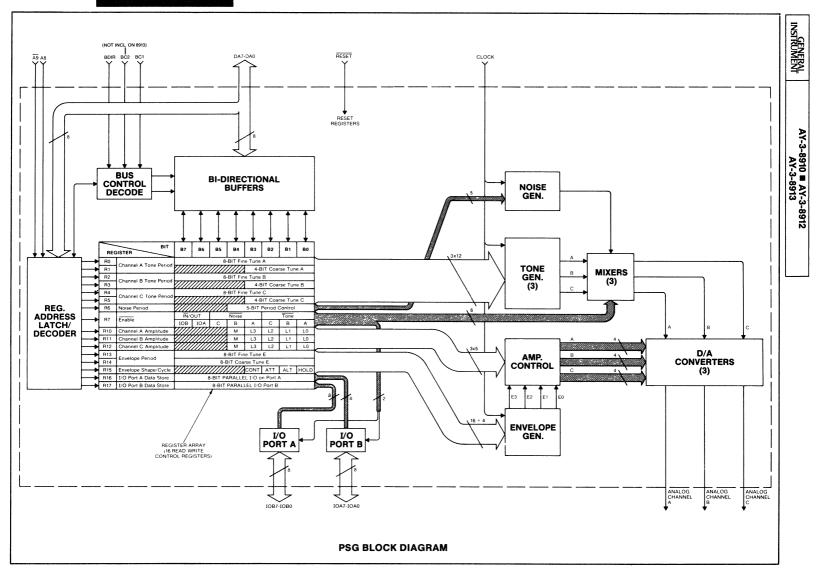

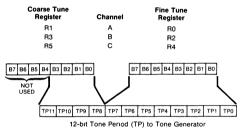

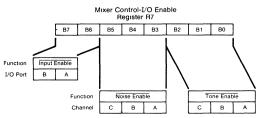

Speech Synthesis Sound Generation

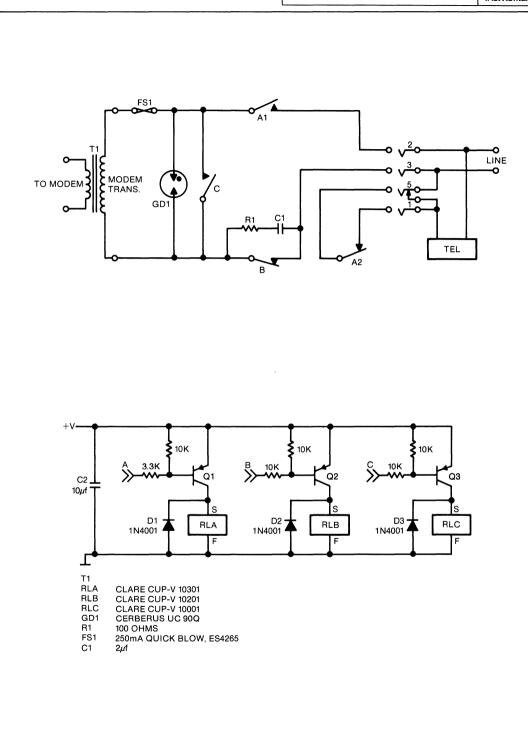

## 6. Telephony

Dialers # Multi-Frequency Generators Code Conversion # Programable Dialers

## . Data Communications

UAR/T Devices Clocks Appliances Remote Control

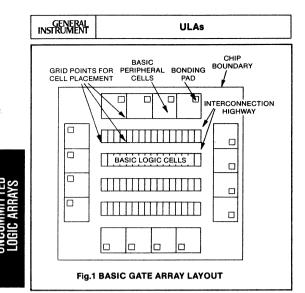

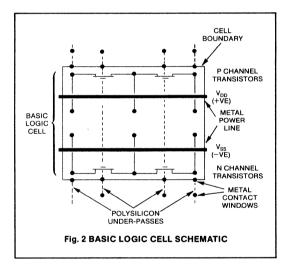

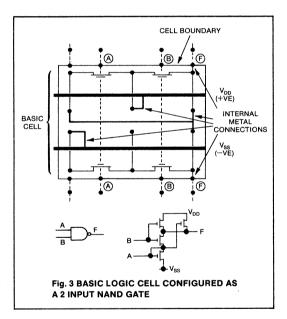

## 8. ULAs

High Speed CMOS Uncommitted Logic Arrays (ULAs)

## 9. Video

Video Display Video Graphics Video Games

## 10. Tuning

Television Synthesizer/Counter EAROM

## **11. General Information**

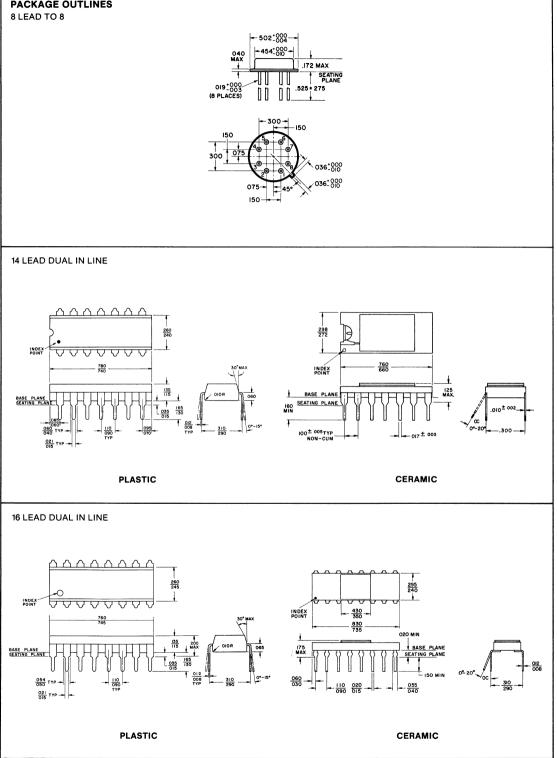

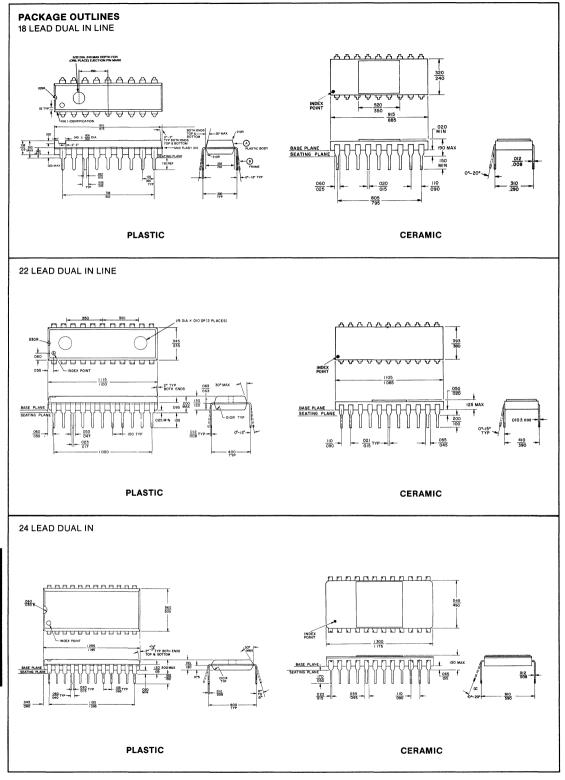

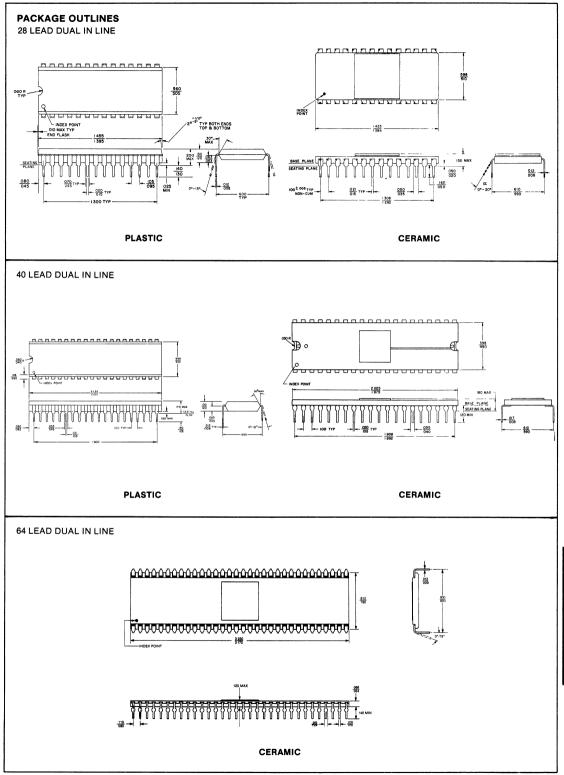

Company Profile Package Outlines Sales Offices

©Copyright 1982 GENERAL INSTRUMENT CORPORATION Printed in U.S.A. The information in this publication, including schematics, is suggestive only. General Instrument Corporation does not warrant, nor will it be responsible or liable for, (a) the accuracy of such information, (b) its use or (c) any infringement of patents or other rights of third parties.

## Part Number Index 1-3 Functional Index 1-4

### PART NUMBER INDEX

| NUMBER         PAGE         NUMBER         PAGE         NUMBER         PAGE           AY-3-1015D         7-4         ER1451         3-8         RA-3-9600         9-51           AY-3-1270         7-32         ER2051         3-14, 10-48         RO9128B/C/D         2-28           AY-3-2012         10-22         ER2051R         3-14, 10-48         RO9128B/C/D         2-28           AY-3-8211         10-4         ER2055R         3-17         RO9432B/C/D         2-14           AY-3-8217         7-42         ER2055R         3-17         RO9432B/C/D         2-14           AY-3-800         9-60         ER2810HR         3-28         RO9444B/AC/AD         2-22           AY-3-800         9-60         ER3400/IR         3-22         RO9664AB/AC/AD         2-22           AY-3-800         9-64         ER3400/IR         3-22         RO9864AB/AC/AD         2-25           AY-3-800         9-64         ER5716IR         3-32         RO-3-2513         2-54           AY-3-800         9-43         ER5816IR         3-36         RO-3-8316A/B/C/C         2-4           AY-3-800         9-43         ER5816IR         3-36         RO-3-9332/B/C/C         2-70           AY-3-810 | PART         |             | PART        |             | PART             |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-------------|------------------|--------------|

| AY-3-1270       7.32       ER2051       3-14, 10-48       RO9128B/C/D       2-28         AY-3-1350       .5-22       ER2051IR       3-14, 10-48       RO9128B/C/D       2-28         AY-3-4502       .2-42       ER2051IR       3-117       RO9432B/C/D       2-14         AY-3-4512       10-4       ER2055IR       3-117       RO9432B/C/D       2-14         AY-3-4470       7-42       ER2055IR       3-117       RO9432B/C/D       2-14         AY-3-4470       7-44       ER2055IR       3-17       RO9432B/C/D       2-14         AY-3-4500       9-60       ER2810IR       3-12       RO9464B/C/D       2-22         AY-3-4600       9-64       ER3400/IR       3-22       RO96082.34       RO9464B/C/D       2-22         AY-3-8600       9-64       ER3400/IR       3-22       RO9664B/C/D       2-25       AY-3-8600       2-34         AY-3-8600       9-64       ER57161       3-32       RO-3-2513       2-54         AY-3-8600       9-43       ER57161R       3-32       RO-3-9316HR       2-22         AY-3-8900       9-43       ER58161R       3-36       RO-3-9332HZ       2-70         AY-3-8910       5-14, 9-56       ER5911                                                           |              | PAGE        |             | PAGE        |                  | PAGE         |

| AY-3-1270       7.32       ER2051       3-14, 10-48       RO9128B/C/D       2-28         AY-3-1350       .5-22       ER2051IR       3-14, 10-48       RO9128B/C/D       2-28         AY-3-4502       .2-42       ER2051IR       3-117       RO9432B/C/D       2-14         AY-3-4512       10-4       ER2055IR       3-117       RO9432B/C/D       2-14         AY-3-4470       7-42       ER2055IR       3-117       RO9432B/C/D       2-14         AY-3-4470       7-44       ER2055IR       3-17       RO9432B/C/D       2-14         AY-3-4500       9-60       ER2810IR       3-12       RO9464B/C/D       2-22         AY-3-4600       9-64       ER3400/IR       3-22       RO96082.34       RO9464B/C/D       2-22         AY-3-8600       9-64       ER3400/IR       3-22       RO9664B/C/D       2-25       AY-3-8600       2-34         AY-3-8600       9-64       ER57161       3-32       RO-3-2513       2-54         AY-3-8600       9-43       ER57161R       3-32       RO-3-9316HR       2-22         AY-3-8900       9-43       ER58161R       3-36       RO-3-9332HZ       2-70         AY-3-8910       5-14, 9-56       ER5911                                                           |              |             |             |             | <u></u>          |              |

| AY-3-1350       5-22       ER2051IR       3-14, 10-48       RO91288/C/D       2-28         AY-3-4592       10-22       ER2051R       3-17       RO9460       2-39         AY-3-4572       7-42       ER2055IR       3-17       RO94328/C/D       2-12         AY-3-4270       7-42       ER2055IR       3-17       RO94328/C/D       2-12         AY-3-4270       7-44       ER2055IR       3-17       RO94328/C/D       2-22         AY-3-4500       9-60       ER210IR       3-22       RO94648/C/D       2-22         AY-3-4600       9-60       ER3400/IR       3-22       RO9580       2-37         AY-3-6605       9-65       ER3400/IR       3-22       RO9680       2-37         AY-3-6605       9-65       ER5716IR       3-32       RO-3-2513       2-54         AY-3-6607       9-66       ER5716IR       3-32       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER5716IR       3-32       RO-3-9332/R       2-74         AY-3-8910       5-14, 9-56       ER5816IR       3-36       RO-3-9332/R       2-77         AY-3-8910       5-14, 9-56       ER5816IR       3-36       RO-3-9332/R       2-710                                                                             |              |             |             |             | RA-3-9600        | 9-51         |

| AY-3-2012       10-22       ER2051 HR       3-14, 10-48       RO960.       2-39         AY-3-4592       2-42       ER2055.       3-17       RO9428/C/D       2-12         AY-3-48211       10-4       ER2055IR       3-17       RO9433B/C/D       2-12         AY-3-4877       7-48       ER2510IR       3-17       RO9433B/C/D       2-12         AY-3-4577       7-48       ER2510IR       3-17       RO9464B/C/D       2-22         AY-3-5600       9-60       ER3400/IR       3-22       RO9464B/C/D       2-22         AY-3-6600       9-64       ER3400/IR       3-22       RO9664B/C/D       2-25         AY-3-6600       9-68       ER5716IR       3-32       RO-3-2513       2-54         AY-3-6600       9-68       ER5716IR       3-32       RO-3-9316HR       2-42         AY-3-6900       9-43       ER5716IR       3-36       RO-3-932A/B/C       2-74         AY-3-6900       9-43       ER5616IR       3-36       RO-3-9332A/B/C       2-70         AY-3-8910       5-14, 9-56       ER5901I       3-20       RO-3-9333B/C       2-10         AY-3-8910       5-14, 9-56       ER5901R       3-41       RO-3-9333B/C       2-10                                                               |              |             |             |             | RO9128B/C/D      | 2-28         |

| AY3-4592       2.42       ER2055       3-17       RO9256       .2-31         AY3-8211       10-4       ER20551R       3-17       RO9432B/C/D       .2-12         AY3-8211       7.42       ER20551R       3-17       RO9432B/C/D       .2-14         AY3-8470       7.42       ER2051R       3-17       RO9464B/C/D       .2-22         AY3-8600       9-60       ER2810HR       3-28       RO9464AB/AC/AD/D       .2-22         AY3-8600       9-64       ER3400HR       3-22       RO9568       .2-34         AY3-8605       9-65       ER3040.       3-48       RO9864AB/AC/AD       .2-25         AY3-8606       9-66       ERS716       3-32       RO-3-9316A/B/C       .2-44         AY3-8606       9-66       ERS716       3-32       RO-3-9316A/B/C       .2-44         AY3-8607       9-68       ERS716       3-32       RO-3-9316A/B/C       .2-44         AY3-8900       9-43       ERS8161R       3-36       RO-3-9332A/B/C       .2-10         AY3-8900       9-43       ERS8161R       3-36       RO-3-9332A/B/C       .2-10         AY3-8900       5-14       9-56       ERS901IR       3-20       RO-3-9333H/R       .2-10     <                                                              |              |             | ER2051HR    | 3-14, 10-48 |                  |              |

| AY3-8470       7-42       ER2055HR       3-17       RO43435/C/D       2-14         AY3-8475       7-48       ER2010H       3-28       RO444B/C/D       2-22         AY3-8500       9-60       ER2810HR       3-28       RO9464AB/AC/AD       2-22         AY3-8600       9-60       ER3400       3-22       RO9568       2-34         AY3-8605       9-65       ER3400/HR       3-22       RO9864AB/AC/AC/AD       2-22         AY3-8607       9-66       ER5304       3-48       RO9864AB/AC/AD       2-25         AY3-8610       9-70       ER5716HR       3-32       RO-3-9316A/B/C       2-44         AY3-8610       9-70       ER5716HR       3-32       RO-3-9316A/B/C       2-44         AY3-8610       9-72       ER5716HR       3-32       RO-3-93316/R/C       2-4         AY3-8900       9-43       ER5816HR       3-36       RO-3-9332A/B/C       2-70         AY3-8910       5-14, 9-56       ER59011       3-20       RO-3-9332HR       2-10         AY3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9334/B/C       2-16         AY3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9364/R       2-10                                                                |              |             |             |             |                  |              |

| AY3-8475       7-46       ER3101R       3-28       RO9464AB/xC/D       2-22         AY3-8600       9-60       ER3400       3-22       RO9464AB/xC/D       2-22         AY3-8600-1       9-60       ER3400/IR       3-22       RO9864AB/xC/D       2-22         AY3-8605       9-65       ER3400/IR       3-22       RO9864B/xC/D       2-25         AY3-8605       9-66       ER304       3-48       RO9864B/xC/D       2-25         AY3-8606       9-66       ER304       3-48       RO9864AB/AC/AD       2-25         AY3-8607       9-68       ER5716       3-32       RO-3-2513       2-54         AY3-8600       9-43       ER57161R       3-32       RO-3-9316/kPC       2-4         AY3-8900       9-43       ER58161R       3-36       RO-3-9332/kPC       2-70         AY3-8900       5-14, 9-56       ER5901       3-20       RO-3-9332/kPC       2-10         AY3-8910       5-14, 9-56       ER5901R       3-20       RO-3-9333HR       2-72         AY3-89010       6-18       ER59161       3-41       RO-3-9364H/C       2-16         AY3-9400       6-18       ER59161R       3-41       RO-3-96502       9-46         <                                                                      |              |             |             |             |                  |              |

| AY-3-8500       9-60       ER2810HR       3-28       FO9464AB/AC/AD       2-22         AY-3-8605       9-64       ER3400/IR       3-22       RO9668/C/D       2-34         AY-3-8605       9-65       ER3400HR       3-22       RO9664/C/D       2-25         AY-3-8605       9-66       ER5304       3-48       RO9664/C/D       2-25         AY-3-8607       9-68       ER5716       3-32       RO-3-2513       2-54         AY-3-8607       9-68       ER5716       3-32       RO-3-2513       2-54         AY-3-8607       9-68       ER5716       3-32       RO-3-9316A/B/C       2-40         AY-3-8900       9-43       ER5816       3-36       RO-3-9332HR       2-70         AY-3-8910       5-14, 9-56       ER5916HR       3-36       RO-3-9332HR       2-70         AY-3-8915       5-57       ER5916HR       3-20       RO-3-9364B/C       2-16         AY-3-8915       9-57       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9900       6-18       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9710       9-28       LA03       8-3       SFD2000       5-15         AY-3-9710<                                                                          |              |             |             |             |                  |              |

| AY-3-8500-1       9-60       ER3400       3-22       RO9508       2-34         AY-3-8603       9-64       ER3400//R       3-22       RO9608       2-37         AY-3-8605       9-66       ER5304       3-48       RO9664AE/AC/AD       2-25         AY-3-8607       9-66       ER5716       3-32       RO-3-2513       2-54         AY-3-8610       9-70       ER57161R       3-32       RO-3-2513       2-54         AY-3-8600       9-43       ER58161R       3-36       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER58161R       3-36       RO-3-9332A/B/C       2-7         AY-3-8910       5-14, 9-56       ER59161R       3-36       RO-3-9332A/B/C       2-70         AY-3-8912       5-14, 9-56       ER59161R       3-20       RO-3-9333HR       2-10         AY-3-8913       5-14, 9-56       ER59161R       3-41       RO-3-9364B/C       2-16         AY-3-8910       6-18       ER59161R       3-41       RO-3-9364B/C       2-16         AY-3-9400       6-18       ER59161R       3-41       RO-3-9364B/C       2-16         AY-3-9735       9-33       LA05       8-3       SPD200       5-15                                                                               |              |             |             |             |                  |              |

| AY-3-8603       9-64       ER3400//R       3-22       RO9868/C/D       2-25         AY-3-8605       9-65       ER3300/R       3-48       RO9864B/C/D       2-25         AY-3-8607       9-68       ER5716       3-32       RO9864B/AC/AD       2-25         AY-3-8610       9-70       ER57161R       3-32       RO-3-2513       2-54         AY-3-8610       9-72       ER57161R       3-32       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER58161R       3-36       RO-3-9332A/B/C       2-7         AY-3-8910       5-14, 9-56       ER5901R       3-20       RO-3-9332HR       2-70         AY-3-8913       5-14, 9-56       ER5901R       3-41       RO-3-9334B/C       2-10         AY-3-8913       5-14, 9-56       ER5901R       3-41       RO-3-9336B/C       2-10         AY-3-8913       5-14, 9-56       ER59161R       3-41       RO-3-9364B/C       2-16         AY-3-9910       6-18       ER59161R       3-41       RO-3-9364B/C       2-16         AY-3-9735       9-33       A       A-3-930       B-22       A03       B-3       SPD200       5-15         AY-5-8105       10-44       LA10       8-3                                                                   |              |             |             |             |                  |              |

| AY-3-8605       9-65       ER3040HR       3-22       RO9864B/C/D       2-25         AY-3-8607       9-66       ER5716       3-32       RO9864AB/AC/AD       2-25         AY-3-8607       9-66       ER5716       3-32       RO-3-2513       2-54         AY-3-8610       9-70       ER5716HR       3-32       RO-3-2513       2-54         AY-3-8610       9-70       ER5716HR       3-32       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER5816HR       3-36       RO-3-9332A/B/C       2-7         AY-3-8910       5-14, 9-56       ER5816HR       3-36       RO-3-9333B/C       2-10         AY-3-8912       5-14, 9-56       ER5901HR       3-20       RO-3-9333B/C       2-10         AY-3-8915       9-57       ER5901HR       3-20       RO-3-9364B/C       2-16         AY-3-8910       6-18       ER5916IR       3-41       RO-3-9364B/C       2-10         AY-3-9400       6-18       ER5916HR       3-41       RO-3-9364B/C       2-10         AY-3-9710       9-28       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9735       9-33       AY-5-9153       RO-3-9502       9-46         AY-5                                                                 |              |             |             |             |                  |              |

| AY-3-8606       9-66       ER5304       3-48       RO9864AB/AC/AD       2-25         AY-3-8607       9-68       ER5716       3-32       RO-3-2513       2-54         AY-3-8610       9-72       ER5716IR       3-32       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER5816       3-36       RO-3-9332A/B/C       2-7         AY-3-8900-1       9-43       ER5816IR       3-36       RO-3-9332A/B/C       2-7         AY-3-8910       5-14, 9-56       ER5901       3-20       RO-3-9333B/C       2-10         AY-3-8912       5-14, 9-56       ER5901HR       3-20       RO-3-9333B/C       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-93364B/C       2-16         AY-3-9900       6-18       ER5916H       3-41       RO-3-9366B/C       2-19         AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SPD200       5-15         AY-5-8116       7-13       LA10       8-3       SPD220       5-15         AY-5-8136       7-13       LA10       8-3       SPD220       5-15         AY-5-91                                                                          |              |             |             |             |                  |              |

| AY-3-8607       9-68       ER5716       3-32       RO-3-2513       2-54         AY-3-8610       9-70       ER57161R       3-32       RO-3-9316A/B/C       2-4         AY-3-8600       9-43       ER57161R       3-32       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER58161R       3-36       RO-3-9316A/B/C       2-7         AY-3-8910       5-14, 9-56       ER55161R       3-36       RO-3-93321/B/C       2-7         AY-3-8912       5-14, 9-56       ER5901       3-20       RO-3-9333B/C       2-10         AY-3-8915       5-14, 9-56       ER5901/IR       3-20       RO-3-9333B/C       2-10         AY-3-8915       9-57       ER5901/IR       3-20       RO-3-9333B/C       2-10         AY-3-9400       6-18       ER5916IR       3-41       RO-3-9364B/C       2-16         AY-3-9710       9-28       ER5916IR       3-41       RO-3-9503       9-49         AY-3-9705       9-33       AY-3-900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15       SP0256       5-15         AY-5-9151A/B       6-4       PIC16C5                                                         |              |             |             |             |                  |              |

| AY-3-8610       9-70       ER5716IR       3-32       RO-3-2513       2-54         AY-3-8765       9-72       ER5716HR       3-32       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER5816       3-36       RO-3-9316A/B/C       2-4         AY-3-8900       9-43       ER5816       3-36       RO-3-9332/H       2-7         AY-3-8910       5-14, 9-56       ER5901       3-20       RO-3-93332/H       2-7         AY-3-8913       5-14, 9-56       ER5901       3-20       RO-3-9333HR       2-10         AY-3-8915       9-57       ER5901HR       3-20       RO-3-9333HR       2-16         AY-3-8916       9-57       ER5901HR       3-20       RO-3-9336H/C       2-16         AY-3-9910       6-18       ER5916IR       3-41       RO-3-936B/C       2-16         AY-3-9735       9-33       LA05       8-3       RO-3-9504       2-32, 9-54         AY-3-9735       9-33       LA05       8-3       RO-3-9504       2-32, 9-54         AY-5-8116T       7-13       LA15       8-3       SFD2000       5-15         AY-5-8136       7-13       LA20       8-3       SP0256       5-5         AY-5-9152/B <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                  |              |             |             |             |                  |              |

| AY-3-8900       9-43       ER5816       3-36       RO-3-9316HR       2-4         AY-3-8900-1       9-43       ER5816IR       3-36       RO-3-9322/R/C       2-7         AY-3-8910       5-14, 9-56       ER5801HR       3-36       RO-3-9332/R/C       2-10         AY-3-8912       5-14, 9-56       ER5901       3-20       RO-3-9333HR       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9334HR       2-10         AY-3-8915       9-57       ER5901HR       3-20       RO-3-9364B/C       2-16         AY-3-8916       9-57       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9400       6-18       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9410       6-18       ER5916HR       3-41       RO-3-9364B/C       2-19         AY-3-9710       9-28       ER5916HR       3-41       RO-3-9504       2-32, 9-54         AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-816       7-13       LA15       8-3       SP0250       5-15         AY-5-9154/A       6-4       PIC16C55       4-62       SP0256       5-5                                                                          |              |             |             |             | RO-3-2513        | 2-54         |

| AY-3-8900-1       9-43       ER3816IR       3-36       RO-3-9332A/B/C       2-7         AY-3-8910       5-14, 9-56       ER5816HR       3-36       RO-3-9332PR       2-7         AY-3-8912       5-14, 9-56       ER5901       3-20       RO-3-9333PR       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9334PR       2-10         AY-3-8915       9-57       ER5901HR       3-20       RO-3-9334PR       2-10         AY-3-8915       9-57       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9400       6-18       ER5916HR       3-41       RO-3-9364B/C       2-19         AY-3-9710       9-28       ER5916HR       3-41       RO-3-9502       9-46         AY-3-9700       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8136       7-13       LA15       6-3       SP0250       5-12         AY-5-8136T       7-13       LA20       8-3       SP0256       5-55         AY-5-9152/B       6-4       PIC16C55       4-62       SPR026       5-59         AY-5-9153A/B<                                                                          | AY-3-8765    | <b>9-72</b> | ER5716HR    | 3-32        | RO-3-9316A/B/C . |              |

| AY-3-8910       5-14, 9-56       ER3816HR       3-36       RO-3-9332HR       2-7         AY-3-8912       5-14, 9-56       ER5901       3-20       RO-3-9333B/C       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9333B/C       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9333B/C       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9332HR       2-10         AY-3-8913       5-14, 9-56       ER5901HR       3-20       RO-3-9333HR       2-10         AY-3-9410       6-18       ER5916IR       3-41       RO-3-9364B/C       2-19         AY-3-9710       9-28       ER5916HR       3-41       RO-3-9503       9-49         AY-3-9735       9-33       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8167       7-13       LA20       8-3       SFD2000       5-15         AY-5-8167       7-13       LA20       8-3       SP0232       5-9         AY-5-9151A/B       6-4       PIC16C55       4-62       SP0256       5-5 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td></t<>           |              |             |             |             |                  |              |

| AY-3-8912       5-14, 9-56       ER5901       3-20       RO-3-9333B/C       2-10         AY-3-8913       5-14, 9-56       ER5901IR       3-20       RO-3-9333HR       2-10         AY-3-8915       9-57       ER5901HR       3-20       RO-3-9364B/C       2-10         AY-3-9910       6-18       ER5916IR       3-41       RO-3-9366B/C       2-16         AY-3-9710       9-28       ER5916IR       3-41       RO-3-9365B/C       2-19         AY-3-9700       6-22       LA03       8-3       RO-3-9502       9-46         AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8116       7-13       LA20       8-3       SFD2000       5-15         AY-5-8136T       7-13       LA20       8-3       SP0250       5-12         AY-5-9151A/B       6-4       PIC16C55       4-62       SP0256       S-512         AY-5-9153A/B       6-4       PIC16C55       4-62       SP0256       S-512         AY-5-9154A       6-4       PIC16C55       4-62       SP0256       S-512         AY-5-9154A       6-                                                                                   |              |             |             |             |                  |              |

| AY-3-8913       5-14, 9-56       ER5901IR       3-20       RO-3-9333HR       2-10         AY-3-8915       9-57       ER5901HR       3-20       RO-3-9364B/C       2-16         AY-3-9400       6-18       ER5916IR       3-41       RO-3-9364HR       2-16         AY-3-9410       6-18       ER5916IR       3-41       RO-3-9365B/C       2-19         AY-3-9710       9-28       ER5916HR       3-41       RO-3-9365B/C       2-19         AY-3-9700       6-22       LA03       8-3       RO-3-9502       9-46         AY-3-9900       6-22       LA03       8-3       RO-3-9503       9-49         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8116       7-13       LA20       8-3       SFD2200       5-9         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-8136       7-13       PFD SYSTEMS       4-138       SP0250       5-12         AY-5-915A/B       6-4       PIC16C55       4-62       SP0256       5-5         AY-5-915A/B       6-4       PIC16C50       9-15       SPR032       2-70         AY-5-915A       6-14 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td></t<>                           |              |             |             |             |                  |              |

| AY-3-8915       9-57       ER5901HR       3-20       RO-3-9364B/C       2-16         AY-3-9400       6-18       ER5916       3-41       RO-3-9364B/C       2-16         AY-3-9410       6-18       ER5916HR       3-41       RO-3-9364B/C       2-16         AY-3-9710       9-28       ER5916HR       3-41       RO-3-9365B/C       2-19         AY-3-9700       9-28       ER5916HR       3-41       RO-3-9502       9-46         AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8136       7-13       LA20       8-3       SP0232       5-9         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-9153/B       6-4       PIC16C55       4-62       SP0256       5-5         AY-5-9153/B       6-4       PIC16C55       4-62       SPR025       5-9         AY-5-9153/B       6-4       PIC16C55       4-62       SPR022       5-9         AY-5-9153/A       6-4       PIC1650A       4-16       SPR022       2-70         AY-5-9158       6-14       PIC1                                                                                            | AY-3-8912    | 5-14, 9-56  |             |             |                  |              |

| AY-3-9400       6-18       ER5916       3-41       RO-3-9364HR       2-16         AY-3-9410       6-18       ER5916IR       3-41       RO-3-9365B/C       2-19         AY-3-9710       9-28       ER5916IR       3-41       RO-3-9362B/C       2-19         AY-3-9700       9-28       ER5916IR       3-41       RO-3-9502       9-46         AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA15       8-3       SFD2000       5-15         AY-5-8116       7-13       LA15       8-3       SP0232       5-9         AY-5-8136T       7-13       LA20       8-3       SP0250       5-15         AY-5-9153A/B       6-4       PIC16C55       4-62       SP0256       5-5         AY-5-9153A/B       6-4       PIC16C55       4-62       SP0256       5-9         AY-5-9153A/B       6-4       PIC16C55       4-62       SPR016       2-64         AY-5-9153A       6-11       PIC1650-36       9-15       SPR032       2-73         AY-5-9153A       6-14       PIC1650A       4-16       SPR032       2-73         CY1610       9-22       PIC165                                                                                            |              |             |             |             |                  |              |

| AY-3-9410       .6-18       ER5916IR       .3-41       RO-3-9365B/C       .2-19         AY-3-9710       .9-28       ER5916IR       .3-41       RO-3-9502       .9-48         AY-3-9735       .9-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |             |             |             |                  |              |

| AY-3-9710       9-28       ER5916HR       3-41       RO-3-9502       9-46         AY-3-9735       9-33       LA03       8-3       RO-3-9503       9-49         AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8116       7-13       LA15       8-3       SP0232       5-9         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-8136       7-13       PFD SYSTEMS       4-138       SP0256       5-5         AY-5-9151A/B       6-4       PIC16C55       4-62       SPR000       5-9         AY-5-9153A/B       6-4       PIC16C50       4-62       SPR016       2-64         AY-5-9158       6-11       PIC16C0       10-33       SPR016       2-64         AY-5-9158       6-14       PIC1650-536       9-15       SPR032       2-70         AY-5-9559       6-14       PIC1650A       4-49       SPR128       2-73         CY1010       9-22       PIC1655A       4-38                                                                                                     |              |             |             |             |                  |              |

| AY-3-9735       .9-33         AY-3-9900       .6-22         LA03       .8-3         LA05       .8-3         LA05       .8-3         LA05       .8-3         LA05       .8-3         LA05       .8-3         LA05       .8-3         AY-5-8105       .10-44         LA10       .8-3         AY-5-8116       .7-13         LA20       .8-3         SPD200       .5-15         AY-5-8136       .7-13         LA20       .8-3         SP0232       .5-9         SP0250       .5-12         SP0256       .5-5         SP0256       .5-5         SP0256       .5-5         SP0256       .5-9         SP0256       .5-12         SP0250       .5-12         SP0250       .5-13         SP0250       .5-14         PIC16050-20       10-33                                                                                                                                                                                                                                                                                                          |              |             |             |             |                  |              |

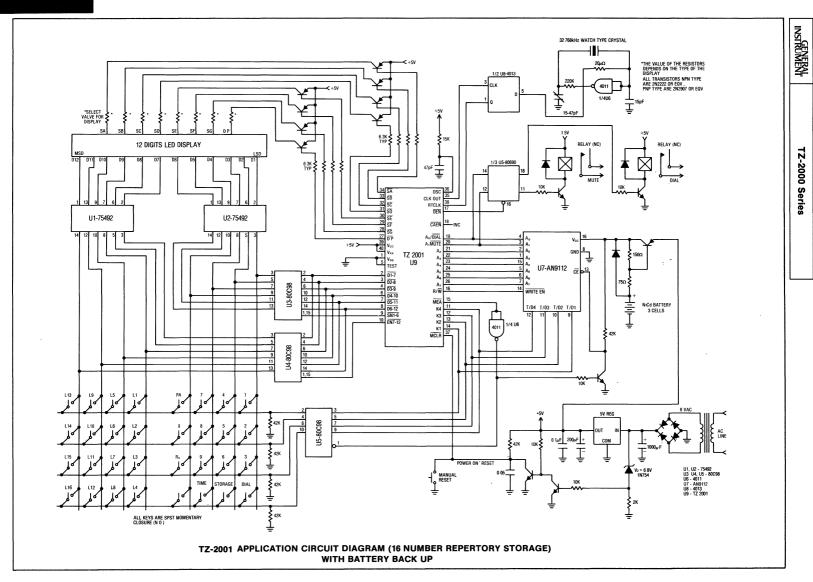

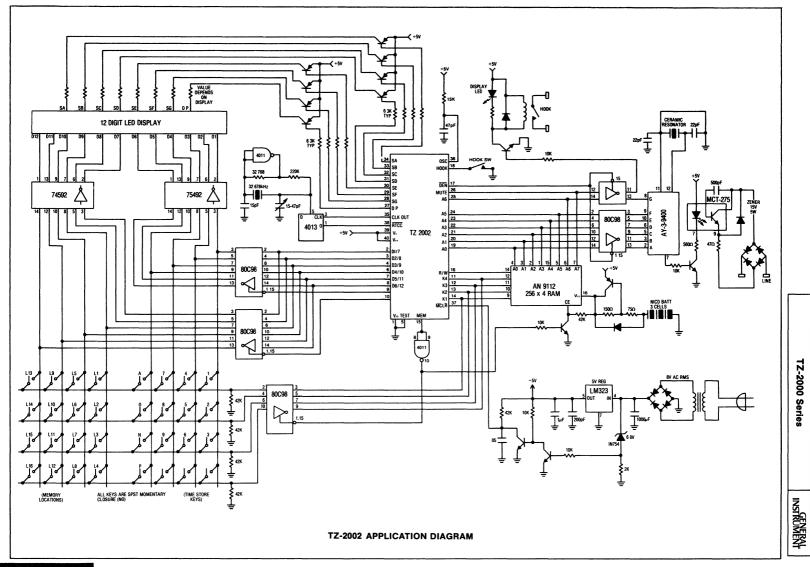

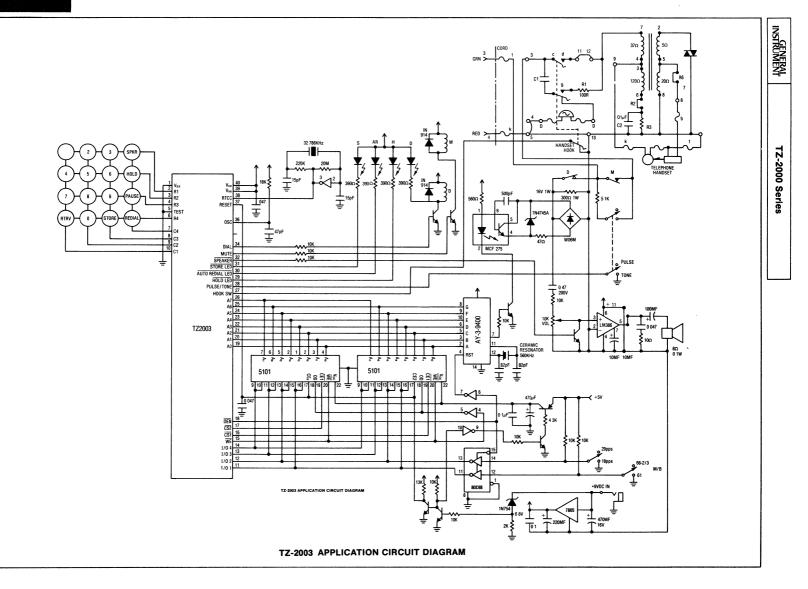

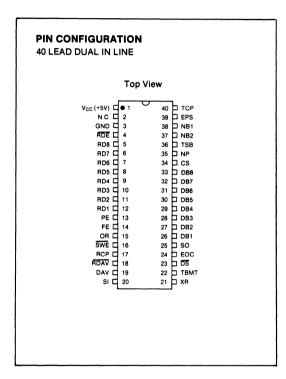

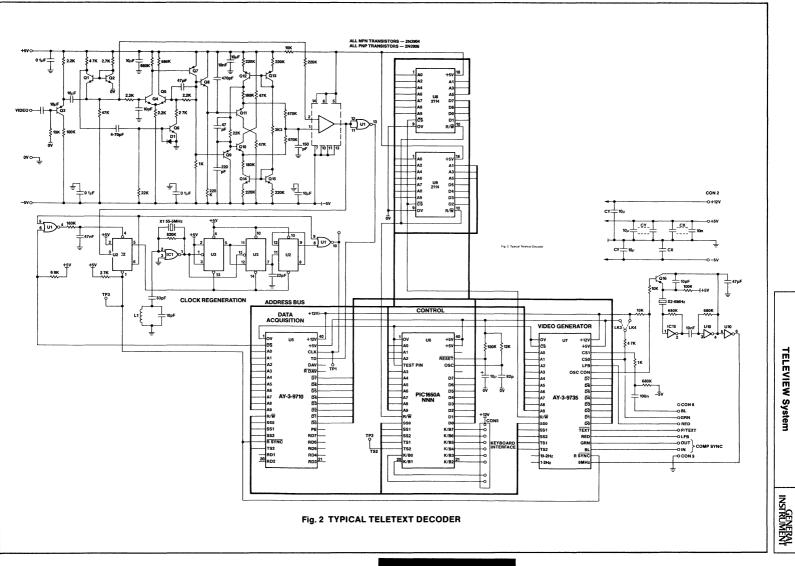

| AY-3-9900       6-22       LA03       8-3       RO-3-9504       2-32, 9-54         AY-5-8105       10-44       LA10       8-3       SFD2000       5-15         AY-5-8116       7-13       LA15       8-3       SFD2000       5-15         AY-5-8116       7-13       LA10       8-3       SFD2000       5-15         AY-5-8116T       7-13       LA20       8-3       SP0232       5-9         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-9151A/B       6-4       PIC16C55       4-62       SP0256       5-5         AY-5-9153A/B       6-4       PIC16C55       4-62       SPR000       5-9         AY-5-9158       6-11       PIC1650-020       10-33       SPR016       2-64         AY-5-9158       6-11       PIC1650A       4-428       SPR032       2-70         AY-5-9559       6-14       PIC1655A       4-28       SPR032       2-73         PIC1655A       4-64       PIC1655A       4-28       TELEVIEW SYSTEM       9-4         PIC1655A       4-28       PIC1655A       4-28       TZ-2001       6-30         CT2010       10-27       PIC1665       4-                                                                                                     |              |             |             |             |                  |              |

| AY-5-8105       10-44       LA05       8-3       SFD2000       5-15         AY-5-8116       7-13       LA15       8-3       SFD2000       5-15         AY-5-8116       7-13       LA15       8-3       SP0250       5-12         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-8136       7-13       LA20       8-3       SP0250       5-12         AY-5-8136       7-13       PFD SYSTEMS       4-138       SP0256       5-5         AY-5-9151A/B       6-4       PIC16C55       4-62       SP0256-AL2       5-9         AY-5-9152/B       6-4       PIC16C55       4-62       SP0256-AL2       5-9         AY-5-9153A/B       6-4       PIC16C53       4-62       SP000       5-9         AY-5-9158       6-11       PIC1650A       4-10       SPR016       2-64         AY-5-9158       6-14       PIC1650A       4-4       9-9       SPR128       2-73         AY-5-9158       6-14       PIC1655A       4-38       TELEVIEW SYSTEM       9-4         CK3300       7-18       PIC1655A       4-32       TZ-2001       6-30         CT2010       10-27       PIC1665<                                                                                                     |              |             | 1 403       | 8-3         |                  |              |

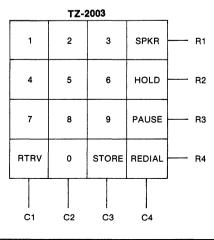

| AY-5-8116       7-13       LA15       8-3         AY-5-8116T       7-13       LA20       8-3         AY-5-8136       7-13       LA20       8-3         AY-5-8136T       7-13       PFD SYSTEMS       4-138         AY-5-9151A/B       6-4       PIC16C55       4-62         AY-5-9153A/B       6-4       PIC16C63       4-110         AY-5-9153A/B       6-4       PIC16C63       4-110         AY-5-9153A/B       6-4       PIC1650-020       10-33         AY-5-9158       6-11       PIC1650-36       9-15         AY-5-9559       6-14       PIC1650A       4-4, 9-9         SPR032       2-70         SPR032       2-70         PIC1655A       4-38         CP1610       9-22         PIC1655A       4-38         PIC1655A       4-38         CP1610       9-22         PIC1665A       4-72         TZ-2001       6-30         TZ-2003       6-30         TZ-2003       6-30         TZ-2003       6-30         TZ-2003       6-30         TZ-2003       6-30         TZ-2003       6-30                                                                                                                                                                                                                 |              |             |             |             |                  |              |

| AY-5-8116T       .7-13       LA20       .8-3       SP0232       .5-9         AY-5-8136       .7-13       PFD SYSTEMS       .4-138       SP0250       .5-12         AY-5-9151A/B       .6-4       PIC 16C55       .4-62       SP0256       .5-5         AY-5-9152/B       .6-4       PIC 16C55       .4-62       SP0256       .5-5         AY-5-9153A/B       .6-4       PIC 16C63       .4-110       SPR000       .5-9         AY-5-9158       .6-11       PIC 1650-020       .10-33       SPR016       .2-64         AY-5-9158       .6-11       PIC 1650-366       .9-15       SPR032       .2-70         AY-5-9559       .6-14       PIC 1650A       .4-49.9       SPR128       .2-73         PIC 1650A       .4-32       PIC 1655A       .4-62       YE-2001       .6-30         PIC 1655A       .4-38       PIC 1655A       .4-38       YE-2001       .6-30         PIC 1655A       .4-32       YE-2001       .6-30       YE-2003       .6-30         CP1610       .9-22       PIC 1665       .4-121       YE-2003       .6-30         CT2010       10-27       PIC 1665       .4-121       YE-2003       .6-30         PIC 167                                                                          | AY-5-8105    | 10-44       | LA10        |             | SFD2000          |              |

| AY-5-8136       .7-13       PFD SYSTEMS       4-138       SP0250       .5-12         AY-5-9151A/B       .6-4       PIC 16C55       .4-62       SP0256       .5-5         AY-5-9153A/B       .6-4       PIC 16C55       .4-62       SP0000       .5-9         AY-5-9153A/B       .6-4       PIC 16C55       .4-62       SP0000       .5-9         AY-5-9153A/B       .6-4       PIC 1650-020       10-33       SPR016       .2-64         AY-5-9158       .6-11       PIC 1650-366       .9-15       SPR032       .2-70         AY-5-9559       .6-14       PIC 1650A       .4-4, 9-9       SPR128       .2-73         PIC 1650A       .4-49.9       SPR128       .2-73       SPR128       .2-73         PIC 1655A       .4-38       PIC 1655A       .4-38       TELEVIEW SYSTEM       .9-4         CT2010       .0-27       PIC 1665       .4-121       TZ-2001       .6-30         CT2017       10-29       PIC 1665       .4-121       VSM2032       .5-10         ECONOMEGA III       .10-8       PICAL       .4-32       VSM2032       .5-10         ER0082       .3-5       PICES II       .4-134       .4-134       .4-134 <td>AY-5-8116</td> <td>7-13</td> <td>LA15</td> <td></td> <td></td> <td></td> | AY-5-8116    | 7-13        | LA15        |             |                  |              |

| AY-5-8136T       7-13       PFD SYSTEMS       4-138       SP0256       5-5         AY-5-9151A/B       6-4       PIC16C55       4-62       SP0256-AL2       5-9         AY-5-9153A/B       6-4       PIC16C63       4-110       SPR000       5-9         AY-5-9153A/B       6-4       PIC16C63       4-110       SPR000       5-9         AY-5-9158       6-11       PIC1650-020       10-33       SPR016       2-64         AY-5-9559       6-14       PIC1650A       9-15       SPR032       2-70         AY-5-9559       6-14       PIC1650A       4-4, 9-9       SPR128       2-73         PIC1650A       4-44, 9-9       SPR128       2-73       SPR128       2-73         PIC1650A       4-48       PIC1655A       4-38       TELEVIEW SYSTEM       9-4         CT2010       10-27       PIC1655A       4-38       TZ-2001       6-30         CT2017       10-29       PIC1665       4-121       VSM2032       5-10         ECONOMEGA III       10-8       PICAL       4-32       VSM2032       5-10         ER0082       3-5       PICES II       4-134       4-134       14-134                                                                                                                        |              |             | LA20        |             |                  |              |

| AY-5-9151A/B       6-4         AY-5-9152/B       6-4         AY-5-9153A/B       6-4         AY-5-9153A/B       6-4         AY-5-9153A/B       6-4         AY-5-9153A/B       6-4         AY-5-9153A/B       6-4         AY-5-9158       6-11         PIC1650-020       10-33         SPR016       2-64         SPR032       2-70         SPR032       2-70         SPR032       2-70         SPR032       2-73         PIC1650A       4-16         CK3300       7-18         PIC1655A       4-38         CP1610       9-22         PIC1655A       4-38         CT2010       10-27         CT2010       10-27         PIC1655       4-121         PIC1650       4-121         PIC1670       4-85         VSM2032       5-10         ECONOMEGA III       10-8         ECONOMEGA IV       10-19         PICAL       4-134                                                                                                                                                                                                                                                                                                                                                                                        |              |             |             |             |                  |              |

| AY-5-9152/B       .6-4       PIC16C55       .4-62         AY-5-9153A/B       .6-4       PIC16C63       .4-110         AY-5-9153A/B       .6-4       PIC16C63       .4-110         AY-5-9154A       .6-4       PIC1650-020       10-33         AY-5-9158       .6-11       PIC1650-536       .9-15         AY-5-9559       .6-14       PIC1650A       .4-4, 9-9         PIC1650XT       .4-16       PIC1650XT       .4-16         CK3300       .7-18       PIC1655A       .4-38         CP1610       .9-22       PIC1655XT       .4-50         PIC1655A       .4-38       TZ-2001       .6-30         CT2010       10-27       PIC1665       .4-121         PIC1670       .4-85       VSM2032       .5-10         ECONOMEGA III       10-8       PICAL       .4-32         ER0082       .3-5       PICES II       .4-134                                                                                                                                                                                                                                                                                                                                                                                       |              |             | PFD SYSTEMS | 4-138       |                  |              |

| AY-5-9153A/B       6-4       PIC16C63       4-110       SPR000       5-9         AY-5-9154A       6-4       PIC1650-020       10-33       SPR016       2-64         AY-5-9158       6-11       PIC1650-536       9-15       SPR032       2-70         AY-5-9559       6-14       PIC1650A       4-4, 9-9       SPR128       2-73         CK3300       7-18       PIC1655A       4-38       TELEVIEW SYSTEM       9-4         CP1610       9-22       PIC1655A       4-38       TZ-2001       6-30         CT2010       10-27       PIC1665       4-72       TZ-2002       6-30         CT2017       10-29       PIC1665       4-121       VSM2032       5-10         ECONOMEGA III       10-8       PICAL       4-32       VSM2032       5-10         ER0082       3-5       PICES II       4-134       4-134       4-134                                                                                                                                                                                                                                                                                                                                                                                     |              |             | 51010075    | 4.00        | SP0256-AL2       | 5-9          |

| AY-5-9154A       6-4       PIC1650-020       10-33       SPR016       2-64         AY-5-9158       6-11       PIC1650-536       9-15       SPR032       2-70         AY-5-9559       6-14       PIC1650A       4-4, 9-9       SPR128       2-73         PIC1650A       4-44, 9-9       PIC1650A       4-28       TELEVIEW SYSTEM       9-4         CK3300       7-18       PIC1655A       4-38       TZ-2001       6-30         CP1610       9-22       PIC1655A       4-72       TZ-2001       6-30         CT2010       10-27       PIC1665       4-72       TZ-2003       6-30         CT2017       10-29       PIC1665       4-121       VSM2032       5-10         ECONOMEGA III       10-8       PICAL       4-32       VSM2032       5-10         ER0082       3-5       PICES II       4-134       4-134       4-134                                                                                                                                                                                                                                                                                                                                                                                  |              |             |             |             | SBD000           | 5-9          |

| AY-5-9158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AT-0-9155A/D |             |             |             |                  |              |

| AY-5-9559                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |             |             |             |                  |              |

| CK3300       .7-18       PIC1650XT       .4-16         PIC1650XT       .4-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |             | PIC1650A    | 4-4, 9-9    |                  |              |

| CK3300       .7-18       PIC1654       .4-28       TELEVIEW SYSTEM       .9-4         CP1610       .9-22       PIC1655A       .4-38       TZ-2001       .6-30         CT2010       .10-27       PIC1666       .4-72       TZ-2002       .6-30         CT2017       10-29       PIC1665       .4-121       PIC1670       .5-10         ECONOMEGA III       .10-8       PICAL       .4-32       VSM2032       .5-10         ER0082       .3-5       PICES II       .4-134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /            |             | PIC1650XT   | 4-16        | 0                |              |

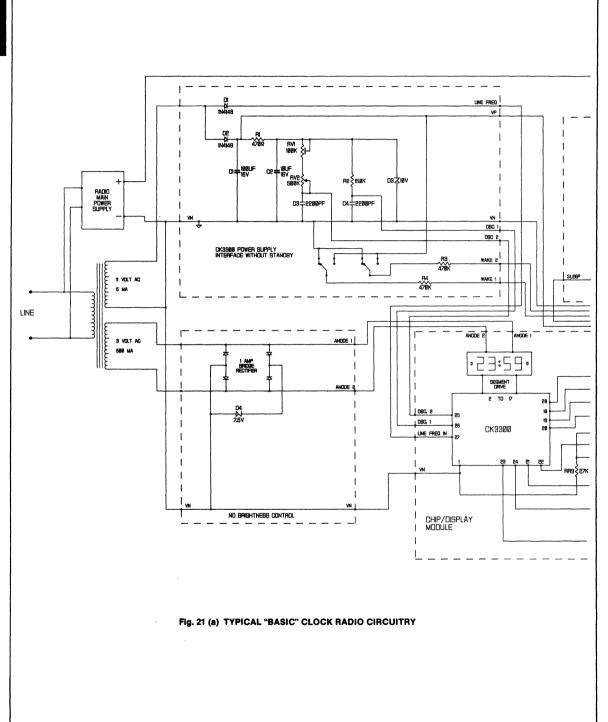

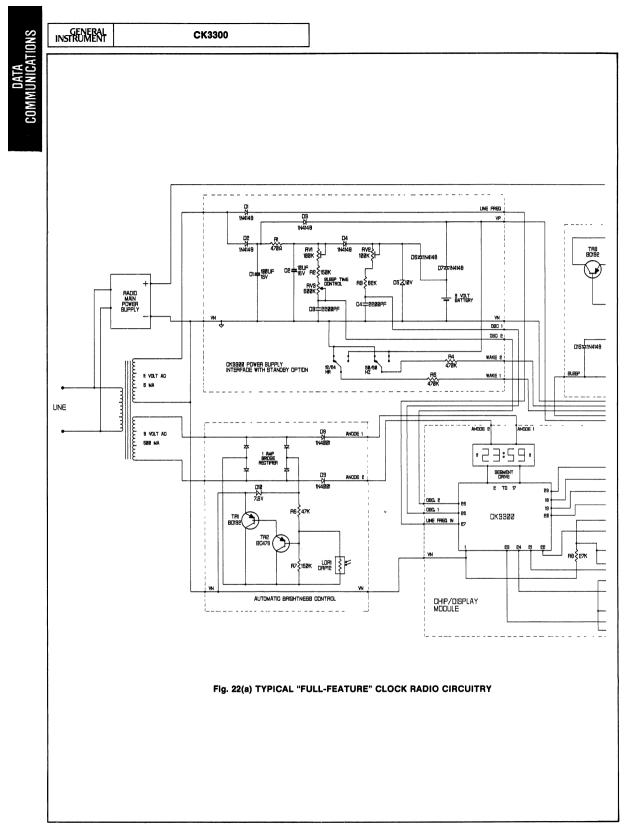

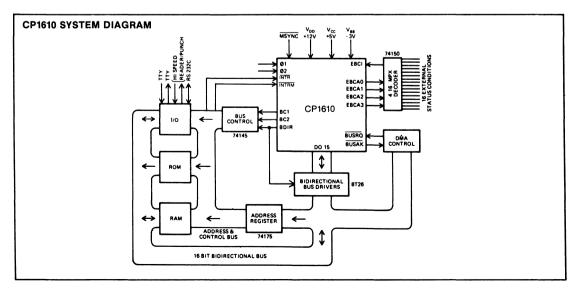

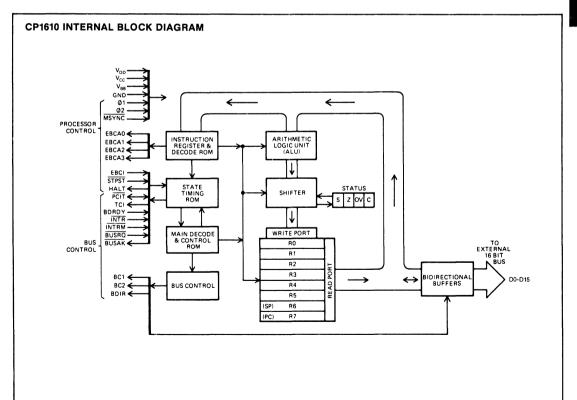

| CP1610                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | СК3300       | 7-18        |             |             | TELEVIEW SYSTE   | M <b>9-4</b> |

| CP1610                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |             |             |             |                  |              |

| CT2010       10-27       PIC1664       4-96       TZ-2003       6-30         CT2017       10-29       PIC1665       4-121       VSM2032       5-10         ECONOMEGA III       10-19       PICAL       4-32       VSM2032       5-10         ER0082       3-5       PICES II       4-134       10-10       10-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CP1610       |             | PIC1655XT   |             |                  |              |

| CT2017       10-29       PIC1665       4-121         PIC1670       4-85       VSM2032       5-10         ECONOMEGA III       10-19       PICAL       4-32         ER0082       3-5       PICES II       4-134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |             |             |             |                  |              |

| ECONOMEGA III10-8         PIC16704-85         VSM20325-10           ECONOMEGA IV10-19         PICAL4-32         VSM20325-10           ER00823-5         PICES II4-34         VSM20325-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |             |             |             | TZ-2003          | 6-30         |

| ECONOMEGA III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | СТ2017       | 10-29       |             |             |                  |              |

| ECONOMEGA IV 10-19         PICAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FOOLONEC     | 40-         | PIC1670     |             | VSM2032          | 5-10         |

| ER0082                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |             | DICAL       | 4 00        |                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ECONOMEGA IV |             |             |             |                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FB0082       | 3-5         | PICES II    | 4-134       |                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |             |             | ·····       |                  |              |

INDEX

## **ROM 2**

| FUNCTION                          | DESCRIPTION                                                                                                  | PART<br>NUMBER | PAGE<br>NUMBER |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|----------------|

|                                   |                                                                                                              | Read Only M    | lemories       |

|                                   |                                                                                                              | RO-3-9316A/B/C | 2-4            |

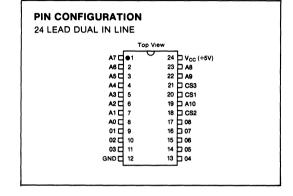

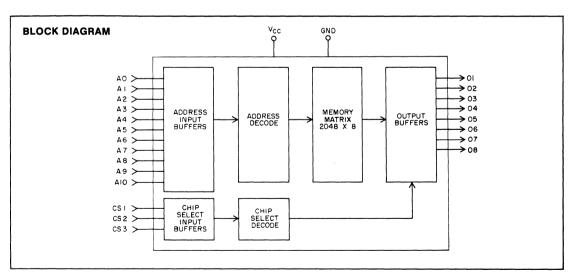

| 16K ROM                           | 16,384 bits organized 2048 x 8                                                                               | RO-3-9316HR    | 2-4            |

|                                   |                                                                                                              | RO-3-9332A/B/C | 2-7            |

|                                   |                                                                                                              | RO-3-9332HR    | 2-7            |

| 00% 0.014                         |                                                                                                              | RO-3-9333B/C   | 2-10           |

| 32K ROM                           | 32,768 bits organized 4096 x 8                                                                               | RO-3-9333HR    | 2-10           |

|                                   |                                                                                                              | R09432B/C/D    | 2-12           |

|                                   |                                                                                                              | R09433B/C/D    | 2-14           |

|                                   |                                                                                                              | RO-3-9364B/C   | 2-16           |

|                                   |                                                                                                              | RO-3-9364HR    | 2-16           |

|                                   |                                                                                                              | RO-3-9365B/C   | 2-19           |

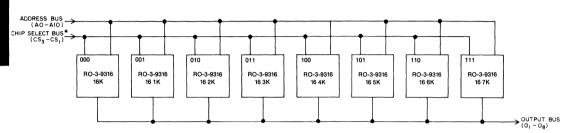

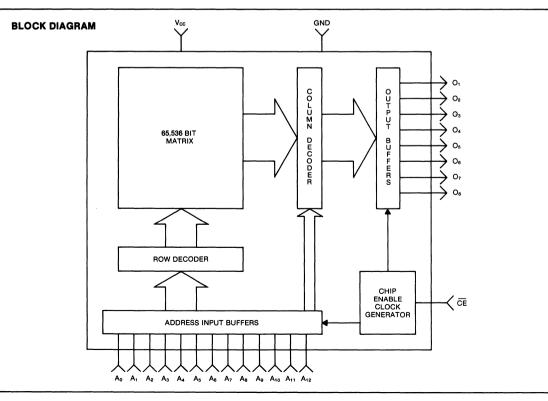

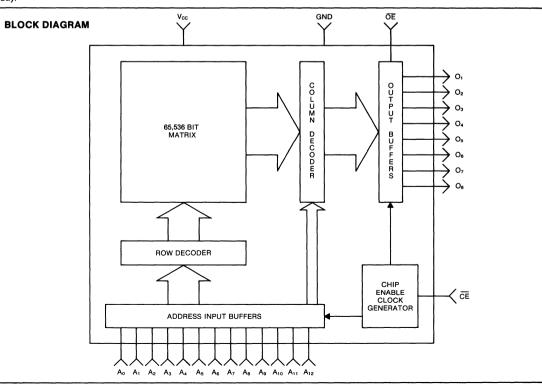

| 64K ROM                           | 65,536 bits organized 8192 x 8                                                                               | R09464B/C/D    | 2-22           |

|                                   |                                                                                                              | RO9464AB/AC/AD | 2-22           |

|                                   |                                                                                                              | RO9864B/C/D    | 2-25           |

|                                   | ·                                                                                                            | RO9864AB/AC/AD | 2-25           |

| 128K ROM                          | 131,072 bits organized 16,384 x 8                                                                            | RO9128B/C/D    | 2-28           |

| 256K ROM                          | 262,144 bits organized 32,768 x 8                                                                            | RO9256         | 2-31           |

| 20K CARTRIDGE<br>ROM              | 20,480 bits organized 2048 x 10                                                                              | RO-3-9504      | 2-32           |

| 40K CARTRIDGE<br>ROM              | 40,960 bits organized 4096 x 10                                                                              | RO9508         | 2-34           |

| 80K CARTRIDGE<br>ROM              | 81,920 bits organized 8192 x 10                                                                              | RO9580         | 2-37           |

| 160K CARTRIDGE<br>ROM             | 163,840 bits organized 16,384 x 10                                                                           | RO9160         | 2-39           |

|                                   |                                                                                                              | Keyboard       | Encoder        |

| CAPACITIVE<br>KEYBOARD<br>ENCODER | 4,592 bits organized as 112 keys x 4 modes x 10 bits, plus 112 bits for internal programing of function keys | AY-3-4592      | 2-42           |

|                                   |                                                                                                              | Character G    | enerators      |

| CHARACTER                         | 2,560 bits organized a 64-5 x 8 characters                                                                   | RO-3-2513      | 2-54           |

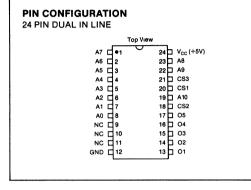

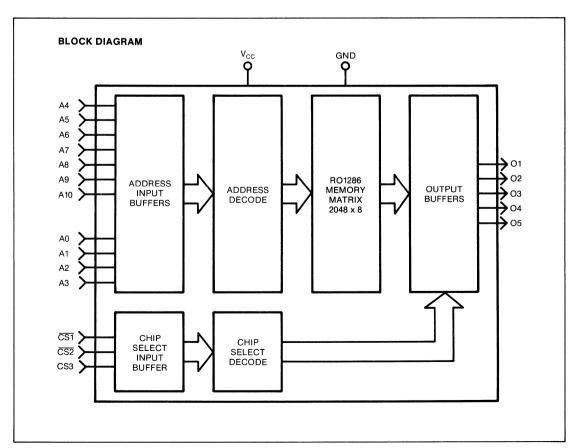

| GENERATOR                         | 16,384 bits organized as 2048-8 bit words                                                                    | RO-3-9316CGII  | 2-59           |

|                                   |                                                                                                              | Spee           | ch ROMs        |

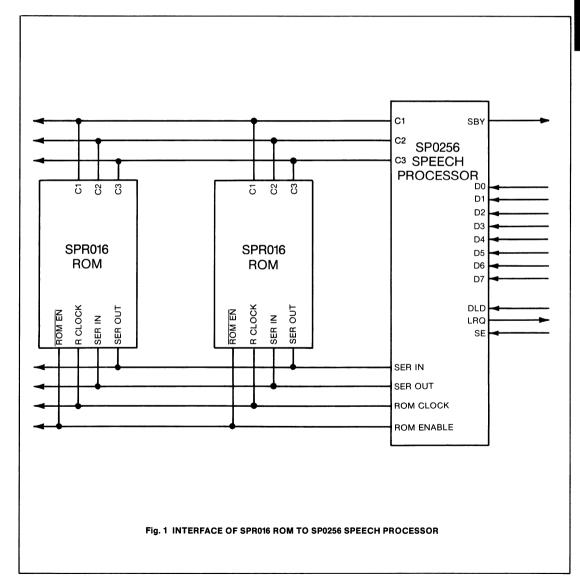

| SERIAL                            | 16,384 bits organized 2048 x 8                                                                               | SPR016         | 2-64           |

| SPEECH                            | 32,768 bits organized 4096 x 8                                                                               | SPR032         | 2-70           |

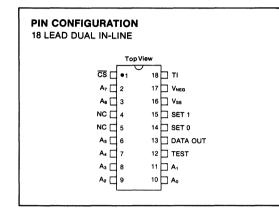

| ROM                               | 131,072 bits organized 16K x 8                                                                               | SPR128         | 2-73           |

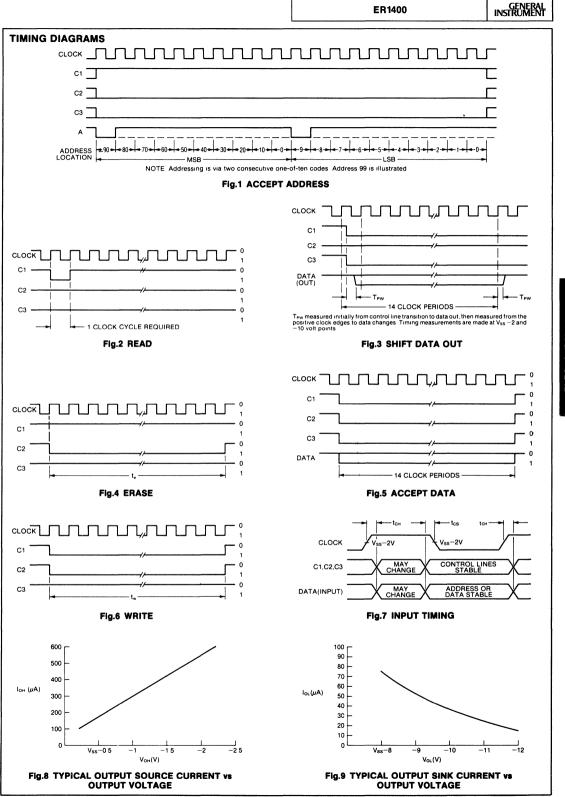

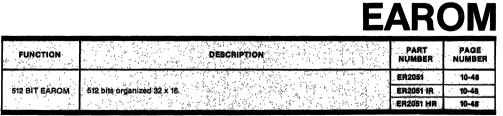

## EANVM 3

| FUNCTION                                   | DESCRIPTION                                                                        | PART        | PAGE     |  |  |

|--------------------------------------------|------------------------------------------------------------------------------------|-------------|----------|--|--|

|                                            |                                                                                    | NUMBER      | NUMBER   |  |  |

|                                            | Electrically Alterable Non-Volatile Memory                                         |             |          |  |  |

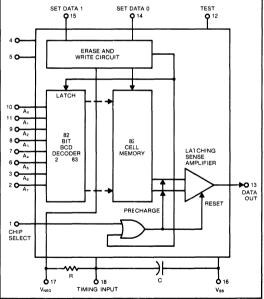

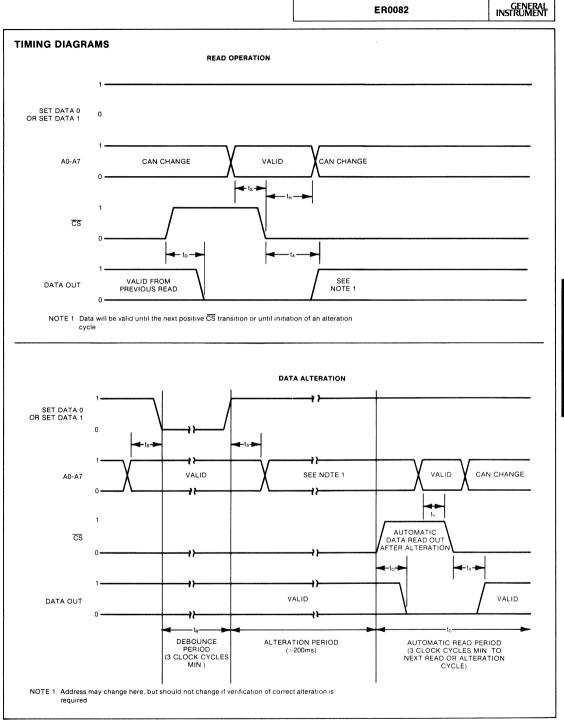

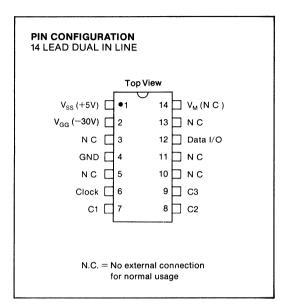

| 82 BIT EAROM                               | 82 bits organized 82 x 1                                                           | ER0082      | 3-5      |  |  |

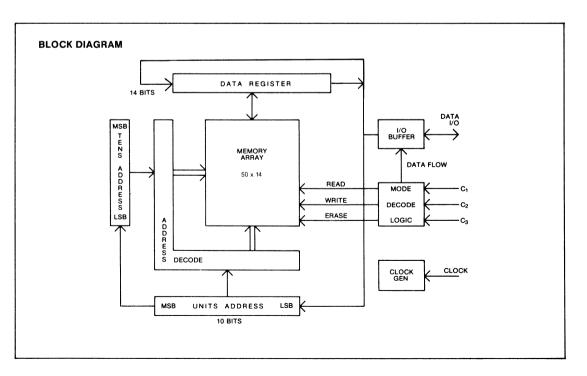

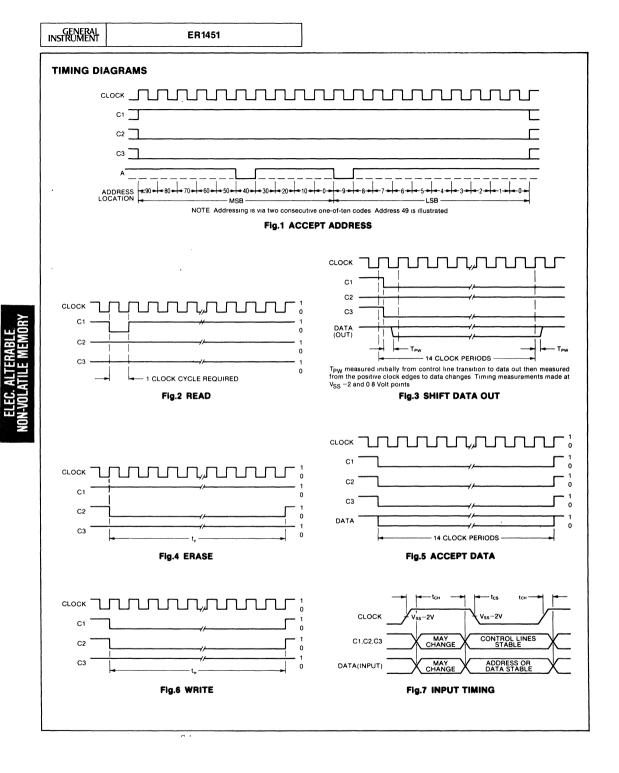

| 700 BIT<br>SERIAL EAROM                    | 700 bits organized 50 x 14                                                         | ER1451      | 3-8      |  |  |

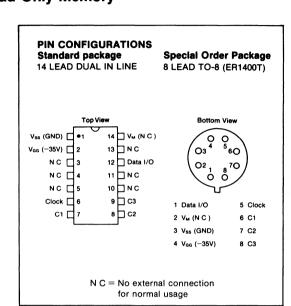

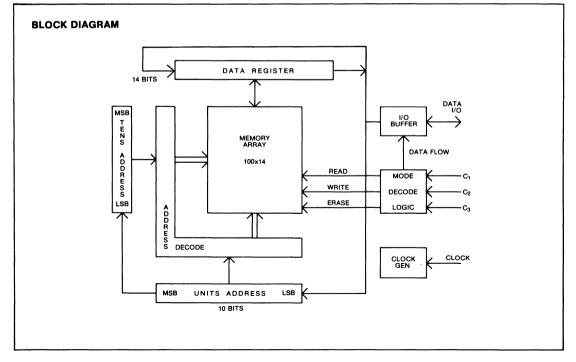

| 1400 BIT<br>SERIAL EAROM                   | 1400 bits organized 100 x 14                                                       | ER1400      | 3-11     |  |  |

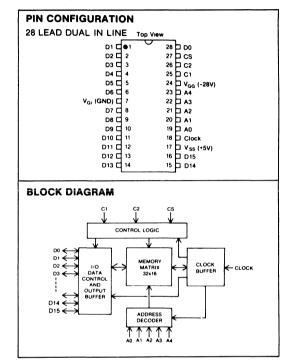

|                                            |                                                                                    | ER2051      | 3-14     |  |  |

| 512 BIT EAROM                              | 512 bits organized 32 x 16                                                         | ER2051IR    | 3-14     |  |  |

|                                            |                                                                                    | ER2051HR    | 3-14     |  |  |

|                                            |                                                                                    | ER2055      | 3-17     |  |  |

| 512 BIT EAROM                              | 512 bits organized 64 x 8                                                          | ER2055IR    | 3-17     |  |  |

|                                            |                                                                                    | ER2055HR    | 3-17     |  |  |

|                                            |                                                                                    | ER5901      | 3-20     |  |  |

| 1K N-CHANNEL<br>EEPROM                     | 1K bits organized 128 x 8                                                          | ER5901IR    | 3-20     |  |  |

| EEFROM                                     |                                                                                    | ER5901HR    | 3-20     |  |  |

|                                            | 4096 bits organized 1024 x 4                                                       | ER3400      | 3-22     |  |  |

| 4096 BIT EAROM                             |                                                                                    | ER3400I/IR  | 3-22     |  |  |

|                                            |                                                                                    | ER3400HR    | 3-22     |  |  |

|                                            |                                                                                    | ER2810IR    | 3-28     |  |  |

| 8192 BIT EAROM                             | 8192 bits organized 2048 x 4                                                       | ER2810HR    | 3-28     |  |  |

|                                            |                                                                                    | ER5716      | 3-32     |  |  |

| 16K N-CHANNEL<br>EEPBOM                    | 16K bits organized 2048 x 8                                                        | ER5716IR    | 3-32     |  |  |

| EEPROM                                     |                                                                                    | ER5716HR    | 3-32     |  |  |

|                                            |                                                                                    | ER5816      | 3-36     |  |  |

| WORD ALTERABLE<br>16K BIT EEPROM           | Electrically word alterable 16K bits organized 2048 x 8, 5V operation in read mode | ER5816IR    | 3-36     |  |  |

| ION BIT EEFHOM                             |                                                                                    | ER5816HR    | 3-36     |  |  |

|                                            |                                                                                    | ER5916      | 3-41     |  |  |

| WORD ALTERABLE<br>16K BIT EEPROM           | Electrically word alterable 16K bits organized 2048 x 8, 5V operation in all modes | ER5916IR    | 3-41     |  |  |

|                                            |                                                                                    | ER5916HR    | 3-41     |  |  |

|                                            | Non-                                                                               | Volatile St | atic RAM |  |  |

| 4K N-CHANNEL<br>NON-VOLATILE<br>STATIC RAM | 4K bits organized 512 x 8                                                          | ER5304      | 3-48     |  |  |

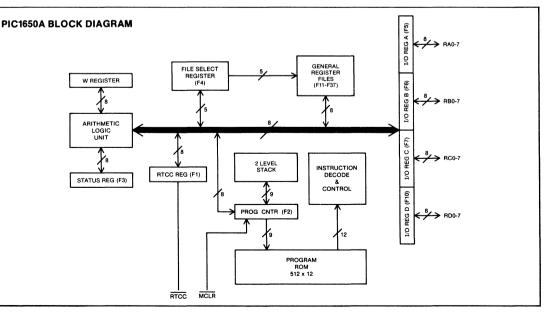

## **Microcomputer 4**

| FUNCTION                  | DESCRIPTION                                                                                                                                                           | PART<br>NUMBER | PAGE<br>NUMBER |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

|                           |                                                                                                                                                                       | Р              | IC Series      |

|                           |                                                                                                                                                                       | PIC1650A       | 4-4            |

|                           |                                                                                                                                                                       | PIC1650XT      | 4-16           |

| 1                         |                                                                                                                                                                       | PIC1654        | 4-28           |

| 8 BIT                     | The PIC1650 series of microcomputers contain RAM I/O and a central processing<br>unit as well as a customer defined ROM to specify overall functional characteristics | PIC1655A       | 4-38           |

| MICROCOMPUTER             | of the device                                                                                                                                                         | PIC1655XT      | 4-50           |

|                           |                                                                                                                                                                       | PIC16C55       | 4-62           |