#

Small Computer Systems Interface

MB87030 Synchronous/Asynchronous Protocol Controller

**Users Manual**

Fujitsu Limited Fujitsu Microelectronics, Inc. Fujitsu Mikroelektronik GmbH

# Small Computer Systems Interface

# **MB87030**

Synchronous/Asynchronous Protocol Controller

**Users Manual**

Copyright © 1986 by Fujitsu Limited and Fujitsu Microelectronics, Inc.

This Publication contains information considered proprietary by Fujitsu Limited, Tokyo, Japan and Fujitsu Microelectronics, Inc. No part of this document may be copied or reproduced in any form or by any means or transferred to any third party without the prior written consent of Fujitsu Limited.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical applications; consequently complete information sufficient for construction purposes is not necessarily given. The information in this publication has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for any inaccuracies.

The information conveyed in this publication does not convey any license under the patent rights of Fujitsu Limited.

Fujitsu reserves the right to change specifications without notice.

MB87030 Synchronous/Asychronous Protocol Controller User's Manual is published by the U.S. Technical Publications Department, Fujitsu Microelectronics, 3320 Scott Blvd., Santa Clara, CA 95054-3197, (408) 727-1700 ext. 2414.

Printed in the U.S.A.

Edition 1.0 (Phase 1)

May, 1986

ii

## **Fujitsu Limited**

Furukawa Sogo Bldg., 6–1 Marunouchi 2–Chome, Chiyoda–ku Tokyo 100, Japan Phone National (03) 216–3211 Phone International 81–3–216–3211 Telex: 2224361 FT TOR J

.

## Fujitsu Microelectronics, Inc.

3320 Scott Blvd. Santa Clara, CA 95054-3197 Phone: (408) 727-1700 Telex: (910) 338-0190

## Fujitsu Mikroelektronik GmbH

Arabella Center 9, OG/A Lyoner Straβe 44-48 D-6000 Frankfurt 71, F.R. Germany Phone 069/66 320 Telex 0411 963

iii

\_\_\_\_\_

•

#### PREFACE

The Fujitsu MB87030 (SPC: SCSI Protocol Controller) is a CMOS LSI circuit developed to control the small computer system interface (SCSI).

This manual explains the functions and use of the MB87030.

It consists of the following chapters:

CHAPTER 1 OUTLINE CHAPTER 2 INPUT/OUTPUT TERMINALS CHAPTER 3 FUNCTIONS CHAPTER 4 OPERATIONAL DESCRIPTION CHAPTER 5 EXAMPLES OF EXTERNAL CIRCUIT CONNECTIONS CHAPTER 6 AC CHARACTERISTICS

To effectively apply this LSI circuit's functions, you must be familiar with SCSI functions and interface control procedures.

Note: Fujitsu reserves the right to change functions or characteristics to improve the design of the LSI circuit without prior notice.

## CONTENTS

| CHAPTER 1 OUTLINE                                  | 1          |

|----------------------------------------------------|------------|

|                                                    | -          |

| 1.1 GENERAL DESCRIPTION                            | 1          |

| 1.2 FEATURES                                       | 1          |

| 1.3 ELECTRICAL CHARACTERISTICS                     | ī          |

|                                                    |            |

| 1.3.1 Absolute Maximum Ratings                     | 1          |

| 1.3.2 Recommended Operating Conditions             | 2          |

|                                                    |            |

| 1.3.3 DC Characteristics                           | 2          |

| 1.3.4 Input/output Capacitance                     | 2          |

| 1.4 PHYSICAL DIMENSIONS                            | 3          |

| 1.7 HINGTONE DIMENSIONS ITTERSTORY                 | -          |

|                                                    |            |

| CHAPTER 2 INPUT/OUTPUT TERMINALS                   | 4          |

| 2.1 PIN ASSIGNMENTS                                | 4          |

|                                                    |            |

| 2.2 INPUT/OUTPUT SIGNALS                           | 4          |

|                                                    |            |

| CHAPTER 3 FUNCTIONS                                | 10         |

|                                                    |            |

| 3.1 FUNCTIONAL BLOCKS                              | 10         |

| 3.2 INTERNAL REGISTER                              | 11         |

| 3.2.1 Addressing                                   | 11         |

|                                                    |            |

| 3.2.2 Internal Register Assignments                | 11         |

| 3.3 MAJOR OPERATIONS                               | 14         |

| 3.3.1 MPU Interface Control Block                  | 14         |

|                                                    |            |

| 3.3.2 Bus Phase Control Block                      | 14         |

| 3.3.3 Arbitration/Selection Sequence Control Block | 14         |

| 3.3.4 Transfer Sequence Control Block              | 14         |

|                                                    |            |

| 3.3.5 Transfer Byte Counter Block                  | 15         |

| 3.3.6 Data Buffer Register Block                   | 15         |

|                                                    |            |

|                                                    | 10         |

| CHAPTER 4 OPERATIONAL DESCRIPTION                  | 16         |

| 4.1 BDID REGISTER                                  | 16         |

| 4.2 SCTL REGISTER                                  | 16         |

|                                                    |            |

| 4.3 SCMD REGISTER                                  | 18         |

| 4.3.1 Register Functions                           | 18         |

| 4.3.2 Command Functions                            | 21         |

|                                                    |            |

| 4.3.3 Command Termination Report                   | 30         |

| 4.3.4 Command Issuance Timing                      | 30         |

| 4.4 TMOD REGISTER                                  | 31         |

|                                                    |            |

| 4.4.1 Register Functions                           | 31         |

| 4.4.2 Transfer Mode Setting Timing                 | 32         |

| 4.5 PCTL REGISTER                                  | 33         |

| 4.6 DATA BUFFER REGISTER (DREG)                    | 34         |

| 4.0 DATA BOFFER REGISTER (DREG)                    |            |

| 4.7 TEMP REGISTER                                  | 35         |

| 4.8 TRANSFER BYTE COUNTER (TCH, TCM, TCL)          | 36         |

| 4.9 PSNS REGISTER                                  | 36         |

|                                                    |            |

| 4.10 SSTS REGISTER                                 | 37         |

| 4.10.1 Register Functions                          | 37         |

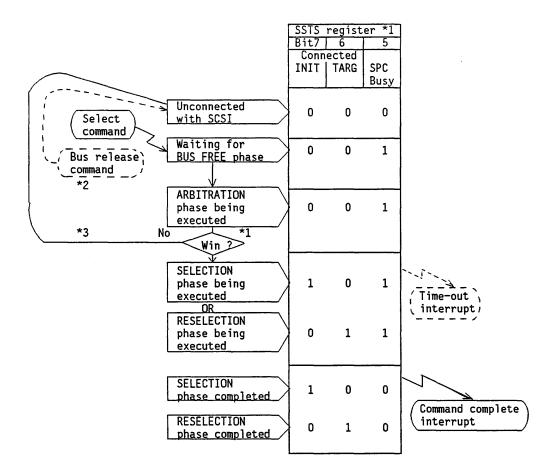

| 4.10.2 SPČ Status                                  | 38         |

|                                                    |            |

| 4.11 INTS REGISTER                                 | 39         |

| 4.11.1 Register Functions                          | 39         |

| 4.11.2 Interrupt Processing                        | 39         |

| 4.12 SERR REGISTER                                 | 47         |

|                                                    |            |

| 4.12.1 Register Functions                          | 47         |

| 4.12.2 Error Reset                                 | 49         |

| 4.13 MBC REGISTER                                  | 49         |

| A 14 EVERNA DIFER DECORTER (EVER)                  |            |

| 4.14 EXTERMA: BIFFER REGOSTER (EXBF)               | 50         |

| 4.15 SDGC REGISTER                                 | 50         |

| 4.16 INITIALIZATION                                | 51         |

| ······································             | <b>~ -</b> |

## Page

- i -

## CONTENTS (Cont'd)

| $5.1.1 \\ 5.1.2$                                                                                                                                       | EXAMPLES OF EXTERNAL CIRCUIT CONNECTIONS<br>SI DRIVER/RECEIVER CIRCUITS<br>Single Ended Type<br>Differential Type<br>TERNAL DATA BUFFER | 53<br>54<br>54<br>57<br>60                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

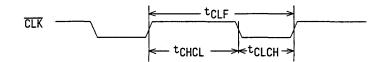

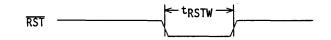

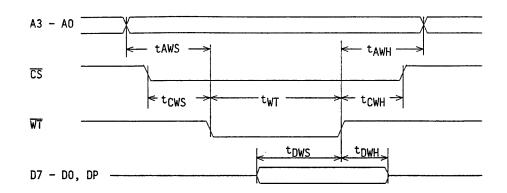

| CHAPTER 6<br>6.1 MPU<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.2 DMA<br>6.2.1<br>6.2.2<br>6.2.3<br>6.3 SCS<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4 | Clock Signal<br>Reset Signal<br>Write Cycle<br>Read Cycle<br>Interrupt                                                                  | 62<br>63<br>63<br>65<br>67<br>67<br>67<br>68<br>69<br>70<br>70<br>78<br>82<br>97 |

| 6.3.5<br>6.3.6                                                                                                                                         | BUS FREE                                                                                                                                | 98<br>101                                                                        |

## Page

## ILLUSTRATIONS AND TABLES

ILLUSTRATIONS

|      | 1.4.1<br>2.1.1 | Dimensions of package<br>Pin assignments                  | 3<br>5 |

|------|----------------|-----------------------------------------------------------|--------|

|      | 3.1.1          | SPC functional block diagram                              | 10     |

| Fig. | 4.3.1          | Status transitions in Select command execution            | 24     |

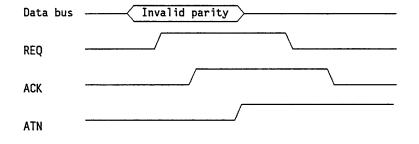

| Fig. | 4.3.2          | ATN signal generation in data transfer                    | 25     |

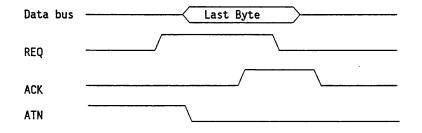

|      | 4.3.3          | ATN signal resetting in MESSAGE OUT phase                 | 25     |

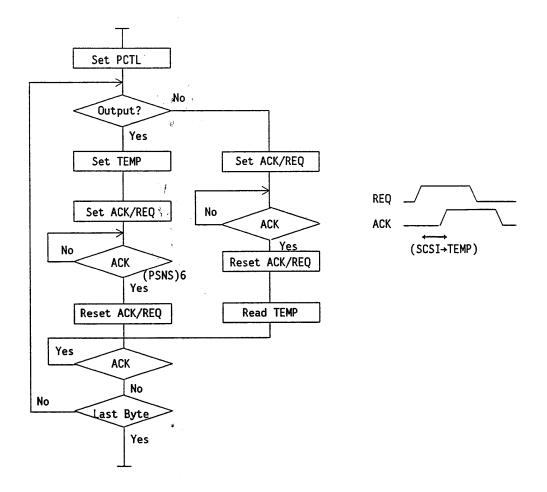

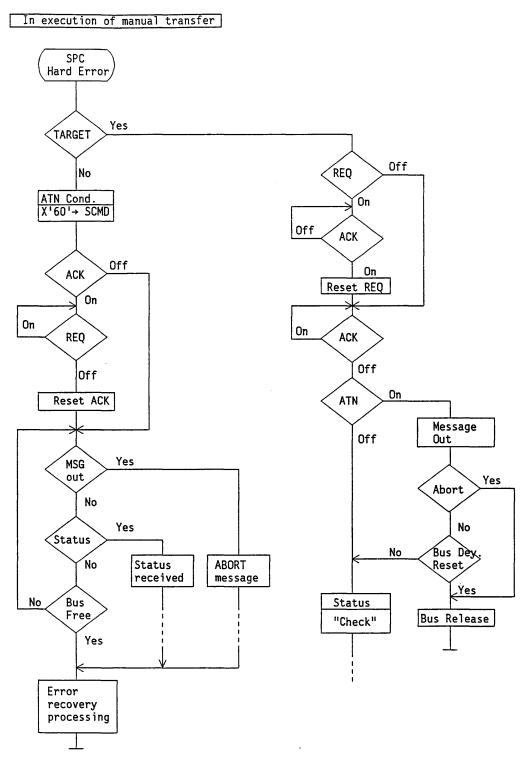

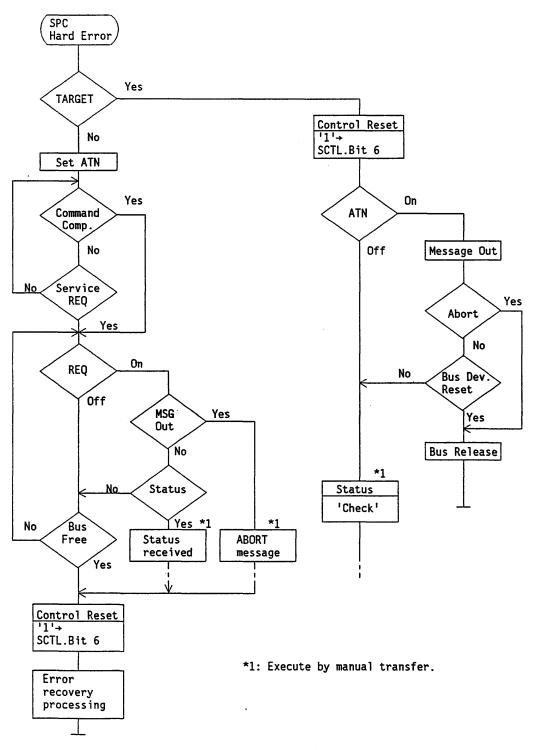

| Fig. | 4.3.4          | Manual transfer procedure (SPC serving as a TARGET)       | 28     |

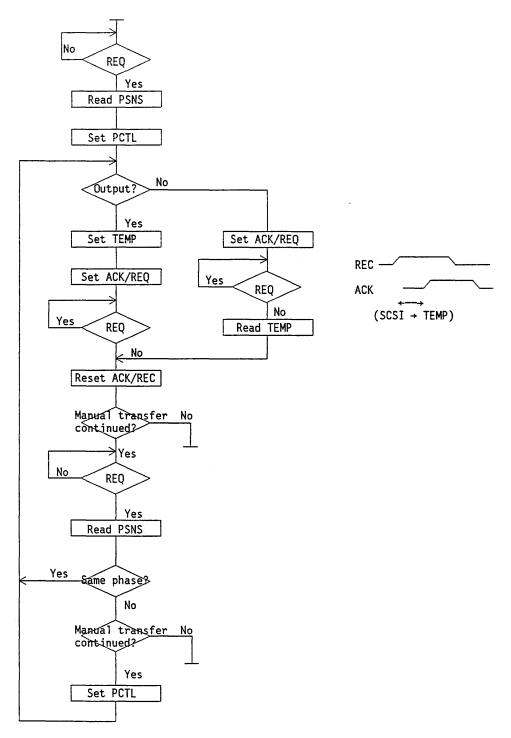

| Fig. | 4.3.5          | Manual transfer procedure (SPC serving as an INITIATOR)   | 29     |

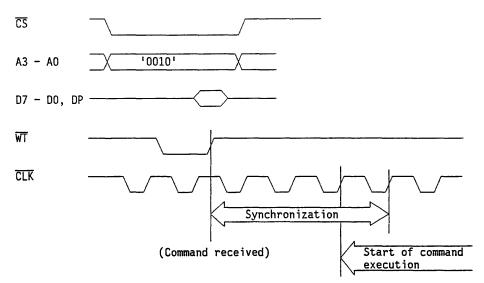

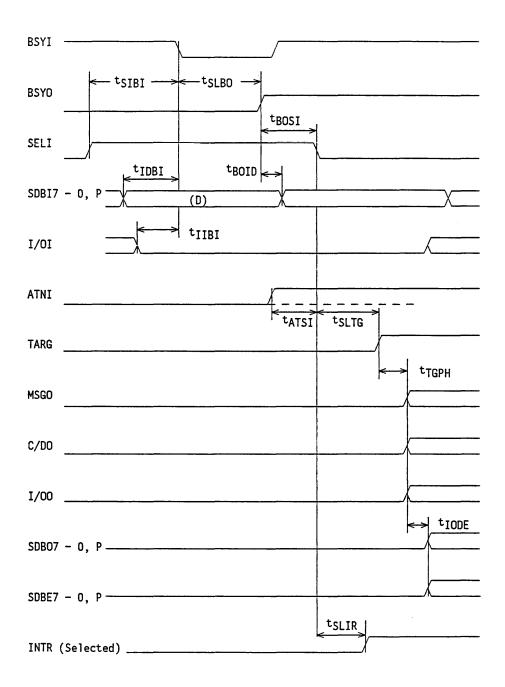

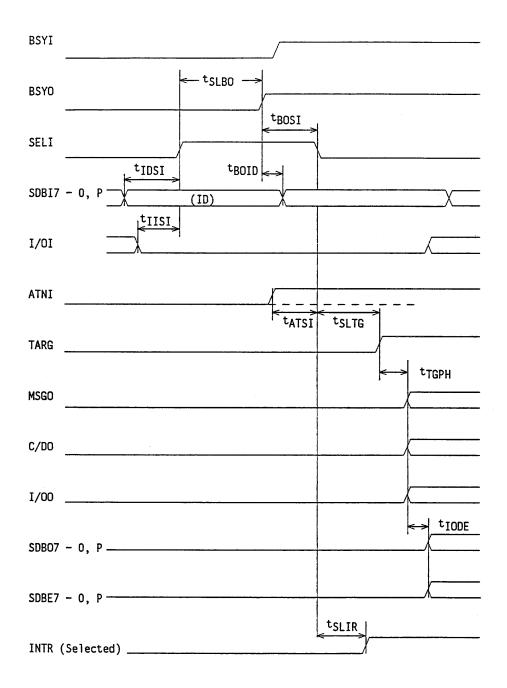

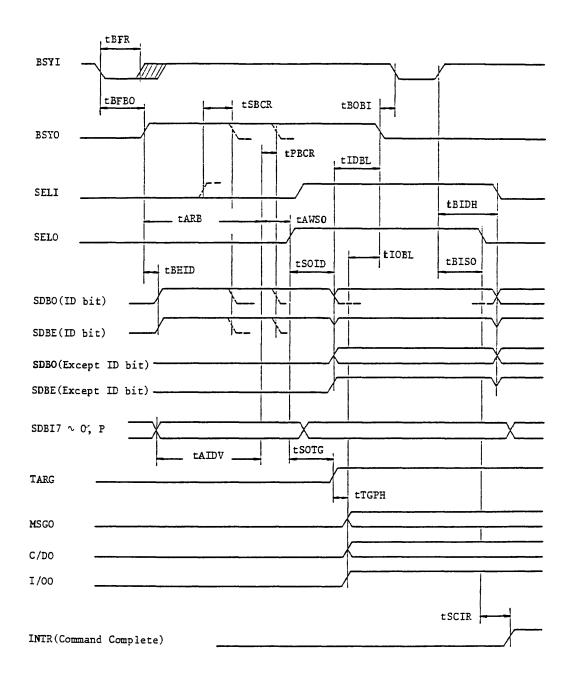

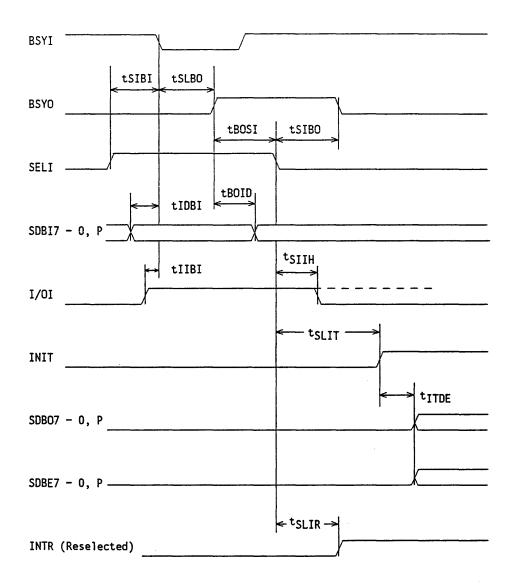

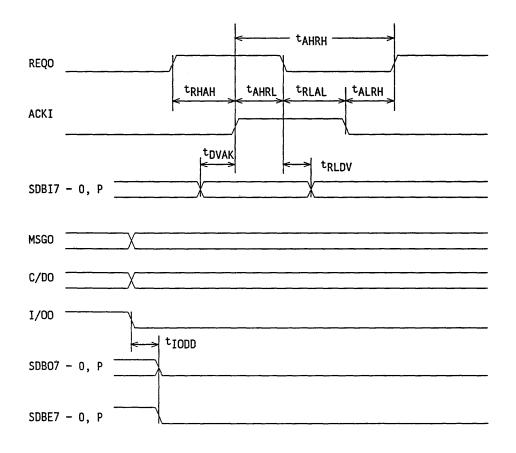

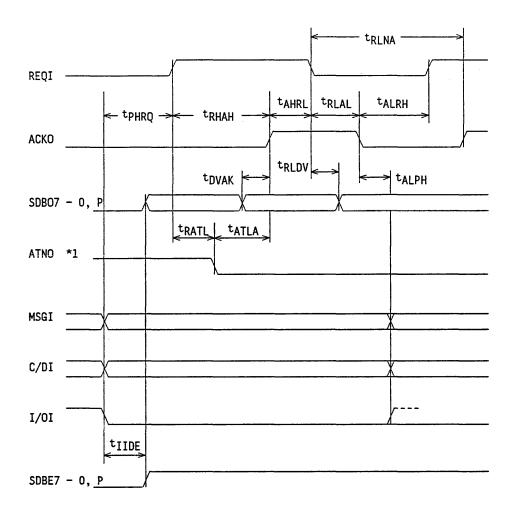

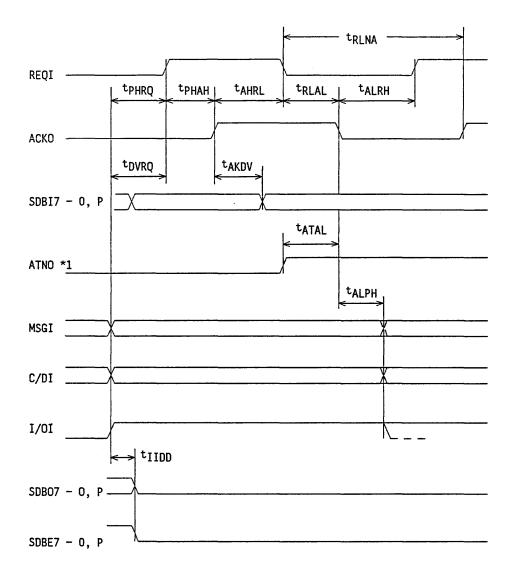

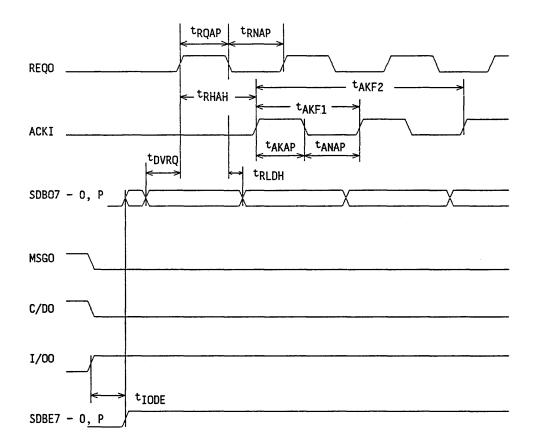

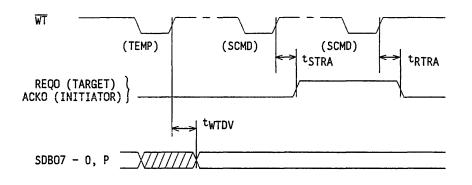

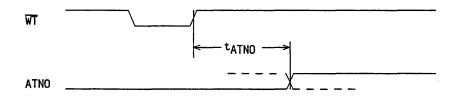

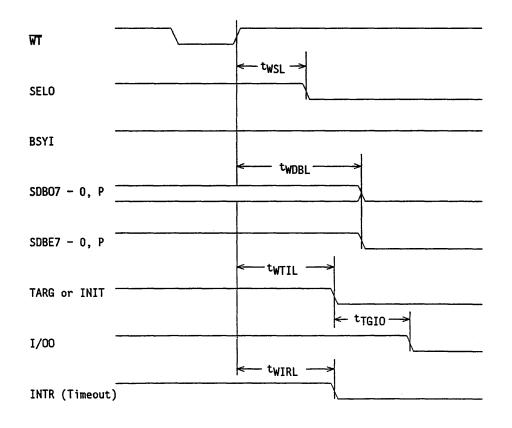

| Fig. | 4.3.6          | Command execution timing                                  | 31     |

| Fig. | 4.4.1          | Transfer period setting                                   | 32     |

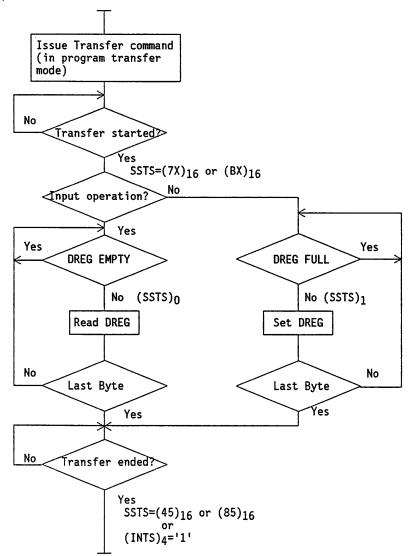

| Fig. | 4.6.1          | DREG access procedure in program transfer mode            | 34     |

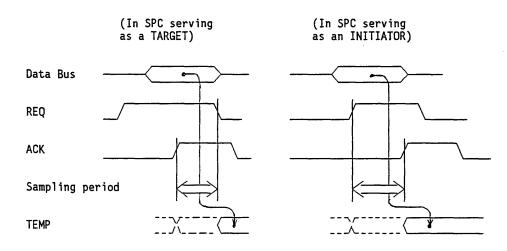

| Fig. | 4.7.1          | Data bus save in manual transfer input operation          | 35     |

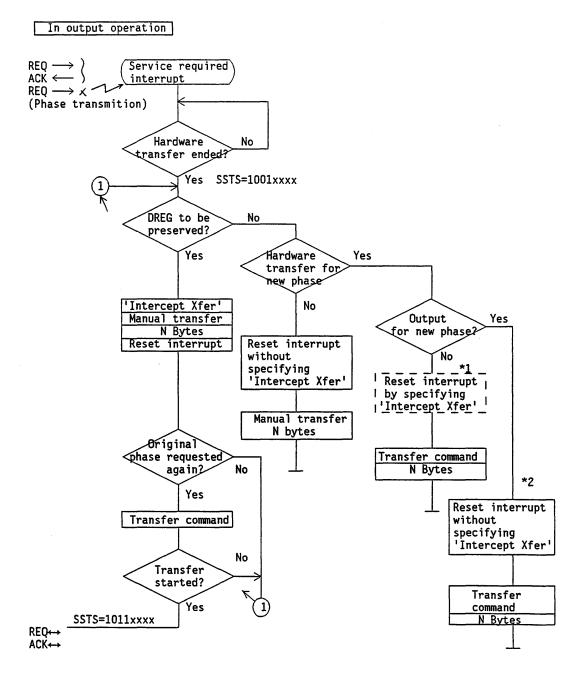

| Fig. | 4.11.1         | Service required interrupt processing procedure (1)       | 42     |

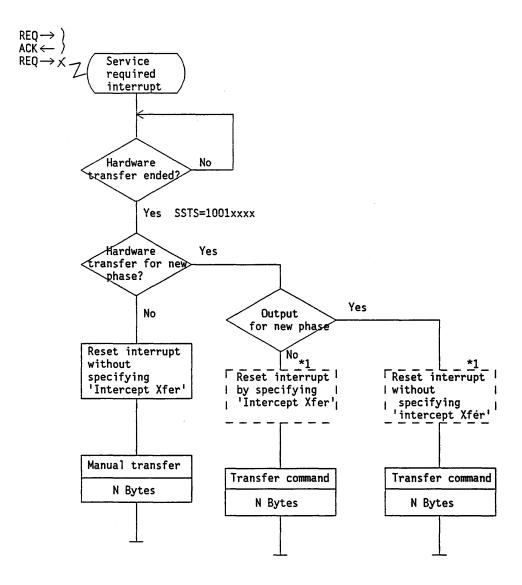

| Fig. | 4.11.2         | Service required interrupt processing procedure (2)       | 43     |

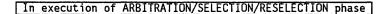

| Fig. | 4.11.3         | Example of control processing for SPC-detected error (1)  | 44     |

| Fig. | 4.11.4         | Example of control processing for SPC-detected error (2)  | 45     |

| Fig. | 4.11.5         | Example of control processing for SPC-detected error (3)  | 46     |

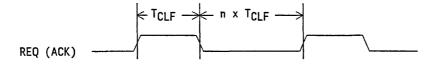

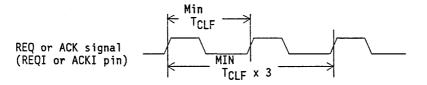

| Fig. | 4.12.1         | Specified input cycle of REQ/ACK signal                   | 48     |

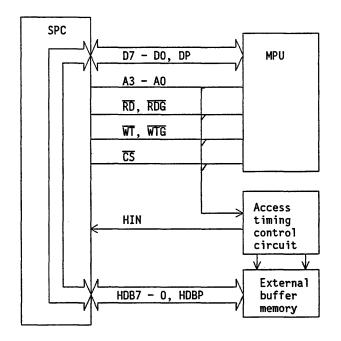

| Fig. | 4.14.1         | Access from MPU to external buffer memory                 | 50     |

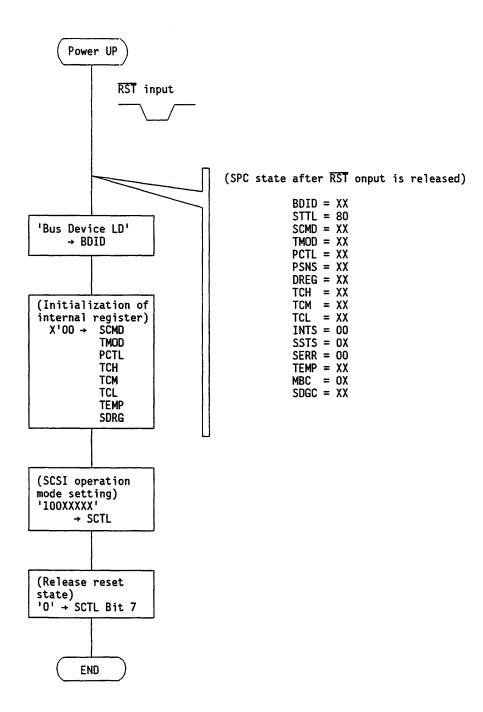

| Fig. | 4.16.1         | SPC initialization (at power-on)                          | 52     |

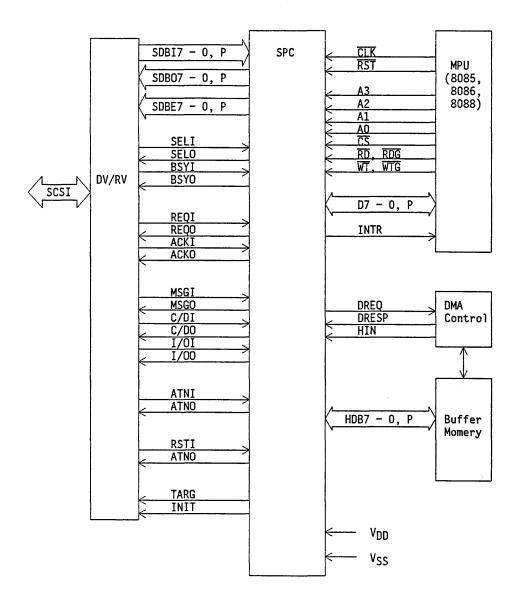

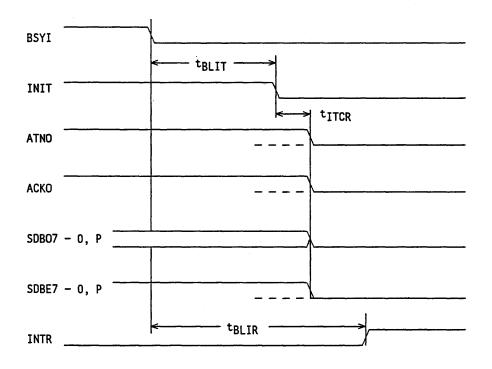

| Fig. | 5.1.1          | Examples of external circuit connections                  | 53     |

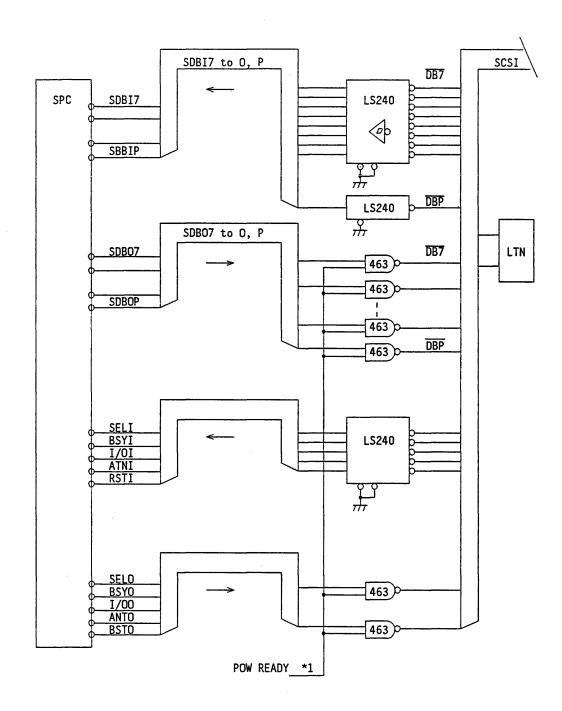

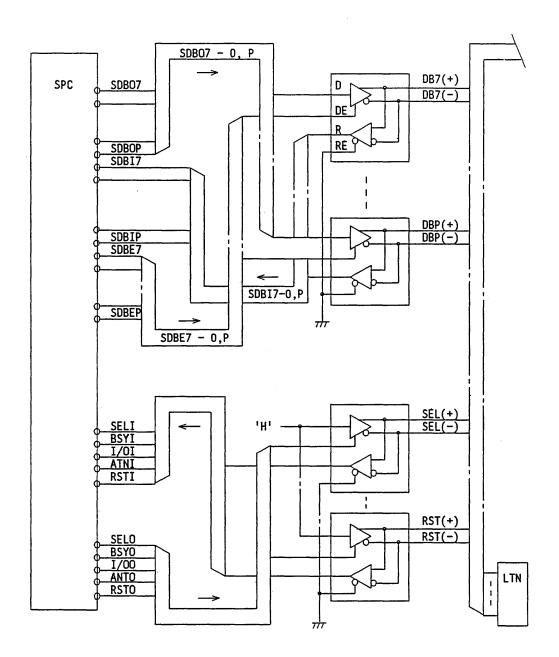

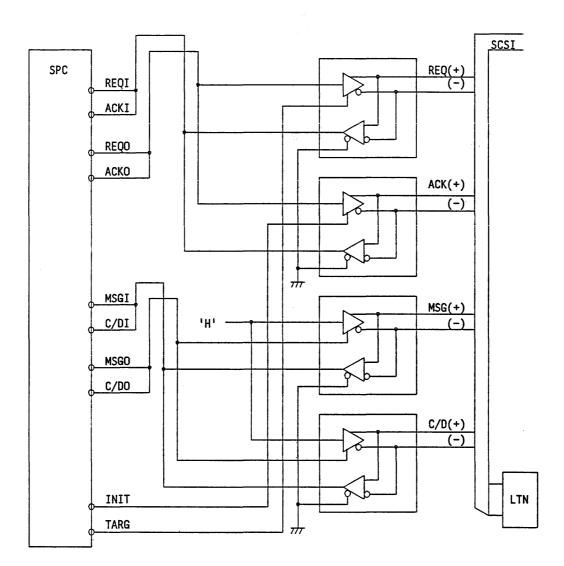

| Fig. | 5.1.2          | Example of single ended type SCSI driver/receiver circuit | 55     |

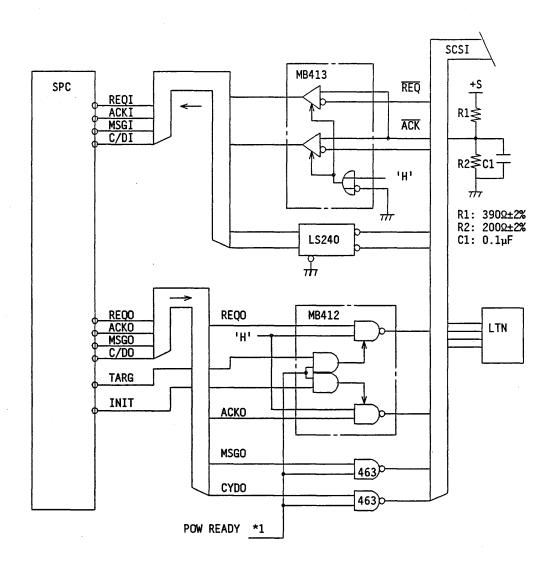

| Fig. | 5.1.3          | Example of differential type SCSI driver/receiver circuit | 58     |

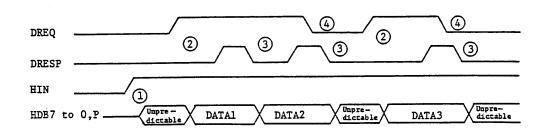

| Fig. | 5.2.1          | Transfer with external data buffer (input operation)      | 60     |

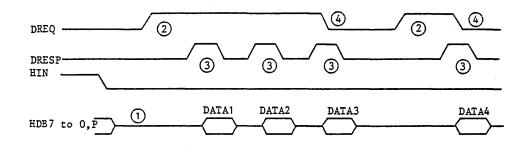

| Fig. | 5.2.2          | Transfer to external data buffer (output operation)       | 61     |

|      |                |                                                           |        |

## TABLES

## Page

| 11<br>12 |

|----------|

| 12       |

|          |

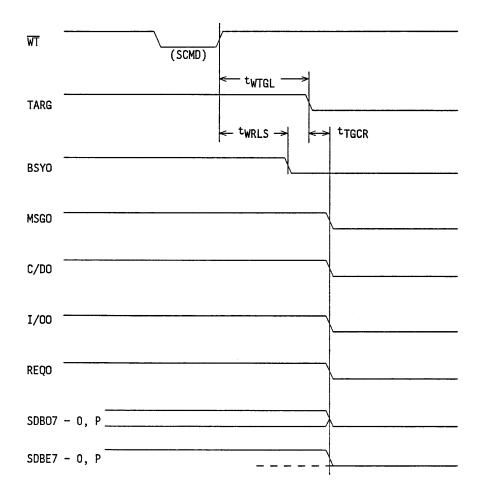

|          |

| 22       |

| 33       |

| 38       |

| 48       |

|          |

| 54       |

|          |

| 57       |

|          |

- iii -

CHAPTER 1

OUTLINE

#### 1.1 GENERAL DESCRIPTION

The MB87030 (SPC: SCSI Protocol Controller) is a CMOS LSI circuit designed to make control of the small computer system interface (SCSI) easier. The MB87030, which can control all the SCSI interface signals and handle almost all the interface control procedures, can be used as a peripheral LSI circuit for an 8- or 16-bit MPU to realize high-level SCSI control. This LSI circuit has an 8-byte FIFO data buffer register and a transfer byte counter that is 24 bits long. Its wide range of applications allows not only asynchronous mode transfer but also synchronous mode transfer with an offset of 8 bytes at maximum. Furthermore, MB87030 can serve as either an INITIATOR or a TARGET device for the SCSI, and can therefore be used for either an I/O controller or a host adapter. (Note: In this manual, MB87030 is referred to as SPC)

## **1.2 FEATURES**

- Full support for SCSI control

- Serves as either INITIATOR or TARGET device

- Synchronous mode transfer with a programmable offset, up to eight bytes

- Data transfer speed programmable at four rates (in synchronous mode transfer)

- Data transfer up to 4 MBPS allowed

- Eight-byte data buffer register incorporated

- Transfer byte counter, 24 bits long, incorporated

- Independent data transfer bus

- Applicable to the single-ended alternative and the differential alternative for SCSI

- Single +5 V supply

- Low power dissipation

- TTL-compatible inputs/outputs

- PGA 88-pin ceramic package

#### **1.3 ELECTRICAL CHARACTERISTICS**

1.3.1 Absolute Maximum Ratings\*

| Rating                           | Symbol <sup>1</sup> | Min.                    | Max.                  | Unit |

|----------------------------------|---------------------|-------------------------|-----------------------|------|

| Supply Voltage                   | V <sub>DD</sub>     | V <sub>SS</sub> **- 0.5 | 7.0                   | v    |

| Input Voltage                    | ٧I                  | V <sub>SS</sub> **- 0.5 | V <sub>DD</sub> + 0.5 | v    |

| Output Voltage                   | v <sub>o</sub>      | V <sub>SS</sub> **- 0.5 | V <sub>DD</sub> + 0.5 | v    |

| Storage Temperature (Ceramic)    | T <sub>stg</sub>    | -65                     | +150                  | °C   |

| Temperature Under Bias (Ceramic) | T <sub>bias</sub>   | -40                     | +125                  | °C   |

| Output Current***                | I <sub>OS</sub>     | -40                     | +70                   | mA   |

\* Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of the data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*\* V<sub>SS</sub> = 0 V

\*\*\* Not more than one output may be shorted at a time for a maximum duration of one second.

## 1.3.2 Recommended Operating Conditions

| Parameter             | Symbol          | Min. | Typ. | Max. | Unit |

|-----------------------|-----------------|------|------|------|------|

| Supply Voltage        | V <sub>DD</sub> | 4.75 | 5.0  | 5.25 | v    |

| Input High Voltage    | VIH             | 2.2  |      |      | v    |

| Input Low Voltage     | VIL             |      |      | 0.8  | v    |

| Operating Temperature | TA              | 0    |      | 70   | °C   |

1.3.3 DC Characteristics (Recommended Operating Conditions unless otherwise noted)

| Parameter             | Symbol           | Condition                                      | Min.            | Typ. | Max.            | Unit |

|-----------------------|------------------|------------------------------------------------|-----------------|------|-----------------|------|

| Power Supply Current  | I <sub>DDS</sub> | *<br>Steady state                              |                 |      | 100             | μΑ   |

| Power Dissipation     | Рр               |                                                |                 | 300  |                 | mW   |

| Output High Voltage   | V <sub>OH</sub>  | $I_{OH} = -0.4 mA$                             | 4.2             |      | V <sub>DD</sub> | v    |

| Output Low Voltage    | V <sub>OL</sub>  | I <sub>OL</sub> = 3.2mA                        | V <sub>SS</sub> |      | 0.4             | v    |

| Input High Voltage    | VIH              |                                                | 2.2             |      |                 | v    |

| Input Low Voltage     | VIL              |                                                |                 |      | 0.8             | v    |

| Input Leakage Current | I <sub>LI</sub>  | v <sub>I</sub> =o - v <sub>DD</sub>            | -10             |      | 10              | μA   |

| Input Leakage Current | ILZ              | 3-state<br>V <sub>I</sub> =0 - V <sub>DD</sub> | -10             |      | 10              | μA   |

\* Note:  $V_{IH} = V_{DD}$  ,  $V_{IL} = V_{SS}$

## 1.3.4 Capacitance

$$(T_A = 25 \text{ °C}, V_{DD} = V_I = 0 \text{ V}, f = 1 \text{ MHz})$$

| Parameter              | Symbol           | Min. | Typ. | Max. | Unit |

|------------------------|------------------|------|------|------|------|

| Input Pin Capacitance  | C <sub>IN</sub>  |      |      | 9    | pF   |

| Output Pin Capacitance | C <sub>OUT</sub> |      |      | 9    | pF   |

| I/O Pin Capacitance    | C <sub>I/0</sub> |      |      | 11   | pF   |

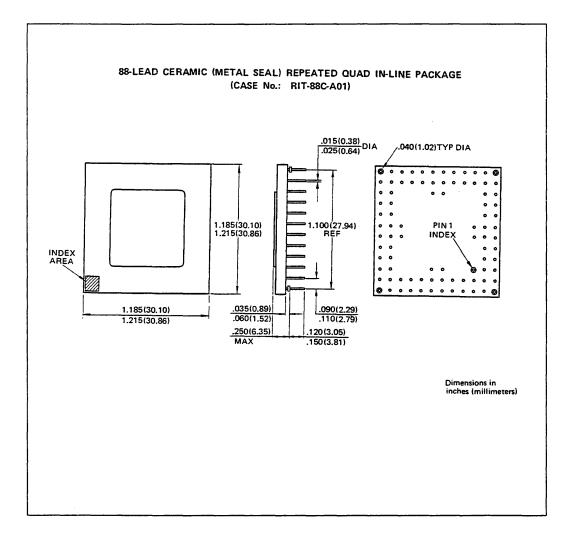

## 1.4 PHYSICAL DIMENSIONS

The MB87030 is packaged in an 88-pin ceramic package. Figure 1.4.1 shows the dimensions of the package.

Figure 1.4.1 Dimensions of Package

CHAPTER 2

INPUT/OUTPUT TERMINALS

2.1 PIN ASSIGNMENTS

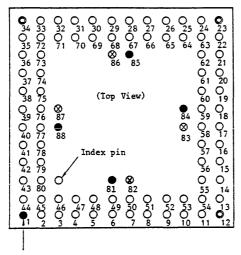

Figure 2.1.1 shows the arrangement of pins on this LSI.

## 2.2 INPUT/OUTPUT SIGNALS

Table 2.1.1 lists the input/output signals and their functions. In this table, the plus and minus signs have the following meaning: +: Indicates an active-high signal. -: Indicates an active-low signal.

Orientation Mark

| No. | 1/0 | Signal<br>name | No. | 1/0 | Signal<br>name | No. | 1/0 | Signal<br>name | No. | 1/0          | Signal<br>name |

|-----|-----|----------------|-----|-----|----------------|-----|-----|----------------|-----|--------------|----------------|

| 1   | I   | HIN            | 23  | 0   | SDBOP          | 45  | I   | A1             | 67  | · 0          | SDBE5          |

| 2   | I/0 | HDBO           | 24  | 0   | SDBE7          | 46  | I   | A2             | 68  | 0            | SDBE4          |

| 3   | 1/0 | 1              | 25  | I   | SDBI7          | 47  | I   | <b>A</b> 3     | 69  | I            | SDB14          |

| 4   | 1/0 | 2              | 26  | 0   | SDBE6          | 48  | I/0 | D4             | 70  | 0            | SDB03          |

| 5   | 1/0 | 3              | 27  | 0   | SDB05          | 49  | I/0 | D5             | 71  | I            | SDBI2          |

| 6   | I/0 | 4              | 28  | I   | SDB15          | 50  | I/0 | D6             | 72  | 0            | SDB01          |

| 7   | 1/0 | 5              | 29  | 0   | SDB04          | 51  | I/0 | D7             | 73  | 0            | SDBEO          |

| 8   | I/0 | 6              | 30  | 0   | SDBE3          | 52  | 1/0 | DP             | 74  | I            | SDBIO          |

| 9   | 1/0 | 7              | 31  | I   | SDBI3          | 53  | 0   | INTR           | 75  | I            | RST            |

| 10  | 1/0 | P              | 32  | 0   | SDB02          | 54  | I   | 1/01           | 76  | 0            | DREQ           |

| 11  | 0   | INIT           | 33  | 0   | SDBE2          | 55  | I   | C/DI           | 77  | I            | WT             |

| 12  | 0   | TARG           | 34  | I   | SDBI1          | 56  | I   | SELI           | 78  | I            | WIG            |

| 13  | 0   | I/00           | 35  | 0   | SDBE1          | 57  | I   | MSG1           | 79  | 1/0          | D2             |

| 14  | 0   | C/DO           | 36  | 0   | SDBOO          | 58  | I   | REQI           | 80  | 1/0          | D3             |

| 15  | 0   | SELO           | 37  | I   | <del>CS</del>  | 59  | I   | RSTI           | 81  | Power supply | VSS            |

| 16  | 0   | MSGO           | 38  | I   | CLK            | 60  | I   | ACKI           | 82  | Power supply | VDD            |

| 17  | 0   | REQO           | 39  | I   | RD             | 61  | I   | BSYI           | 83  | Power supply | VDD            |

| 18  | 0   | RSTO           | 40  | I   | RDG            | 62  | I   | ANTI           | 84  | Power supply | VSS            |

| 19  | 0   | ACKO           | 41  | I   | DRESP          | 63  | I   | SDBIP          | 85  | Power supply | VSS            |

| 20  | 0   | BSYO           | 42  | 1/0 | DO             | 64  | 0   | SDB07          | 86  | Power supply | VDD            |

| 21  | 0   | ATNO           | 43  | 1/0 | Dl             | 65  | 0   | SDB06          | 87  | Power supply | VDD            |

| 22  | 0   | SDBEP          | 44  | I   | A0             | 66  | I   | SDB16          | 88  | Power supply | VSS            |

Figure 2.1.1 Pin assignments

| Signal<br>name       | Pola-<br>rity | I/0 | Pin                  | Q'ty | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|---------------|-----|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>      |               | I   | 82<br>83<br>86<br>87 | 4    | +5 V power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>SS</sub>      |               | I   | 81<br>84<br>85<br>88 | 4    | Ground (O V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLK                  | -             | I   | 38                   | 1    | A clock input for controlling the SPC internal operation and the data transfer speed.                                                                                                                                                                                                                                                                                                                                                                                                           |

| RST                  | -             | I   | 75                   | 1    | An asynchronous reset signal for clearing the internal circuits in SPC.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CS                   | -             | I   | 37                   | 1    | A selection enable signal for accessing an internal<br>register in SPC. When this input signal is active,<br>the following input/output signals are valid:<br>RD, RDG<br>WT, WTG<br>A3 to A0<br>D7 to D0, DP                                                                                                                                                                                                                                                                                    |

| A3<br>A2<br>A1<br>A0 | +             | I   | 47<br>46<br>45<br>44 | 4    | Address input signals for selecting an internal register<br>in SPC.<br>MSB: A3, LSB: A0<br>When CS input is active, read/write is enabled in an<br>internal register selected by these address inputs via<br>data bus lines D7 to D0 and DP.                                                                                                                                                                                                                                                    |

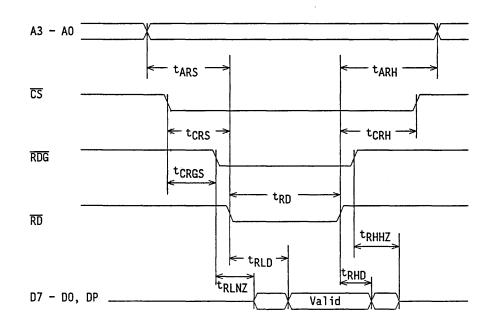

| RD<br>RDG            | -             | I   | 39<br>40             | 2    | These strobe inputs are used for reading out the contents of the SPC internal register, and are effective only when $\overline{\text{CS}}$ input is active. While $\overline{\text{RDG}}$ input is active, the contents of an internal register selected by A3 to A0 inputs are placed on data bus lines D7 to D0 and DP. For a data transfer cycle in the program transfer mode, the trailing edge of $\overline{\text{RD}}$ input is used as a timing signal indicating the end of data read. |

| <b>ज</b> ा           | -             | I   | 77                   | 1    | This strobe input is used for writing data into an SPC internal register, and is effective only when $\overline{CS}$ input is active. On the trailing edge of this signal, data placed on data bus lines D7 to D0 and DP are loaded into an internal register selected by A3 to A0 inputs. (Except when A3 = A2 = A1 = A0 = 'H')<br>For a data transfer cycle in the program transfer mode, the trailing edge of this signal is used as a timing signal indicating data-ready state.            |

| WTG                  | -             | I   | 78                   | 1    | While this signal is active, data placed on data bus lines<br>D7 to D0 and DP are output to HDB7 to HDB0 and HDBP if the<br>following input conditions are satisfied:<br>$\overline{CS} = L'$<br>A3 = A2 = A1 = A0 = 'H'<br>HIN = 'H'                                                                                                                                                                                                                                                           |

Table 2.1.1 Input/output signals (Continued on next sheet)

| Signal<br>name                                                                | Pola-<br>rity | I/0 | Pin                                                | Q'ty | Function                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------|---------------|-----|----------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0<br>DP                            | +             | 1/0 | 51<br>50<br>49<br>48<br>80<br>79<br>43<br>42<br>52 | 9    | Used for write/read data into/from an internal register in<br>SPC. This data bus is three-state and bidirectional.<br>MSB: D7<br>LSB: D0<br>Odd parity bit: DP<br>When the CS and RDG inputs are active, the contents of the<br>internal register are output to the data bus (read<br>operation). In operations other than read, this data bus<br>is kept at a high impedance level. |

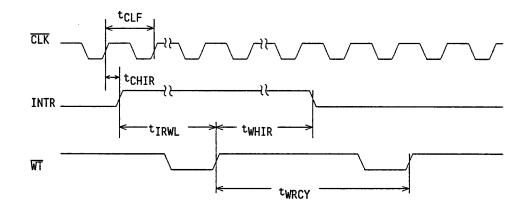

| INTR                                                                          | +             | 0   | 53                                                 | 1    | Requests an interrupt to indicate completion of SPC.<br>internal operation or occurrence of an error. Interrupt<br>masking is allowed except for an interrupt caused by RSTI<br>input (reset condition in SCSI). When an interrupt<br>request is permitted, the INTR signal remains active<br>until the cause of the interrupt is cleared.                                           |

| SDBI7<br>SDBI6<br>SDBI5<br>SDBI4<br>SDBI3<br>SDBI2<br>SDBI1<br>SDBI0<br>SDBIP | +             | I   | 25<br>66<br>28<br>69<br>31<br>71<br>34<br>74<br>63 | 9    | Used as input from the SCSI data bus.<br>MSB: SDBI7<br>LSB: SDBI0<br>Odd parity bit: SDBIP<br>Parity checking for the SCSI data bus is programmable.                                                                                                                                                                                                                                 |

| SDB07<br>SDB06<br>SDB05<br>SDB04<br>SDB03<br>SDB02<br>SDB01<br>SDB00<br>SDB0P | ÷             | 0   | 64<br>65<br>27<br>29<br>70<br>32<br>72<br>36<br>23 | 9    | Used as outputs to the SCSI data bus.<br>MSB: SDB07<br>LSB: SDB00<br>Odd parity bit: SDB0P<br>If the bus driver is an open collector type, there signals<br>can be supplied directly to the driver circuit. If the<br>bus driver is a three-state type, these signals are used<br>as data, and the SDBE7 to SDBE0 and SDBEP signals are used<br>as drive enable signals.             |

| SDBE7<br>SDBE6<br>SDBE5<br>SDBE4<br>SDBE3<br>SDBE2<br>SDBE1<br>SDBE0<br>SDBEP | +             | 0   | 24<br>26<br>67<br>68<br>30<br>33<br>35<br>73<br>22 | 9    | Used as drive enable signals (corresponding to respective<br>bit positions) where a three-state buffer is used for the<br>SCSI data bus. SDBE7 to SDBE0 and SDBEP correspond to SDB07<br>to SDB00 and SDB0P, respectively. The relationship with<br>SCSI bus phase is shown below.                                                                                                   |

Table 2.1.1 Input/output signals (Continued on next sheet)

| Signal                                                               | Pola-     | I/0 | Pin                                                | Q'ty | Function                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------|-----------|-----|----------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SELI<br>BSYI<br>REQI<br>ACKI<br>MSGI<br>C/DI<br>I/OI<br>ATNI<br>RSTI | rity<br>+ | I   | 56<br>61<br>58<br>60<br>57<br>55<br>54<br>62<br>59 | 9    | Used for receiving SCSI control signals. The outputs of<br>the SCSI receiver circuit can be connected directly.<br>Note: Waveform distortion or any other disturbance should<br>not occur in the REQI and ACKI signals which are<br>used as timing control signals for sequencing data<br>transfer.                                                                                                       |

| SELO<br>BSYO<br>REQO<br>ACKO<br>MSGO<br>C/DO<br>I/OO<br>ATNO<br>RSTO | +         | 0   | 15<br>20<br>17<br>19<br>16<br>14<br>13<br>21<br>18 | 9    | Used for outputting SCSI control signals. The following<br>signals become active only when SPC serves as a TARGET;<br>otherwise, these signals are always low.<br>REQO, MSGO, C/DO, I/OO<br>The following signals become active only when SPC serves as<br>an INITIATOR; otherwise, these signals are always low.<br>ACKO, ATNO                                                                           |

| INIT<br>TARG                                                         | +         | 0   | 11 12                                              | 2    | Used for indicating the SPC operation state. These signals<br>are also available as control signals for the SCSI<br>driver/receiver circuit.<br><u>INIT TARG</u> Status<br><u>'L' 'L' SPC is not connected with SCSI.</u><br><u>'L' 'H' SPC is executing RESELECTION phase, or is<br/>operating as a TARGET.</u><br><u>'H' 'L' SPC is executing SELECTION phase, or is<br/>operating as an INITIATOR.</u> |

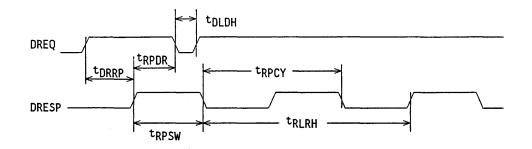

| DREQ                                                                 | +         | 0   | 76                                                 | 1    | At a data transfer cycle in DMA mode, the DREQ signal is<br>used to indicate a request for data transfer between SPC<br>and the external buffer memory. In DMA mode, data is<br>routed as shown below.<br>• Output operation<br>External buffer memory                                                                                                                                                    |

Table 2.1.1 Input/output signals (Continued on next sheet)

- 8 -

| Table | 2.1.1 | Input/output | signals | (Continued) |

|-------|-------|--------------|---------|-------------|

| labie | 2.1.1 | input/output | signais | (continued) |

| Signal<br>name                                                       | Pola-<br>rity | I/0 | Pin                                        | Q'ty | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------|---------------|-----|--------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

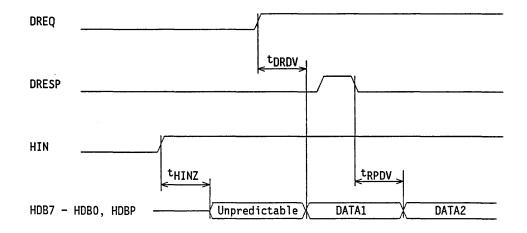

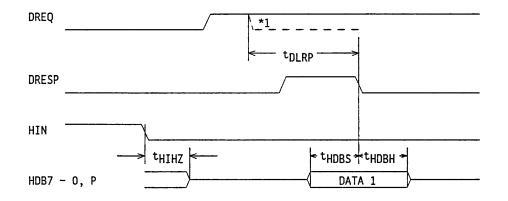

|                                                                      |               |     |                                            |      | <ul> <li>Input operation<br/>(SCSI)</li> <li>SDBI7 to SDBI0 and SDBIP pins</li> <li>SPC internal data buffer register (8 bytes)</li> <li>HDB7 to HDB0 and HDBP pins</li> <li>External buffer memory</li> <li>In an output operation, this signal becomes active to request data transfer from the external buffer memory when the SPC internal data buffer register has free space available. In an input operation, it becomes active to request data transfer to the external buffer memory when the SPC internal buffer register contains valid data.</li> </ul> |

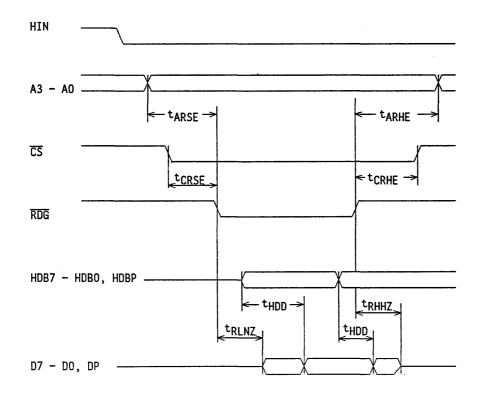

| DRESP                                                                | +             | I   | 41                                         | 1    | Used as an response signal to the above data transfer<br>request signal (DREQ) in DMA mode data transfer cycle.<br>Pin DRESP must be supplied with a pulse signal at the end<br>of each byte that is transferred. In an output operation,<br>SPC uses the trailing edge of the DRESP signal for sampling<br>data on HDB7 to HDB0 and HDBP bus lines.<br>In an input operation, SPC holds data to be transferred<br>onto HDB7 to HDB0 and HDBP bus lines until the trailing<br>edge of the DRESP signal.                                                             |

| HDB7<br>HDB6<br>HDB5<br>HDB4<br>HDB3<br>HDB2<br>HDB1<br>HDB0<br>HDBP | +             | I/0 | 9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>10 | 9    | Three-state, bidirectional data bus for transferring data<br>to/from the external buffer memory in DMA mode data<br>transfer cycle.<br>MSB: HDB7<br>LSB: HDB0<br>Odd parity bit: HDBP<br>The data transmission direction depends on the HIN input<br>signal.<br><u>HIN HDBn Operation</u><br>'L' Input mode Output<br>'H' Output mode Input                                                                                                                                                                                                                         |

| HIN                                                                  | +             | I   | 1                                          | 1    | This signal indicates transmission direction along data<br>bus lines HDB7 to HDB0 and HDBP in DMA transfer mode.<br>Transmission direction must be coordinated with the SPC<br>internal operation to be executed. When the HIN signal<br>is low, data bus lines HDB7 to HDB0 and HDBP are put in<br>the high impedance state (input mode). When the HIN signal<br>is high, they are put in the output mode.                                                                                                                                                         |

#### CHAPTER 3

FUNCTIONS

## 3.1 FUNCTIONAL BLOCKS

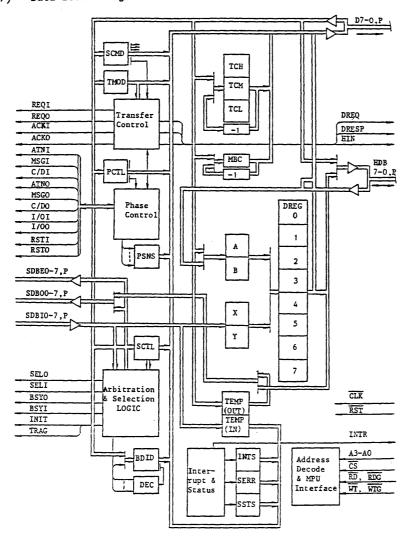

Figure 3.1.1 shows the SPC functional block diagram. SPC mainly consists of the following functional blocks:

- Internal register block

- (1) (2) (3) (4) (5) (6) (7) MPU interface control block

- Bus phase control block

- Arbitration/selection sequence control block Transfer sequence control block Transfer byte counter block

- Data buffer register block

Figure 3.1.1 SPC functional block diagram

- 10 -

#### 3.2 INTERNAL REGISTER

SPC has internal registers consisting of 17 bytes that are accessible from an external circuit. These internal registers are used for controlling SPC internal operation and indicating SPC processing status/result status.

#### 3.2.1 Addressing

A unique address is assigned to each internal register, and a particular register is identified by address bits A3 to A0. Table 3.2.1 shows internal register addressing.

#### 3.2.2 Internal Register Assignments

Table 3.2.2 shows the bit assignment to each internal register. When accessing an internal register (in read/write), remember the following:

- (1) The internal register block includes the read-only/write-only register and those having different meanings in read and write operations.

- (2) A write to the read-only register is ignored.

(3) If the write-only register is read out, the data and parity bit are undefined.

(4) At bit positions indicating "\_\_\_\_" for a write in Table 3.2.2, either 1 of 0, or may be written.

| Table 3.2.1 | Internal | register | addressing |

|-------------|----------|----------|------------|

|             |          |          |            |

| <del>CS</del> | A3 | A2 | A1 | A0 | OP     | Register Name                      | Abbr. |

|---------------|----|----|----|----|--------|------------------------------------|-------|

| 0             | 0  | 0  | 0  | 0  | R<br>W | Bus Device ID                      | BDID  |

| 0             | 0  | 0  | 0  | 1  | R      | SPC Control                        | SCTL  |

| 0             | 0  | 0  | 1  | 0  | R<br>W | Command                            | SCMD  |

| 0             | 0  | 0  | 1  | 1  | R      | Transfer Mode                      | TMOD  |

| 0             | 0  | 1  | 0  | 0  | R      | Interrupt Sense<br>Reset Interrupt | INTS  |

| 0             | 0  | 1  | 0  | 1  | R      | Phase Sense                        | PSNS  |

|               | U  | T  | 0  | 1  | W      | SPC Diagnostic Control             | SDGC  |

|               | •  | 4  | •  | ~  | R      | SPC Status                         | SSTS  |

| 0             | 0  | 1  | 1  | 0  | W      |                                    |       |

| -             | •  | •  |    |    | R      | SPC Error Status                   | SERR  |

| 0             | 0  | 1  | 1  | 1  | W      |                                    |       |

| 0             | 1  | 0  | 0  | 0  | R      | Phase Control                      | PCTL  |

|               | 1  | _  | •  |    | R      | Modified Byte Counter              | MBC   |

| 0             | 1  | 0  | 0  | 1  | W      |                                    |       |

| 0             | 1  | 0  | 1  | 0  | R<br>W | Data Register                      | DREG  |

| 0             | 1  | 0  | 1  | 1  | R<br>W | Temporary Register                 | TEMP  |

| 0             | 1  | 1  | 0  | 0  | R      | Transfer Counter High              | тсн   |

| 0             | 1  | 1  | 0  | 1  | R      | Transfer Counter Middle            | TCM   |

| 0             | 1  | 1  | 1  | 0  | R      | Transfer Counter Low               | TCL   |

| 0             | 1  | 1  | 1  | 1  | R<br>W | External Buffer                    | EXBF  |

| No. | Name              | OP   | 7             | 6                                    | 5              | 4              | 3              | 2              | 1                                     | 0 1              | P        |  |

|-----|-------------------|------|---------------|--------------------------------------|----------------|----------------|----------------|----------------|---------------------------------------|------------------|----------|--|

| 10. | (Abbr.)           | 01   | ,             | U                                    | 5              | т              |                |                | -                                     | Ŭ                | <b>'</b> |  |

|     | Bus               | R    |               |                                      | S              | CSI Bus        | Device I       | D              |                                       |                  |          |  |

|     | Device ID         |      | #7            | #6                                   | #5             | #4             | #3             | #2             | #1                                    | #0               | '0'      |  |

|     | (BDID)            | W    |               |                                      |                |                |                | ID4            | Bus Devic<br>ID2                      | e ID<br>I ID1    | -        |  |

| 2   | SPC               | R    | Reset         | Control                              | Diag           | ARBIT          | Parity         |                | Reselect                              |                  | P        |  |

| -   | Control           |      | and           | Reset                                | Mode           | Enable         | Enable         |                | Enable                                | Enable           |          |  |

|     | (SCTL)            | W    | Dis-          |                                      |                |                |                |                |                                       |                  |          |  |

|     |                   |      | able          |                                      |                |                |                |                |                                       |                  |          |  |

| 3   | Command<br>(SCMD) | R    | Comm          | and Code                             |                | RST            | Inter-         | Irans          | fer Modif                             | ier              | Р        |  |

|     | (SCHD)            | W    | COnni         |                                      |                | Out            | cept           | PRG            | 101                                   | Term.            |          |  |

|     |                   |      |               | 1                                    |                |                | Xfer           | Xfer           | , , , , , , , , , , , , , , , , , , , | Mode             |          |  |

| 4   | Transfer          | R    | Sync.         |                                      |                |                |                |                |                                       |                  |          |  |

|     | Mode              | L.,- | Xfer          |                                      | Transfe        | r              | Min. Tr        |                | '0'                                   | '0'              | Р        |  |

|     | (TMOD)            | W    |               | 4                                    | ffset<br>2     | 1              | Peri<br>2      | 00<br>1        |                                       |                  |          |  |

| 5   | Phase             | R    | Bus           |                                      | ۷.             | L              | <u> </u>       | <u> </u>       |                                       | L                |          |  |

| Ĭ   | Control           | "    | Free          |                                      |                |                |                |                |                                       |                  |          |  |

|     | (PCTL)            | W    | Inter-        |                                      | 1              | 0'             |                | MSG            | C/D                                   | I/D              | Р        |  |

|     |                   |      | rupt          |                                      |                |                |                | Out            | Out                                   | Out              |          |  |

| 6   | Phase             | R    | Enable<br>REO | ACK                                  | ATN            | SEL            | BSY            | MSG            | C/D                                   | 1/0              | P        |  |

|     | Sense             | "    | INEQ.         | TON                                  | 710            | JLL            |                | Pisu           | 0/0                                   | 1/0              | •        |  |

|     | (PSNS)            | W    |               |                                      |                |                |                |                |                                       |                  |          |  |

|     | ··                | L    |               | Internal Data Register (8 Byte FIFO) |                |                |                |                |                                       |                  |          |  |

| 7   | Data<br>Register  | R    |               | Inter                                | nal Dat        | a Kegist       | er (8 By       | te FIFU        | )                                     |                  | Р        |  |

|     | (DREG)            | W    | Bit7          | 6                                    | 5              | 4              | 3              | 2              | 1                                     | 0                | ſ        |  |

|     | (====)            |      |               |                                      |                |                |                | -              |                                       |                  |          |  |

| 8   | Transfer          | R    |               |                                      | _              |                |                |                |                                       |                  |          |  |

|     | Counter           | W    | D:+ 22        | 22                                   |                |                | unter Hi<br>19 | igh (MSB<br>18 |                                       | 16               | P        |  |

|     | High<br>(TCH)     | W    | Bit23         | 22                                   | 21             | 20             | 1 19           | 18             | 17                                    | 16               |          |  |

| 9   | Transfer          | R    |               |                                      |                |                |                |                |                                       |                  | P        |  |

|     | Counter           |      |               |                                      |                |                | Middle (       |                |                                       | •                |          |  |

|     | Mid.              | W    | Bit15         | , 14                                 | 13             | 12             | 11             | 10             | 9                                     | 8                |          |  |

| 10  | (TCM)<br>Transfer | R    |               |                                      |                | ļ              |                | ļ              |                                       |                  | <u> </u> |  |

| 10  | Counter           |      |               | I                                    | l<br>Tra       | l<br>Insfer Co | <br>Dunter Lo  | W (LSB)        | l                                     | 1                | Р        |  |

|     | Low               | W    | Bit7          | 6                                    | 5              | 4              | 3              | 2              | 1                                     | 0                | '        |  |

|     | (TCL)             |      |               |                                      |                |                |                |                |                                       |                  |          |  |

| 11  | Interrupt         | R    | Sele-         | Rese-                                | Dis-           | Com-           | Ser-           | Time           | SPC                                   | Reset            |          |  |

|     | Sense<br>(INTS)   |      | cted          | lected                               | Con-<br>nected | mand<br>Com-   | vice<br>Re-    | Out            | Hard<br>Error                         | Condi-<br>  tion | P        |  |

|     | (1013)            |      |               |                                      | nected         | plete          | quired         |                |                                       |                  |          |  |

|     |                   | W    |               | Reset Interrupt                      |                |                |                |                |                                       |                  |          |  |

|     |                   |      |               |                                      |                |                | -              |                |                                       |                  |          |  |

| 12  | SPC               | R    |               | ected                                | SPC            | Xfer in        |                | TC=0           | DREG St                               |                  | P        |  |

|     | Status<br>(SSTS)  | 1    | INIT          | TARG                                 | Busy           | Pro-           | RST            |                | FULL                                  | EMPTY            |          |  |

|     | (3313)            | W    |               | gress                                |                |                |                |                |                                       |                  |          |  |

| 1   |                   | 1 "  |               |                                      |                | -              | _              |                |                                       |                  | 1-       |  |

|     |                   | 1    | •             |                                      |                |                |                |                |                                       |                  | 1        |  |

Table 3.2.2 Internal register bit assignment (Continued on next sheet)

| No. | Name<br>(Abbr.)       | OP | 7            | 6               | 5            | 4             | 3              | 2              | 1               | 0               | Р |

|-----|-----------------------|----|--------------|-----------------|--------------|---------------|----------------|----------------|-----------------|-----------------|---|

| 13  | SPC Error<br>Status   | R  | Data<br>SCSI | Error<br>SPC    | 101          | '0'           | TC P-<br>Error | Phase<br>Error | Short<br>Period | Offset<br>Error | Ρ |

|     | (SERR)                | W  |              |                 |              | -             | _              |                |                 |                 |   |

| 14  | Temporary<br>Register | R  | Bit7         | 6               | emporar<br>5 | y Data (<br>4 | Input: F       | rom SCS<br>2   | I)<br>1         | 0               | Р |

|     | (TĚMP)                | W  | Bit7         |                 | emporar<br>5 | y Data (<br>4 | Output:        | to SCSI<br>2   | )<br>1          | 0               | Р |

| 15  | External<br>Buffer    | R  |              | External Buffer |              |               |                |                |                 |                 | Р |

|     | (EXBF)                | W  | Bit7         | 6               | 5            | 4             | 3              | 2              | 1               | 0               |   |

| 16  | Modified<br>Byte      | R  |              |                 | 0'           |               | Bit3           | M<br>2         | BC<br>1         | 0               | Р |

|     | Counter<br>(MBC)      | W  |              |                 |              |               |                |                |                 |                 |   |

| 17  | SPC<br>Diagnostic     | R  |              |                 |              |               |                |                |                 |                 | - |

|     | Control<br>(SDGC)     | W  | Diag<br>REQ  | Diag<br>ACK     |              |               | Diag<br>BSY    | Diag<br>MSG    | Diag<br>C/D     | Diag<br>I/O     | - |

Table 3.2.2 Internal register bit assignment (Continued)

## 3.3 MAJOR OPERATIONS

#### 3.3.1 MPU Interface Control Block

The MPU interface control block selects a specified internal register and controls a read/write operation. Also, this block generates an interrupt and indicates its cause. (This is done to report the result status of SPC internal operation, and the detection of an error, if encountered.)

#### 3.3.2 Bus Phase Control Block

The bus phase control block generates a specified bus phase for SCSI and controls its sequence of executions. Also, this block supervises SCSI status, and responds to the bus phase being executed if necessary.

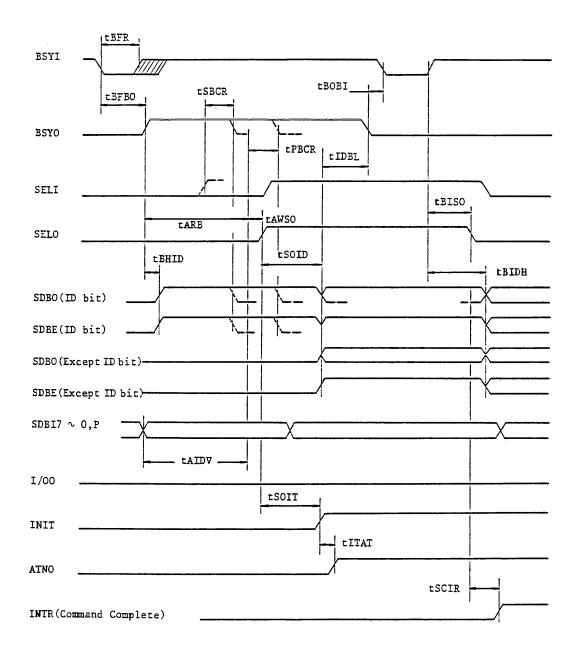

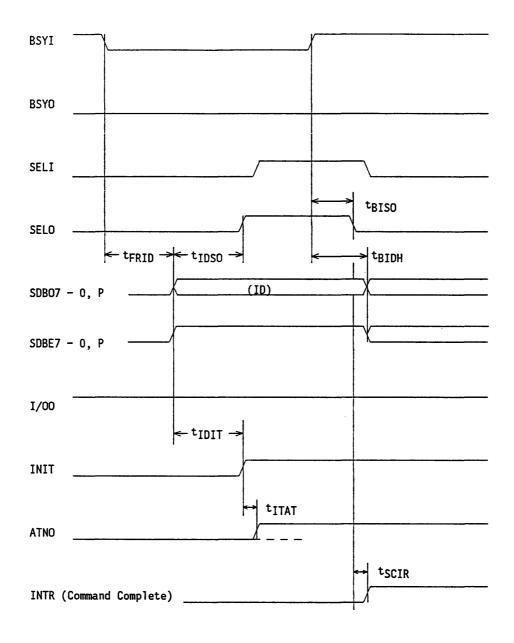

#### 3.3.3 Arbitration/Selection Sequence Control Block

This sequence control block executes the ARBITRATION phase with the SCSI-specified timing and obtains permission to use the SCSI bus. Then, it carries out the SELECTION/RESELECTION phase and checks the response from the selected/reselected device. Also, this block detects the SELECTION/RESELECTION phase on SCSI, and checks the bus device ID specified in the internal register against that specified on the SCSI data bus. Then, if this block finds that SPC has been selected by another SCSI bus device, it executes the response sequence for the SELECTION/RESELECTION phase.

#### 3.3.4 Transfer Sequence Control Block

This sequence control block controls the DATA IN/OUT, COMMAND, STATUS, and MESSAGE IN/OUT phases to be executed in SCSI. The following two modes are available for execution of these transfer phases:

(1) Manual transfer mode

In manual transfer mode, the MPU interface is used for transferring data and sending/receiving/checking the REQ/ACK signals on SCSI.

(2) Hardware transfer mode

In hardware transfer mode, SPC controls the SCSI transfer sequence according to the transfer mode and transfer byte count specified in the internal registers, and reports the end result of transfer. Asynchronous and synchronous mode transfer operations can be executed. In the asynchronous mode transfer operation, the REQ and ACK signals are controlled by the interlock protocol. In the synchronous mode transfer operation, a maximum of eight-byte offset is available for the DATA IN/OUT phase. The hardware transfer mode is subdivided into two according to the data routing:

(a) Program transfer mode

Data is routed via MPU interface in the following data paths: SCSI  $\leftrightarrow$  Data buffer register  $\leftrightarrow$  Data bus lines D7 to D0 and DP.

(b) DMA mode

Data is routed using DREQ and DRESP signals for DMA control in the following data paths:

SCSI  $\leftrightarrow$  Data buffer register  $\leftrightarrow$  Data bus lines HDB7 to HDB0 and HDBP.

#### 3.3.5 Transfer Byte Counter Block

This counter indicates the transfer byte count used for hardware transfer mode operation in SPC. It consists of 24 bits. Except for execution of a special transfer operation (padding), the transfer byte counter is decresed by one each time one byte of data is transferred on SCSI. The transfer byte counter is also used as a timer for supervising the waiting time for a response to be returned from the selected SCSI bus device during execution of the selection/reselection phase. On the MPU interface, the transfer byte counter is treated as three separate internal registers (TCH, TCM, TCL), each being one byte long.

#### 3.3.6 Data Buffer Register Block

The data buffer register block is used in execution of a hardware transfer mode operation in SPC. It has a capacity of eight bytes, and operates on the FIFO principle for each byte. In an input operation (from SCSI to SPC), data received from SCSI is loaded into the buffer register. In DMA mode, transfer request signal DREQ is generated to the external buffer memory. Also, in program transfer mode, data can be read out from this buffer register. In an output operation (from SPC to SCSI), data supplied from the MPU interface (program transfer mode) or external buffer memory (DMA mode) is loaded into the buffer register and then sent to SCSI. In this case, a maximum of eight bytes of data is prefetched into SPC. The MPU interface treats 8-byte data buffer register as if it was a one-byte internal register. In an input operation, the byte locations holding valid data are selected in succession for reading out. In an output operation, the empty byte locations are selected in succession for writing in.

#### CHAPTER 4

#### OPERATIONAL DESCRIPTION

#### 4.1 BDID REGISTER

| OP | 7  | 6  | 5            | 4              | 3              | 2               | 1             | 0  | Р   |

|----|----|----|--------------|----------------|----------------|-----------------|---------------|----|-----|

| R  | #7 | #6 | Bit Si<br>#5 | gnifican<br>#4 | t Bus De<br>#3 | vice ID<br>#2   | #1            | #0 | '0' |

| W  |    |    |              |                | SCSI B<br>ID4  | us Devic<br>ID2 | e ID<br>  ID1 | —  |     |

#### Write Operation (Bits 2 to 0):

The BDID register specifies an SCSI bus device identifier (ID) with a three-bit binary number. This setting must be completed before resetting the SCTL register's bit 7 (Reset & Disable). Bits 2 to 0 are not affected by any resetting except power on reset.

#### Read Operation:

The BDID register indicates an SCSI physical device address (bus device ID) with each bit. An SCSI physical device address is decoded from the values at bits 2 to 0 specified in a write operation to the BDID register described above. One of the bits is 'one', the others are all 'zeros'. The SCSI bus usage priority is assigned in descending order from bit 7 to bit 0. Using a bus device ID indicated in this register, SPC executes the ARBITRATION phase. Also, if a SELECTION/RESELECTION phase condition occurs in SCSI, the value of the SCSI data bus is checked against the contents of this register to see whether the SPC has been selected/reselected or not.

#### 4.2 SCTL REGISTER

| OP     | 7                     | 6     | 5 | 4               | 3 | 2 | 1                  | 0             | Р |

|--------|-----------------------|-------|---|-----------------|---|---|--------------------|---------------|---|

| R<br>W | Reset<br>&<br>Disable | Reset |   | ARBIT<br>Enable |   |   | Reselect<br>Enable | INT<br>Enable | Р |

#### Bit 7: Reset & Disable

Bit 7 indicates a reset instruction to the internal registers and control circuits in SPC. When this bit is 1, SPC is reset and logically disconnected from SCSI (put in the disable state). Execution of the hardware reset (RST input = 'L') causes this bit to be 1. To enable the SCSI operation, bit 7 must be made zero to release the disable state.

#### Bit 6: Control Reset

Bit 6 instructs resetting of the data transfer control circuit in SPC. That is, the data transfer control circuit is reset when this bit is 1. Even if the control reset is executed by this bit during the SPC operates with SCSI, the SPC keeps connected state with SCSI. The reset function of this bit should be used for resetting the data transfer control circuit while it is connected with SCSI. More specifically, it should be used when an error is indicated by bit 1 (SPC Hardware Error) of the INTS register during execution of the SCSI transfer phase or when a timeout occurs before completion of Transfer command execution (supervised by the MPU program). Bit 1 (SPC Hardware Error) of the INTS register and the SERR register are cleared by the reset function of this bit.

- Note: This reset function initializes the SPC transfer control circuit. So, when the SPC serves as an INTIATOR, the following consideration is required:

- Since the REQ signal may be received during resetting, the first byte should be transferred in manual mode after resetting.

#### Bit 5: Diagnostic Mode

When bit 5 is 1, SPC enters a diagnostic mode and is disconnected from SCSI. A diagnostic mode allows pseudo-execution of the SCSI operation using the SDGC register (to be explained later).

#### Bit 4: Arbitration Enable

Bit 4 indicates whether the ARBITRATION phase is executable in SCSI or not. 1 ... ARBITRATION phase executable

- 0 ... ARBITRATION phase nonexecutable

With this bit set to 1, the Select command causes SPC to execute the ARBITRATION phase. And, if the SPC win the arbitration, it executes the SELECTION/RESELECTION phase. With this bit set to 0, the Select command causes SPC to execute the SELECTION phase without the ARBITRATION phase. As long as bit 4 is 0, SPC returns no response to a reselection request from other SCSI bus device. That is, no response is made even if bit 1 (Reselect Enable) of this register is set to 1. Remember that bit 4 must be set correctly before clearing bit 7 (Reset & Disable) of the SCTL register. Note also that this bit should not be changed in other than a diagnostic mode after clearing bit 7 of the SCTL register.

#### Bit 3: Parity Enable

Bit 3 indicates whether the parity of data received from the SCSI data bus is to be checked or not.

1 ... Parity of the data received from the SCSI data bus is checked.

0 ... Parity of the data received from the SCSI data bus is not checked. Regardless of the value of this bit, the parity of the data to be sent to the SCSI data bus is ensured. Also, the parity of the data on the SPC internal data bus is always checked. While SPC is connected with SCSI, this bit should not be changed.

A parity check is carried out in the following cases:

(1) When checking an ID value placed on the data bus upon detection of the SELECTION/RESELECTION phase in SCSI: Detection of a parity error causes no response to the SELECTION/RESELECTION phase even if the SCSI bus device ID has been matched.

(2) When receiving data from SCSI in an input transfer sequence: If a parity error is detected in a data byte, the relevant parity bit value is corrected and the data byte with the corrected parity is sent to the MPU/DMA data bus.

#### Bit 2: Select Enable

- 1 ... SPC responds as a TARGET device to the SELECTION phase in SCSI.

- 0 ... SPC does not respond to the SELECTION phase in SCSI.

- Note: If SPC has already detected the SELECTION phase during an attempt to set this bit to 0, SPC responds to the SELECTION phase as a TARGET device. In this case, the 0 setting is effective for the subsequent SELECTION phase (with no response).

#### Bit 1: Reselect Enable

- 1 ... SPC responds as an INITIATOR to the RESELECTION phase in SCSI.

- 0 ... SPC does not respond to the RESELECTION phase in SCSI.

- Note: If SPC has already detected the RESELECTION phase during an attempt to set this bit to 0, SPC responds to the RESELECTION phase as an INITIATOR. In this case, the 0 setting is effective for the subsequent RESELECTION phase (with no response).

#### Bit O: Interrupt Enable

Bit O serves as a mask for enabling/disabling an interrupt (INTR) output from the SPC.

1 ... Interrupt enabled

0 ... Interrupt disabled

An interrupt due to a RESET condition detected in SCSI cannot be masked. Regardless of the value of this bit, an interrupt event is always indicated in the INTS register. This makes available poll-mode control in an interrupt disabled state.

#### 4.3 SCMD REGISTER

| OP          | 7  | 6       | 5   | 4          | 3                      | 2                    | 1                | 0                      | Р |

|-------------|----|---------|-----|------------|------------------------|----------------------|------------------|------------------------|---|

| R<br>/<br>W | Co | mmand C | ode | RST<br>Out | Inter-<br>cept<br>Xfer | Trans<br>PRG<br>Xfer | fer Mod<br>  'O' | ifier<br>Term.<br>Mode | P |

#### 4.3.1 Register Functions

The SCMD register is used for giving a command to SPC. Writing into this register causes SPC to initiate the command processing specified at bits 7 to 5.

- 18 -

Bit 7 to 5: Command Code

| Bit 7 | 6 | 5 | Command        |

|-------|---|---|----------------|

| 0     | 0 | 0 | Bus Release    |

| 0     | 0 | 1 | Select         |

| 0     | 1 | 0 | Reset ATN      |

| 0     | 1 | 1 | Set ATN        |

| 1     | 0 | 0 | Transfer       |

| 1     | 0 | 1 | Transfer Pause |

| 1     | 1 | 0 | Reset ACK/REQ  |

| 1     | 1 | 1 | Set ACK/REQ    |

#### Bit 4: RST Out

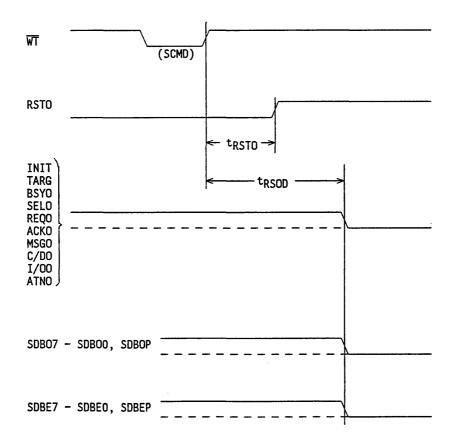

If bit 7 (Reset & Disable) of the SCTL register is 0, setting 1 in bit 4 of this SCMD register sends the RST signal (RSTO pin) to SCSI. When bit 4 is set to 1, a command being executed or waiting for execution in SPC is cleared and all signals to SCSI other than RST are deactivated. To ensure for the SCSI timing requirements, MPU must maintain this bit at 1 for more than 25 microseconds.

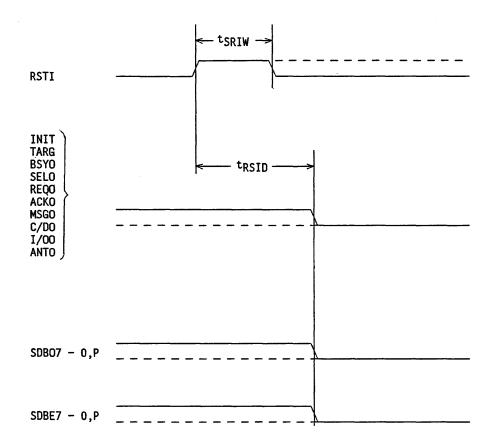

Note: If the RST signal (RSTI pin) is received from SCSI with this bit set to 0, the operation sequence is as follows:

• A command being executed or waiting for execution in the SPC is cleared.

- All signals to the SCSI are deactivated.

- An interrupt condition (non-maskable) is generated.

Whenever bit 7 (Reset & Disable) of the SCTL register is 0, the SPC always accepts the RST signal from the SCSI.

#### Bit 3: Intercept Transfer

Bit 3 specifies the special data transfer mode. It is valid only when SPC serves as an INITIATOR.

This bit should be set to 1 together with the Set ATN, Set ACK/REQ, or Bus Release command (Bus Release command has no effect when SPC has been connected with SCSI as an INITIATOR). And, this bit should be reset together with the Reset ACK/REQ command. (When two or more bytes are transferred using the Set ACK/REQ and Reset ACK/REQ commands, this bit must be reset on issuance of the Reset ACK/REQ command for the last byte.) With bit 3 of SCMD register set to 1, executing manual transfer (MPU- controlled transfer using the Set ACK/REQ and Reset ACK/REQ commands) does not change the contents of the eight-byte data buffer register in SPC. Therefore, if a TARGET changes bus phase to such as MESSAGE IN during execution of the DATA OUT phase, this intercept transfer mode makes it possible to optionally restart the DATA OUT phase at the end of the interrupting phase. The phase change during transfer execution is reported by a 'service required' interrupt. To execute this intercept transfer mode, bit 3 of SCMD register must be set to 1 prior to the resetting of an interrupt (an interrupt must be reset after bit 3 is set to 1). Even when not using the intercept transfer mode, bit 3 may be specified for resetting a 'service required' interrupt. In this case, bit 3 must be set/reset together with the Bus Release command. For more details, see the description of bit 3 (Service Required) of the INTS register.

#### Bits 2 to 0: Transfer Modifier

Bits 2 to 0 are used as a field for specifying the execution mode of the information transfer phase. A value must be set in this field when the Transfer command is issued. If any of the following commands are issued during execution of the Transfer command, this field's value must not be changed:

• Set ATN

- Transfer Pause

- Reset ACK/REQ

#### Bit 2: Program Transfer

- 1 ... Data is transferred between the MPU and the data buffer register in SPC.

- 0 ... Data is transferred in the DMA mode in which the SPC signals a transfer request to the external buffer memory.

#### Bit 1: Unused

Bit 1 must always be set to 0.

#### Bit O: Termination Mode

Bit O provides different functions depending on the SPC operation mode. When SPC serves as an INITIATOR, bit O specifies the following operations:

- 1 ... Even after the transfer byte counter reaches 0 during execution of the Transfer command, data transfer is continued if the REQ signal arrives from a TARGET in the same phase. if an output operation is in progress, all 0 bits (with a parity bit set to 1) are transmitted as data. During an input operation, the received data is ignored. But parity is checked if it is enabled (Parity Enable). The above data transfer is referred to as padding transfer, which is effective only when the DATA IN or DATA OUT phase is executed. Padding transfer is executed only within SPC, and a transfer request is not signalled to the external buffer memory even if the DMA transfer mode is specified. Padding transfer is maintained until a TARGET changes the bus phase. In the padding transfer byte counter set to 0, execution of padding transfer is started with the first byte. To carry out an output operation in this case, the TEMP register must be set to X'00' prior to issuance of the Transfer command.

- 0 ... Transfer command execution terminates when the transfer byte counter reaches 0. The Transfer command must be reissued for receiving the next REQ signal from a TARGET.

When SPC serves as a TARGET, bit O specifies the following operations:

- 1 ... If a parity error is detected in the received data during execution of the Transfer command for input, the current transfer sequence is immediately stopped to terminate Transfer command execution.

- 0 ... Even if a parity error is detected in the received data during execution of the Transfer command for input, the current transfer sequence is continued until the transfer byte counter reaches 0.

- 4.3.2 Command Functions

- (1) Bus Release command

When SPC acts as a TARGET role, the Bus Release command instructs a transition to the BUS FREE phase. During execution of the information transfer phase, the Transfer Pause command must be issued to halt the data transfer operation prior to this command. Otherwise, the SCSI bus sequence is not ensured. The Bus Release command may also be used to cancel the Select command waiting for the bus to become free. Note that the Bus Release command is ignored if SPC has already started the ARBITRATION or SELECTION phase.

(2) Select command

The select command requests the SELECTION/RESELECTION phase to be started. It shall be issued only when the SPC is not connected with SCSI. When the SPC receives this command, it carries out the following operation upon detection of the BUS FREE phase is SCSI.

- a. When bit 4 (Arbitration Enable) of the SCTL register is set to 1: After the BUS FREE phase has been detected, SPC executes the ARBITRATION phase to try to obtain bus usage permission. If the SPC has lost the arbitration, the Select command terminates its execution. If the SPC has won the arbitration, SPC executes the SELECTION or RESELECTION phase. The SELECTION phase is executed when bit 0 (I/O Out) of the PCTL register is set to 0, and the RESELECTION phase is executed when it is set to 1.

- b. When bit 4 (Arbitration Enable) of the SCTL register is set to 0: After the BUS FREE phase has been detected, SPC executes the SELECTION phase.

Before this command is issued, the following settings must be made in either of the above cases:

```

a. PCTL register

Specify the phase to be executed at bit 0 (I/O Out).

0 ... SELECTION phase to be executed

1 ... RESELECTION phase to be executed

Note that whenever bit 4 (Arbitration Enable) of the SCTL register is set to 0, the SELECTION phase is executed regardless a value of bit 0 (I/O Out) of the PCTL register.

```

- b. Set ATN command Issue the Set ATN command if it is required to assert an ATN signal at the SELECTION phase.

- c. TEMP register In the TEMP register, specify a value to be sent to the SCSI data bus during execution of the SELECTION/RESELECTION phase.

- d. TCH and TCM registers Specify a response (BSY signal) waiting supervisory time for execution of the SELECTION/RESELECTION phase. The supervisory time T<sub>SL</sub> should be calculated as follows: Assuming that the value of TCH and TCM is N (MSB: TCH, LSB: TCM); When N does not equal 0,  $T_{SL} = (N \times 256 + 15) \times T_{CLF} \times 2$ . When N equals 0,  $T_{SL} = infinite$ . Where,  $T_{CLF}$  is a cycle time of the clock signal supplied to the CLK pin of SPC.

e. TCL register

Specify a period of time ( $T_{WAIT}$ ) from the moment when both BSY and SEL signals become inactive on SCSI upon detection of the BUS FREE phase to the moment when SPC initiates the ARBITRATION/SELECTION phase. Parameters (X'00') to (X'OF') can be specified in the TCL register. The average TWAIT value can be derived using the following equation:

$T_{WAIT} = [(TCL + 6] \times T_{CLF} [(TCL) + 7] \times T_{CLF}]$ Where,

(TCL): A set value in the TCL register.

$T_{CLF}$ : A cycle time of the clock signal supplied to the  $\overline{CLK}$  pin of SPC.

Table 4.3.1 lists the values recommended to be set in the TCL register.

Table 4.3.1 Values recommended to be set in TCL register for use of Select command

| T <sub>CLF</sub> (ns) | TCL                | <sup>T</sup> WAIT (average) (ns) |

|-----------------------|--------------------|----------------------------------|

| 125 - 180             | <sup>(04)</sup> 16 | 1,250 - 1,980                    |

| 140 - 200             | <sup>(03)</sup> 16 | 1,260 - 2,000                    |

In ARBITRATION phase execution by the Select command, the bus device identifier (ID) which is sent to the SCSI data bus is the value specified in the BDID register. The following equation can be used to obtain the period of time (TARB) required from the moment when the arbitration is started (BSY signal assertion) to the moment when the bus usage priority is examined: