# Static RAM Products

1990

DATA BOOK

LAND REALEMENTS

TRACERCURA

Static RAM Products

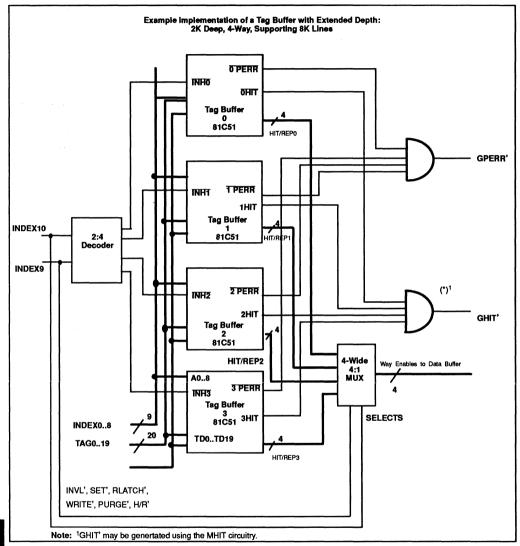

| 1  | High-Speed CMOS SRAMs                |

|----|--------------------------------------|

| 2  | High-Speed BiCMOS SRAMs              |

| 3  | Low-Power CMOS SRAMs                 |

| 4  | Application-Specific SRAMs           |

| 5  | High Temperature Range SRAM Products |

| 6  | CMOS SRAM Modules                    |

| 7  | Quality and Reliability              |

| 8  | Ordering Information                 |

| 9  | Sales Information                    |

| 10 | Appendices – Design Information      |

|    |                                      |

# FUJITSU

# Static RAM Products

1990 Data Book

Fujitsu Limited Tokyo, Japan

Fujitsu Microelectronics, Inc. San Jose, California, U.S.A.

Fujitsu Mikroelectronik GmbH Frankfurt, F.R. Germany

Fujitsu Microelectronics Asia PTE Limited Singapore

Copyright© 1990 Fujitsu Microelectronics, Inc., San Jose, California

All Rights Reserved.

Circuit diagrams using Fujitsu products are included to illustrate typical semiconductor applications. Information sufficient for construction purposes may not be shown.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu Microelectronics, Inc. assumes no responsibility for inaccuracies.

The information conveyed in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited, its subsidiaries, or Fujitsu Microelectronics, Inc.

Fujitsu Microelectronics, Inc. reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu Microelectronics, Inc.

This document is published by the Publications Department, Fujitsu Microelectronics, Inc., 3545 North First Street, San Jose, California, U.S.A. 95134–1804; U.S.A.

Printed in the U.S.A.

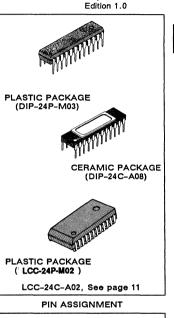

Edition 1.0

### Contents and Alphanumeric Product List

### SRAM Products

| Introduction — SRAM Products            | s                                                                                   |

|-----------------------------------------|-------------------------------------------------------------------------------------|

| Section 1 – High-Speed CMOS             | <b>SRAMs</b> — At a Glance 1–1                                                      |

| MB81C67-35/-45/-55                      | CMOS 16384 x 1 bit SRAM 1–3                                                         |

| MB81C68A-25/-30/-35                     | CMOS 4096 x 4 bits SRAM 1–15                                                        |

| MB81C69A-25/-30/-35                     | CMOS 4096 x 4 bits SRAM 1-27                                                        |

| MB81C71A-25/-35                         | CMOS 65536 x 1 bit SRAM 1–39                                                        |

| MB81C74-25/-35                          | CMOS 16384 x 4 bits SRAM 1-51                                                       |

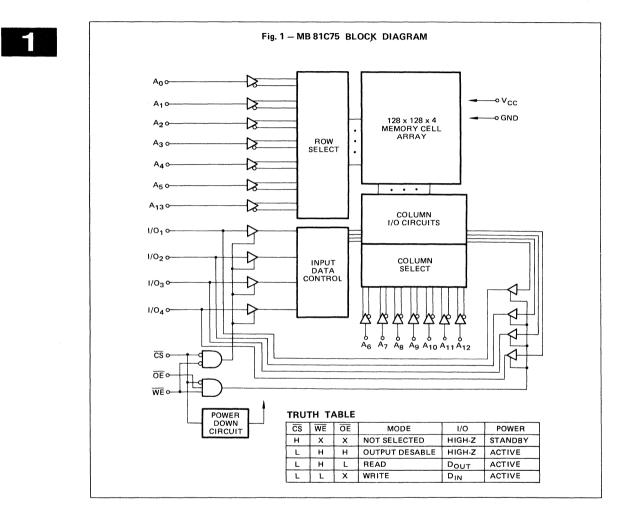

| MB81C75-25/-35                          | CMOS 16384 x 4 bits SRAM 1-61                                                       |

| MB81C78A-35/-45                         | CMOS 8192 x 8 bits SRAM 1–73                                                        |

| MB81C79A-35/-45                         | CMOS 8192 x 9 bits SRAM 1-87                                                        |

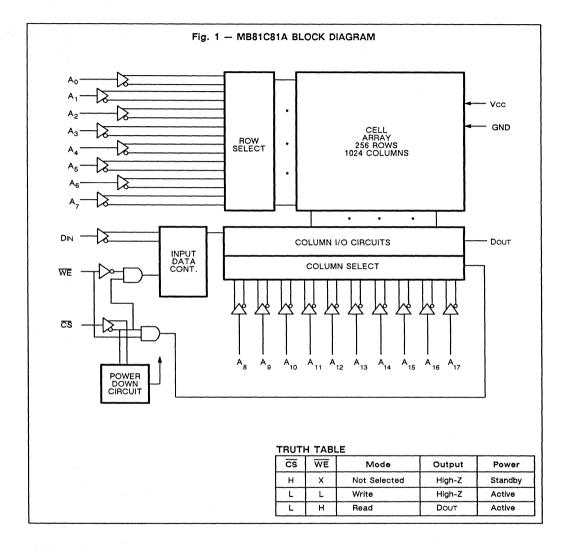

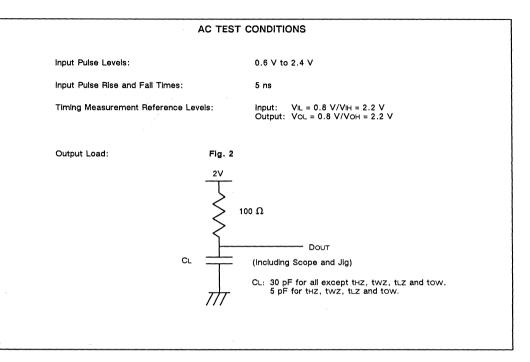

| MB81C81A-35/-45                         | CMOS 262144 x 1 bit SRAM 1–101                                                      |

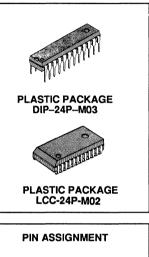

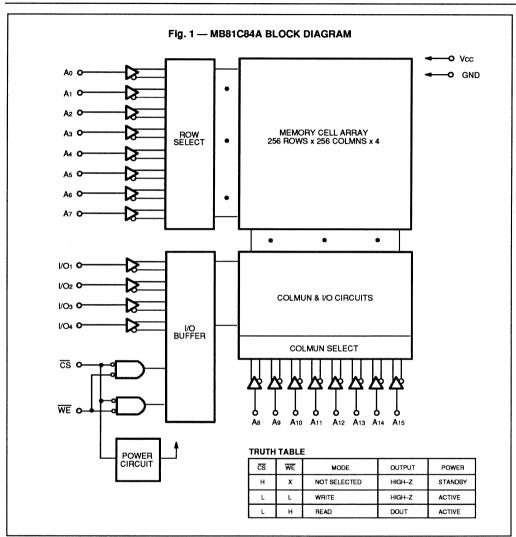

| MB81C84A-35/-45                         | CMOS 65536 x 4 bits SRAM 1–113                                                      |

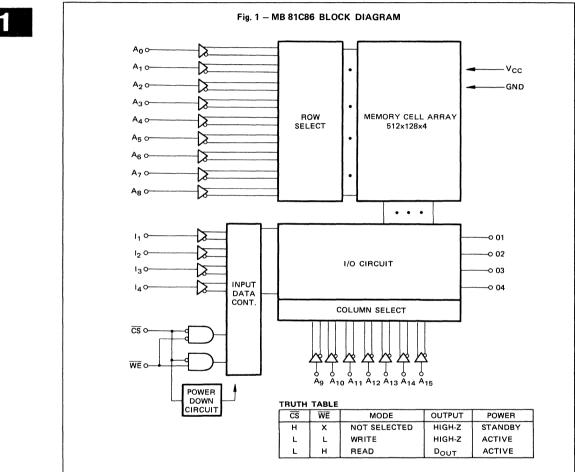

| MB81C86-55/-70                          | CMOS 65536 x 4 bits SRAM 1–123                                                      |

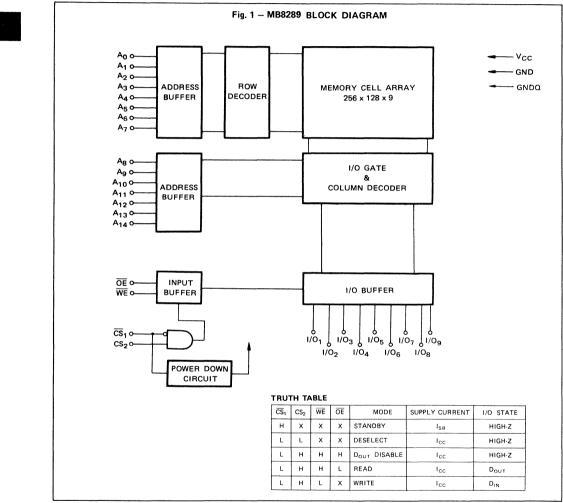

| MB8289-25/-35                           | CMOS 32768 x 9 bits SRAM 1–131                                                      |

| Section 2 – High-Speed BiCMC            | S SRAMs — At a Glance                                                               |

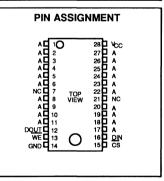

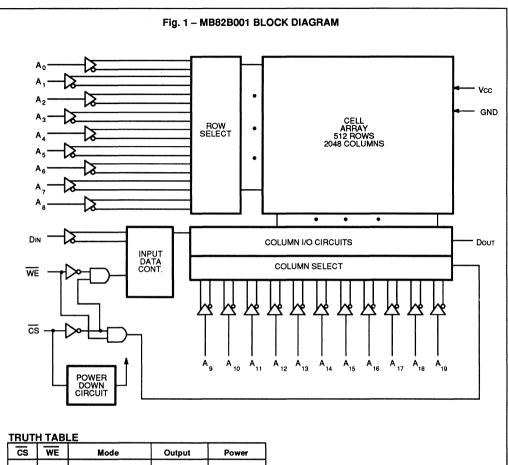

| MB82B001-25/-35                         | BiCMOS 1048576 x 1 bit SRAM 2–3                                                     |

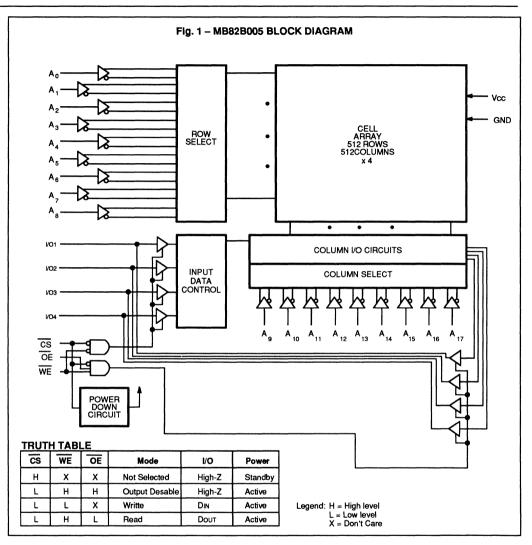

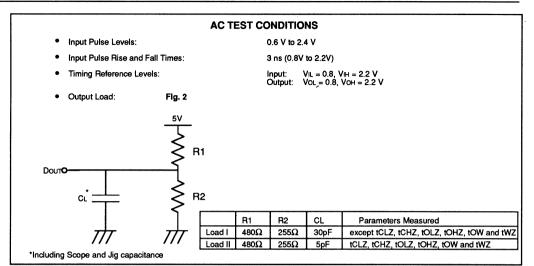

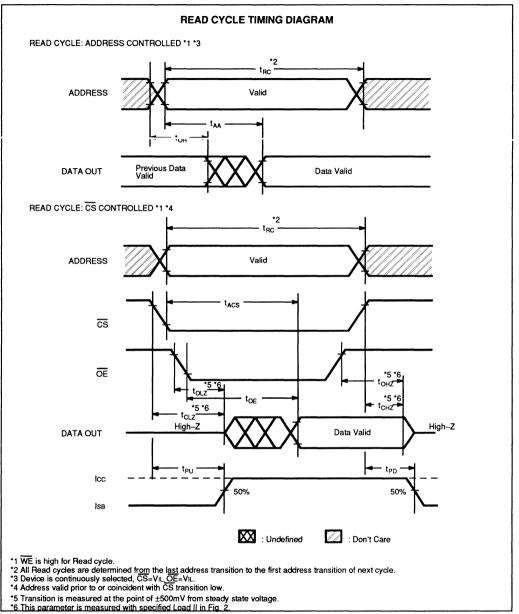

| MB82B005-25/-35                         | BiCMOS 262144 x 4 bits SRAM 2-11                                                    |

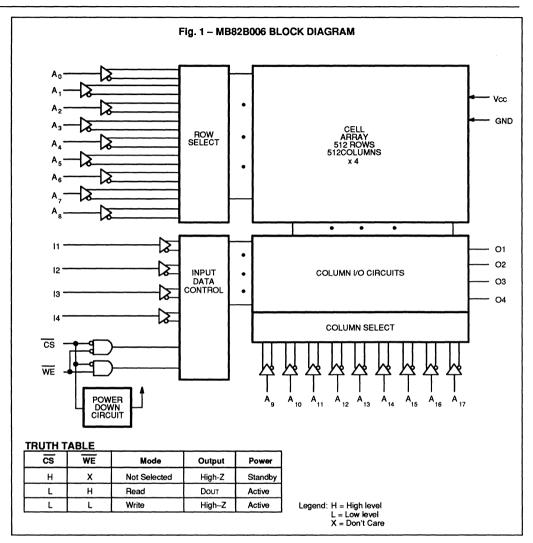

| MB82B006-25/-35                         | BiCMOS 262144 x 4 bits SRAM 2–19                                                    |

| MB82B71-15/-20                          | BiCMOS 65536 x 1 bit SRAM 2–27                                                      |

| MB82B74-15/-20                          | BiCMOS 16384 x 4 bits SRAM 2–37                                                     |

| MB82B75-15/-20                          | BiCMOS 16384 x 4 bits SRAM                                                          |

| MB82B79-15/-20                          | BiCMOS 8192 x 9 bits SRAM 2-55                                                      |

| MB82B81-15/-20                          | BiCMOS 262144 x 1 bit SRAM 2-65                                                     |

| MB82B84-15/-20                          | BiCMOS 65536 x 4 bits SRAM 2–73                                                     |

| Section 3 – Low-Power CMOS              | SRAMs — At a Glance                                                                 |

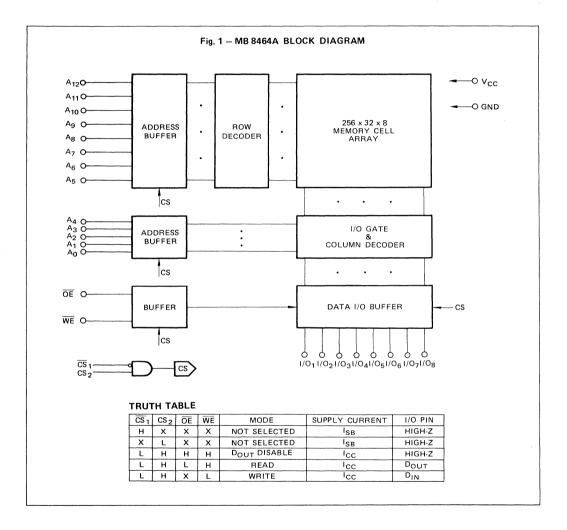

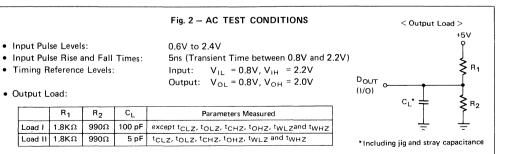

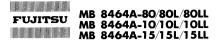

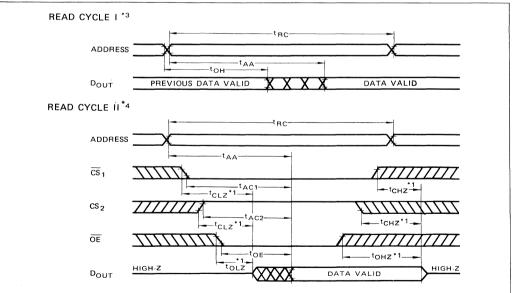

| MB8464A -80/L/LL                        | CMOS 8192 x 8 bits SRAM                                                             |

| -10/L/LL, -15/L/L<br>MB84256   -10/L/LL | CMOS 32768 x 8 bits SRAM 3–15                                                       |

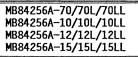

| -12/L/LL, -15/L/L<br>MB84256A-70/L/LL   | L CMOS 32768 x 8 bits SRAM 3–25                                                     |

| -10/L/LL, -15/L/L                       | L                                                                                   |

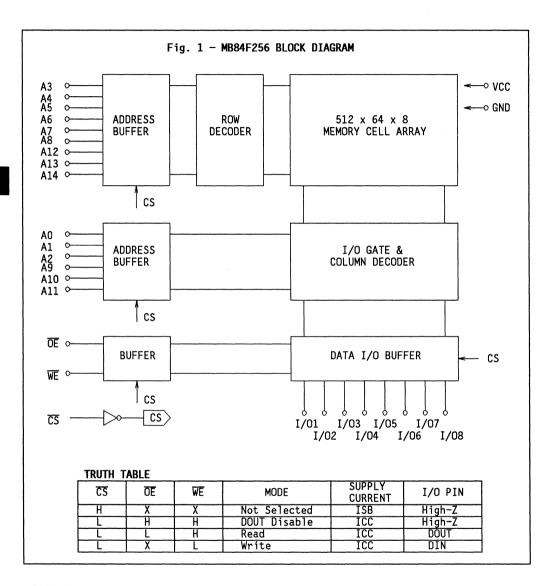

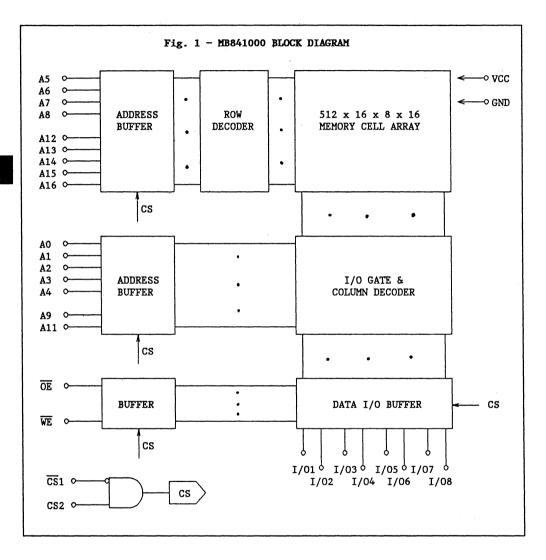

| MB84F256-25<br>MB841000 -80/-10/-12/L   | CMOS 32768 x 8 bits SRAM 3-35<br>CMOS 131072 x 8 bits SRAM with Data Retention 3-47 |

|                                         |                                                                                     |

### Contents and Alphanumeric Product List (Continued)

### SRAM PRODUCTS

| Section 4 – Application Specific         | <b>SRAMs</b> — <i>At a Glance</i> 4–1            |

|------------------------------------------|--------------------------------------------------|

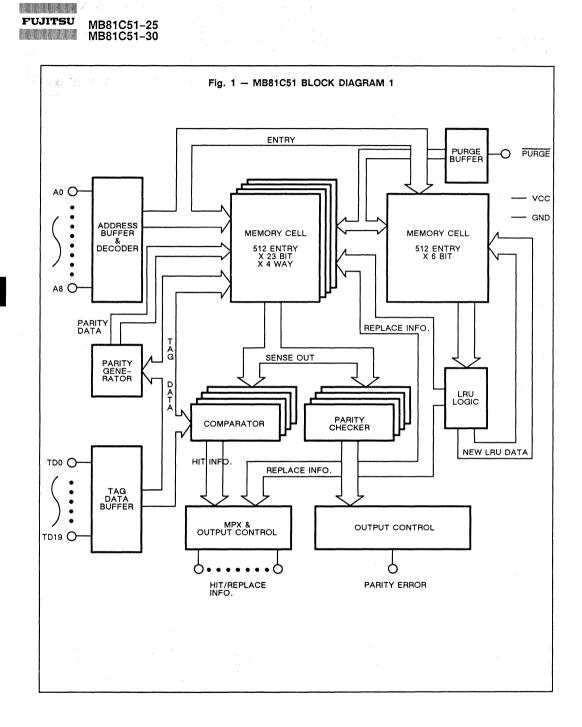

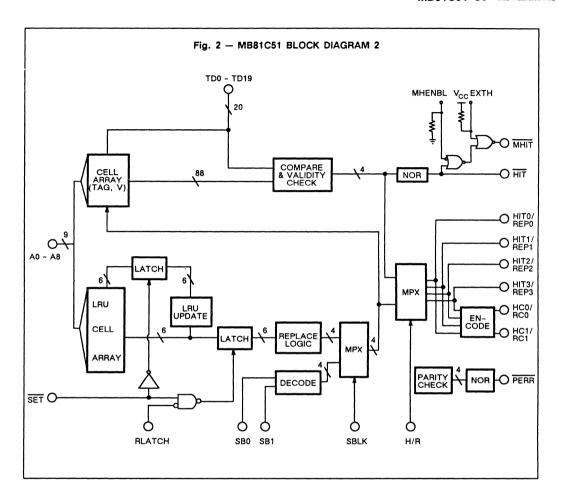

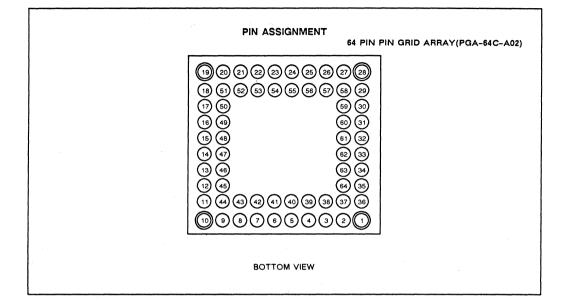

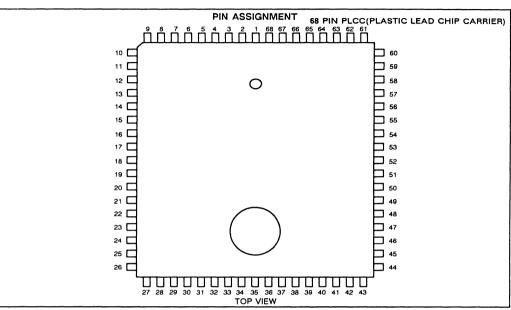

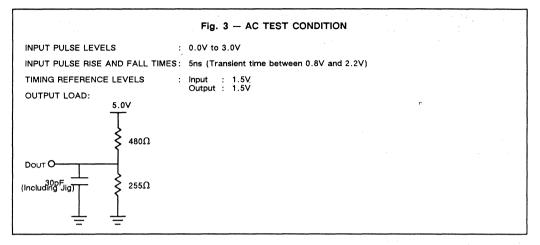

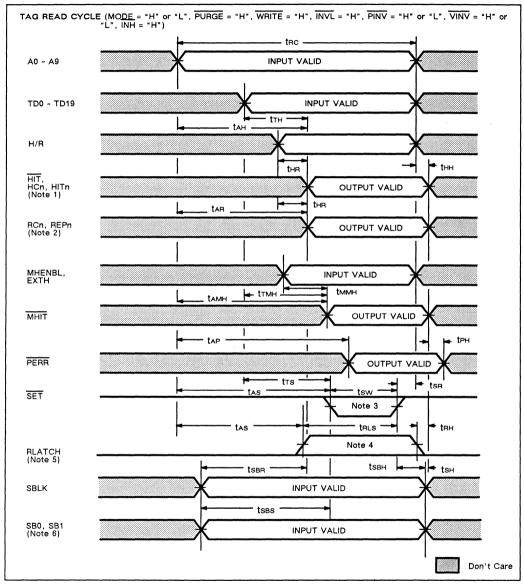

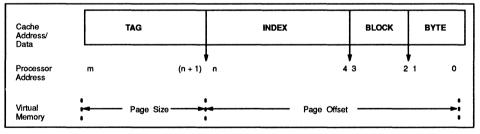

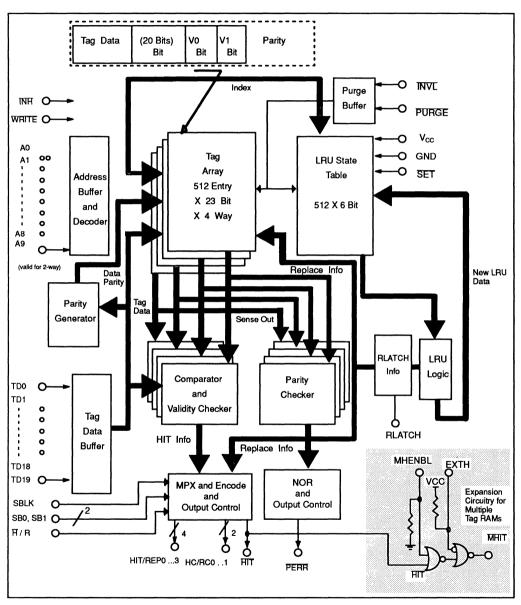

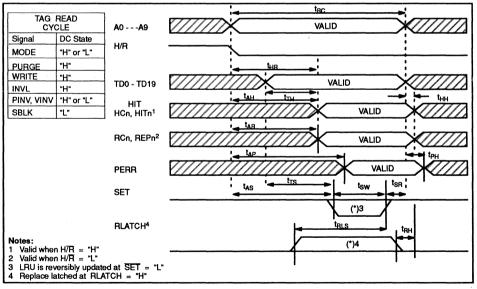

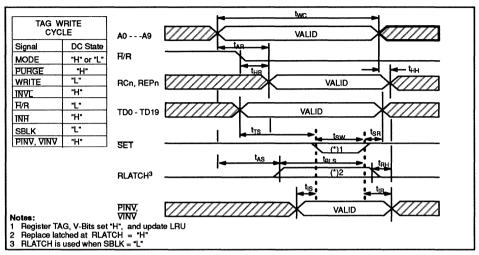

| MB81C51-25/-30                           | CMOS 512 x 4/1024 x 2 TAG RAM 4-3                |

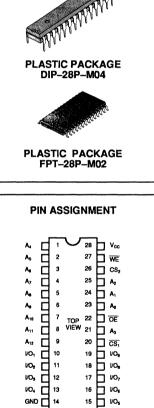

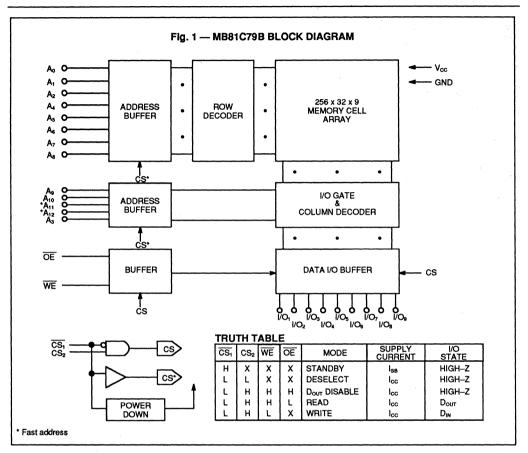

| MB81C79B-35/-45                          | CMOS 8192 x 9 bits SRAM 4–19                     |

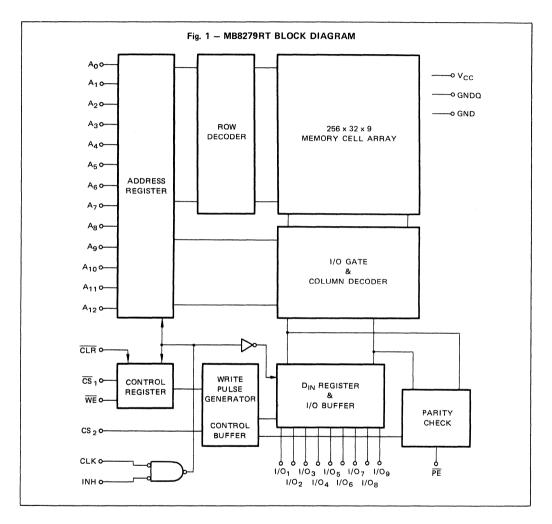

| MB8279RT-20/-25                          | CMOS 8192 x 9 bits STRAM 4-31                    |

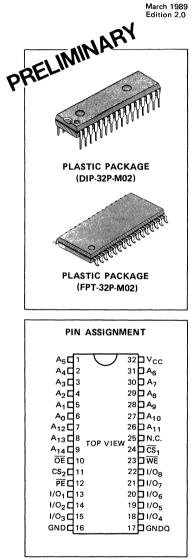

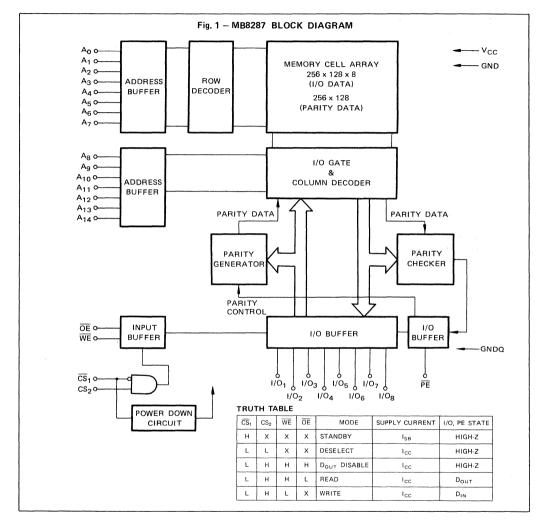

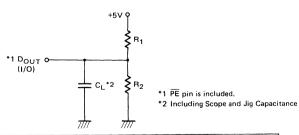

| MB8287-25/-35                            | CMOS 32768 x 8 bits SRAM with PE 4–43            |

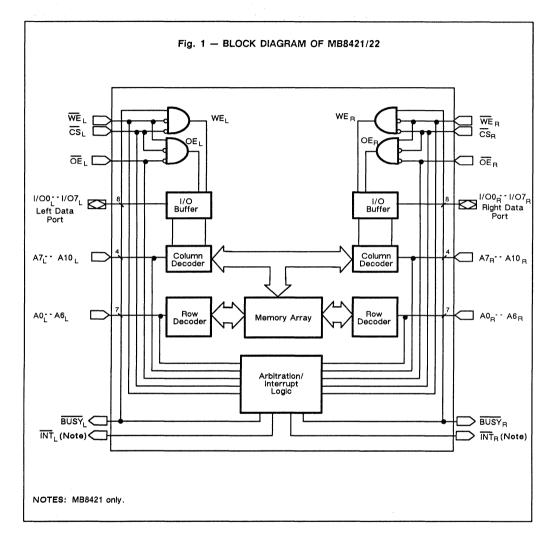

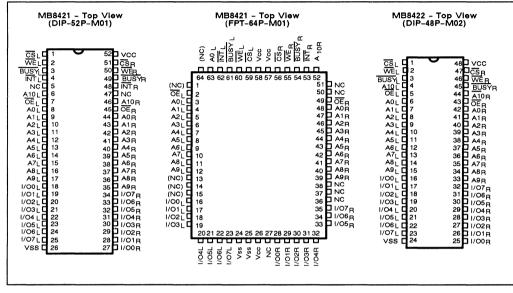

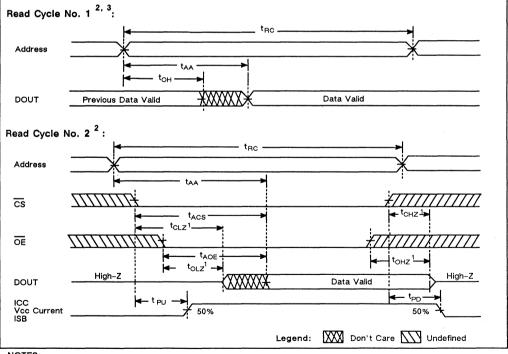

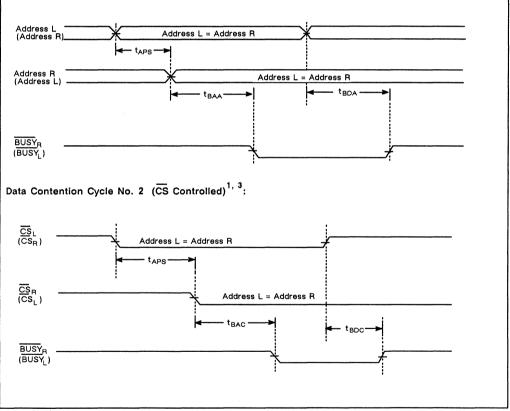

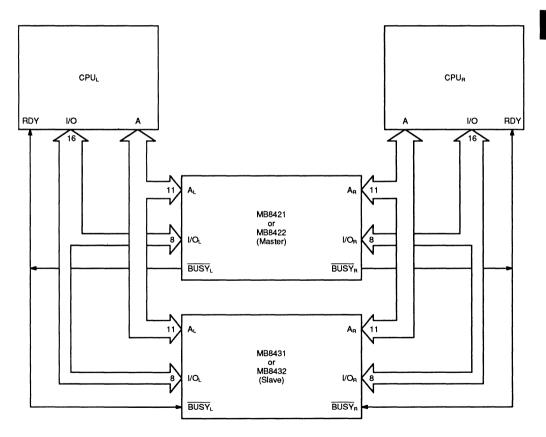

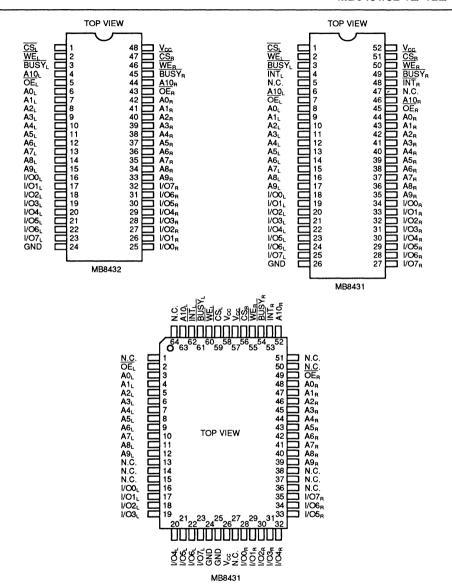

| MB8421-90/-12/L                          | CMOS 2048 x 8 bits SRAM 4–55                     |

| MB8422-90/-12/L                          |                                                  |

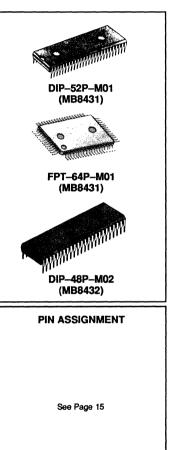

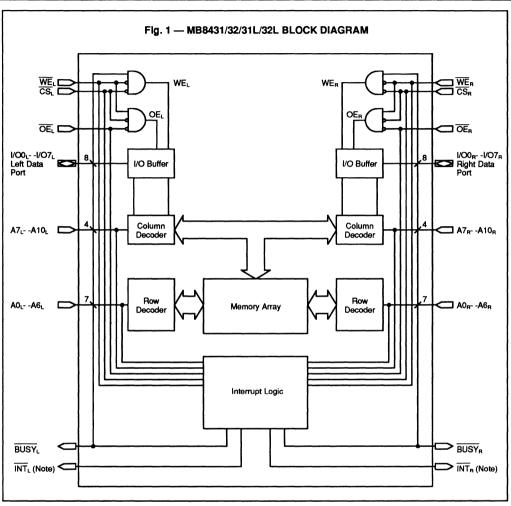

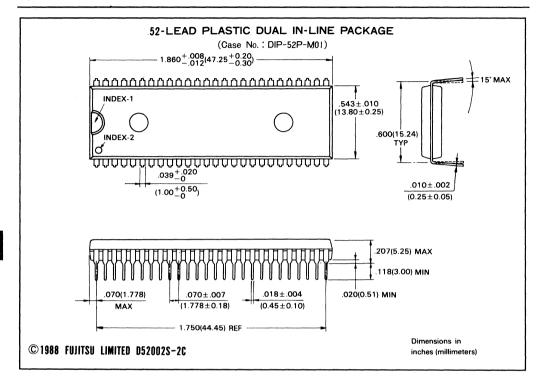

| MB8431-90/-12/L/LL<br>MB8432-90/-12/L/LL | CMOS 2048 x 8 bits SRAM 4–69                     |

|                                          |                                                  |

| Section 5 – Wide Temperature R           | ange SRAM Products — At a Glance                 |

| MB81C68A-45W                             | CMOS 4096 x 4 bits SRAM 5-3                      |

| MB81C78A-45W                             | CMOS 8192 x 8 bits SRAM 5–11                     |

| MB81C79A-45W                             | CMOS 8192 x 9 bits SRAM 5-23                     |

| MB8464A-10W/-15W                         | CMOS 8192 x 8 bits SRAM 5–35                     |

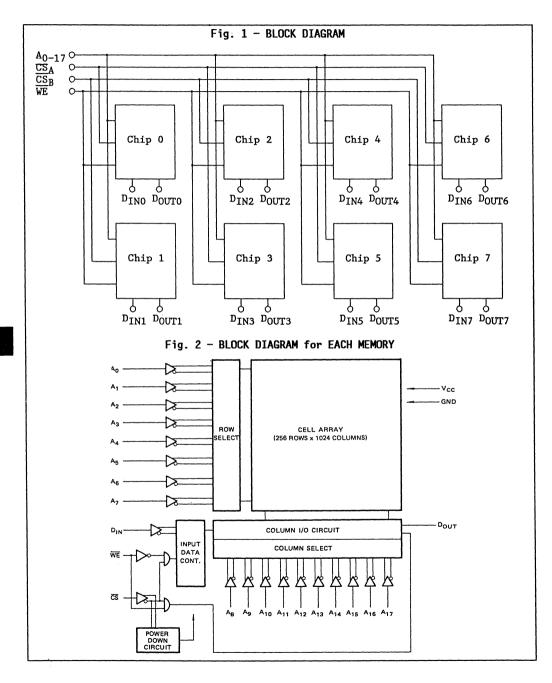

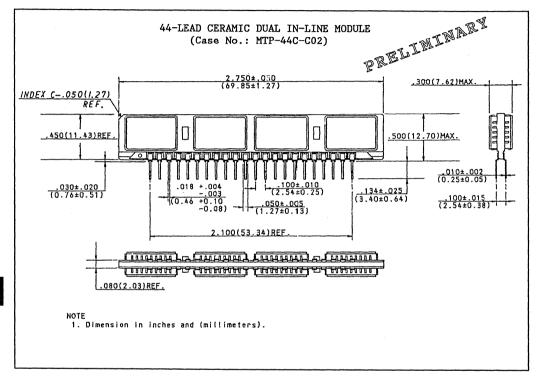

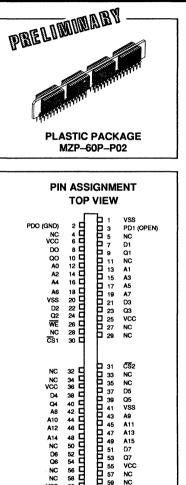

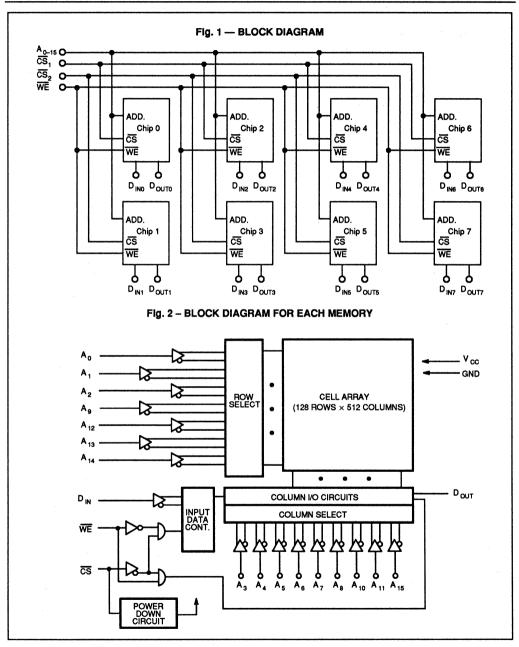

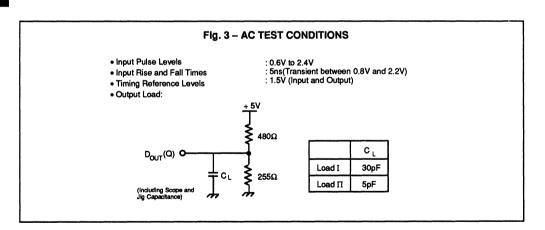

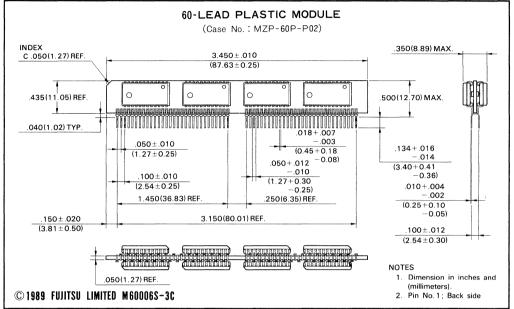

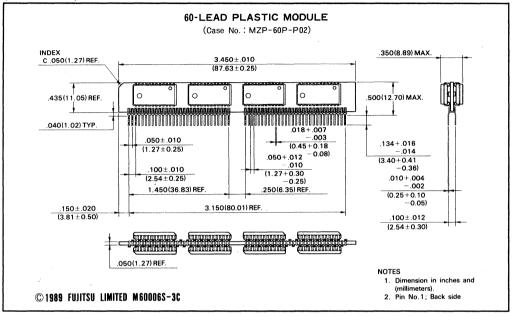

| Section 6 – CMOS SRAM Module             | es — At a Glance                                 |

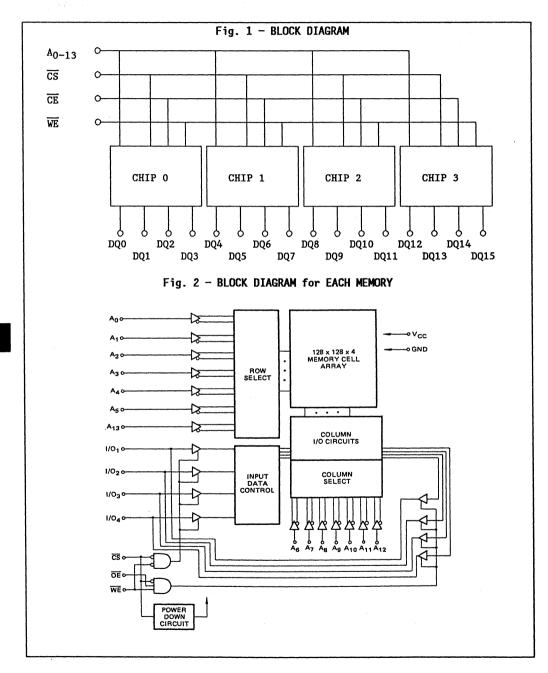

| MB85402-30/-40                           | CMOS 16384 x 16 bits SRAM Module                 |

| MB85403-40/-50                           | CMOS 262144 x 8 bits SRAM Module 6-11            |

| MB85410-30/-40                           | CMOS 65536 x 8 bits High Speed SRAM Module 6-19  |

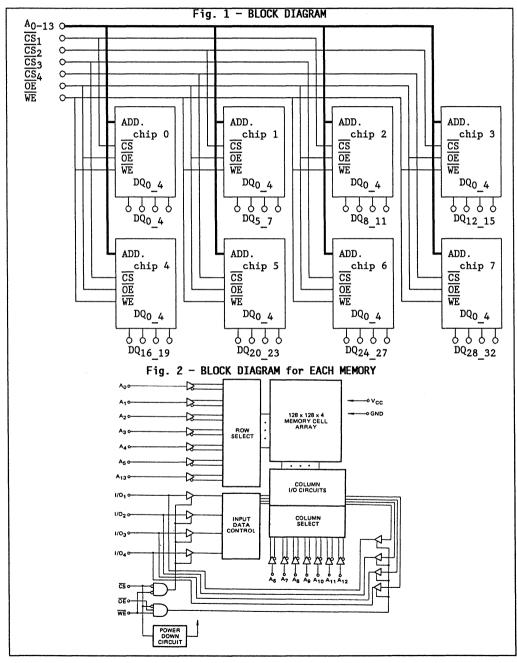

| MB85414-30/-40                           | CMOS 16384 x 32 bits High Speed SRAM Module 6-27 |

| MB85420-40/-50                           | CMOS 252144 x 8 bits High Speed SRAM Module 6–35 |

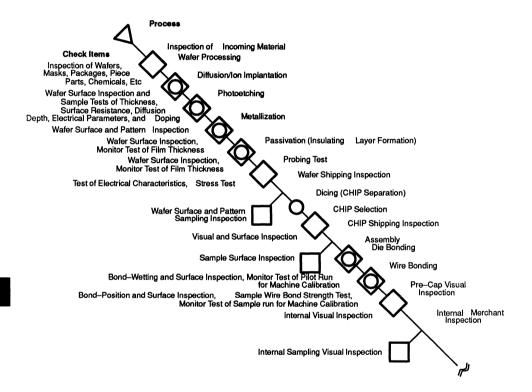

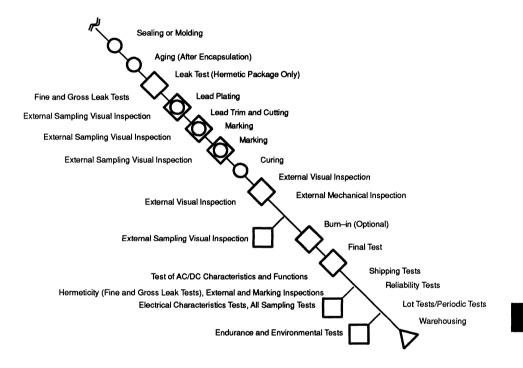

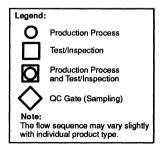

| Section 7 – Quality and Reliabili        | <b>ty</b> — At a Glance                          |

| Quality Control at Fujitsu               |                                                  |

|                                          | Fujitsu                                          |

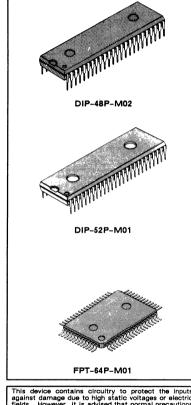

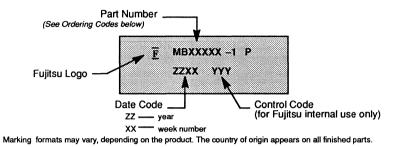

| Section 8 – Ordering Information         | n — At a Glance                                  |

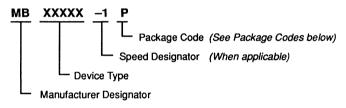

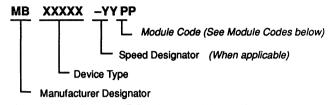

| IC Product Marking                       |                                                  |

|                                          | ber)                                             |

|                                          |                                                  |

| IC Module Ordering Code (Pa              | art Number)                                      |

| IC Module Package Codes .                |                                                  |

| Wide Temperature IC Orderin              | ng Code (Part Number) 8–5                        |

| Wide Temperature IC Packag               | e Codes                                          |

|                                          |                                                  |

### Contents and Alphanumeric Product List (Continued)

### SRAM PRODUCTS

| Section 9 – | Sales Information — At a Glance                     |

|-------------|-----------------------------------------------------|

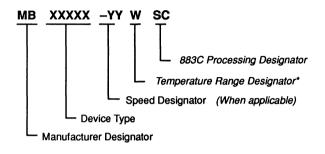

| Int         | roduction to Fujitsu                                |

| Int         | egrated Circuits Corporate Headquarters – Worldwide |

| FM          | II Sales Offices for North and South America        |

| FM          | II Representatives – USA                            |

| FM          | II Representatives - Canada                         |

| FM          | II Representatives – Mexico                         |

| FM          | II Representatives – Puerto Rico                    |

| FM          | II Distributors – USA                               |

| FM          | II Distributors – Canada                            |

| FN          | IG Sales Offices for Europe                         |

| FM          | IG Distributors – Europe                            |

| FM          | A Sales Offices for Asia and Australia              |

| FM          | A Representatives – Asia                            |

| FM          | A Distributors – Asia and Austraila                 |

|             |                                                     |

| Section 10 – Ap | ppendices – Design Information                                     | 10–1          |

|-----------------|--------------------------------------------------------------------|---------------|

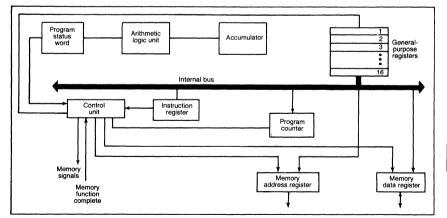

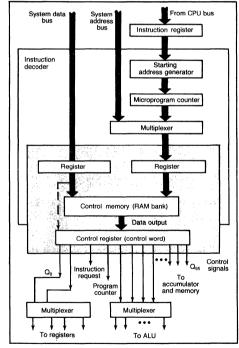

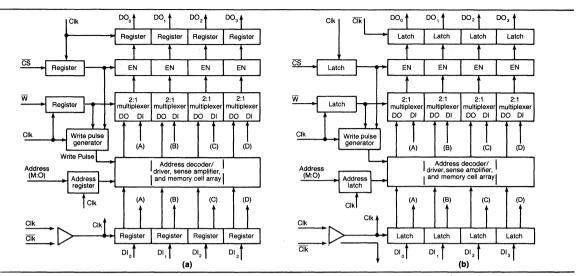

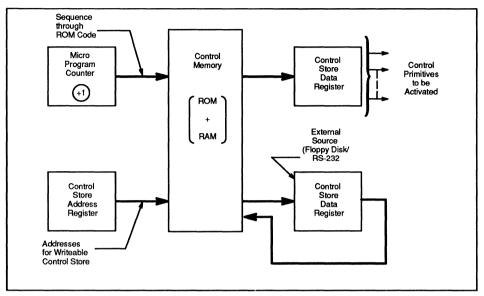

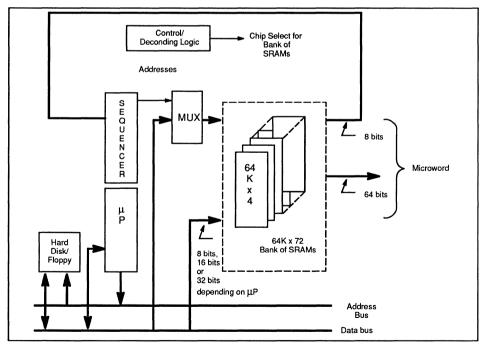

| Append          | dix 1. Design Applications. Internally timed RAMs build fast write | eable         |

|                 | control stores                                                     | 10–3          |

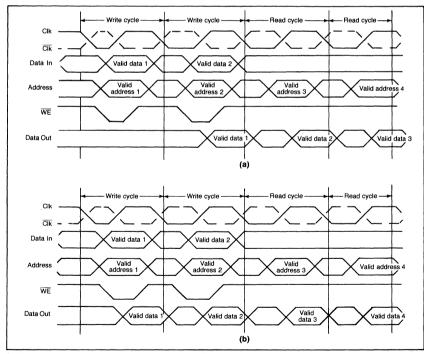

| Append          | dix 2. Application Note: Separate Data Inputs and Outputs SRAMs    | s Provide New |

|                 | Architectural Solutions for System Designers                       |               |

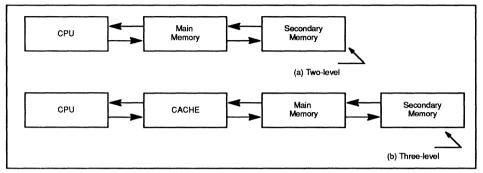

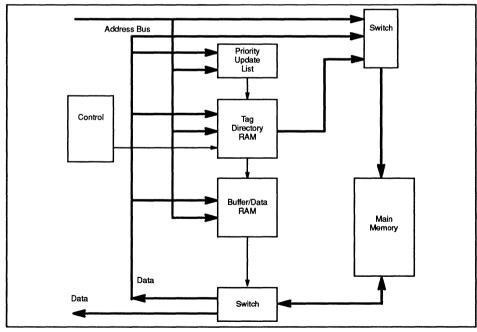

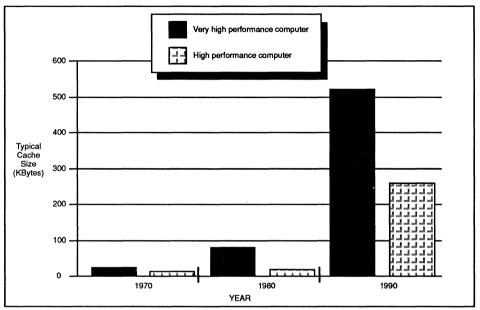

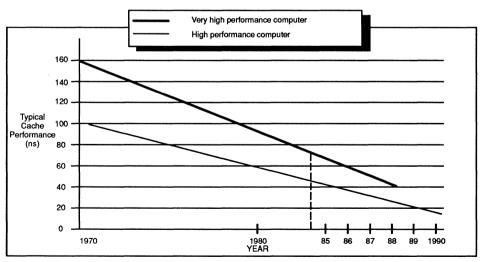

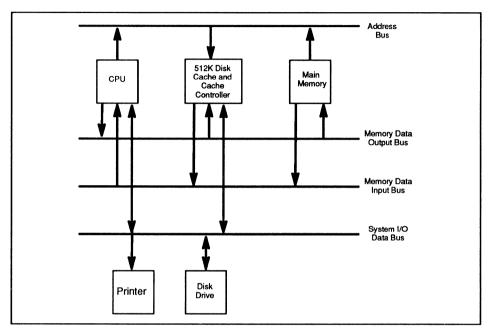

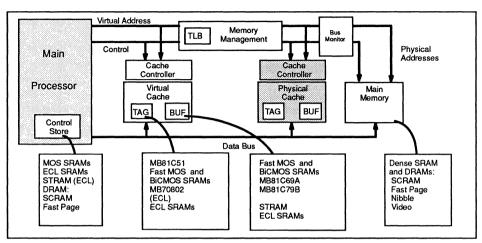

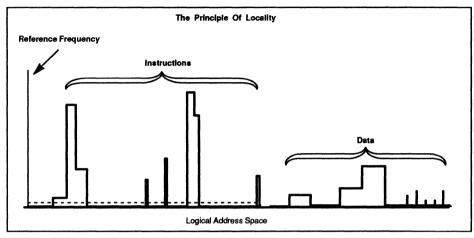

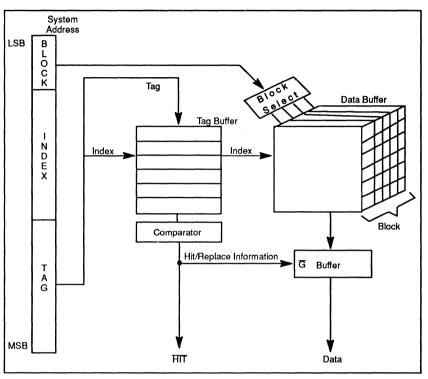

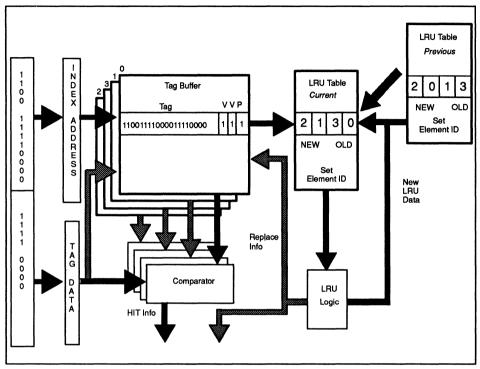

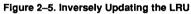

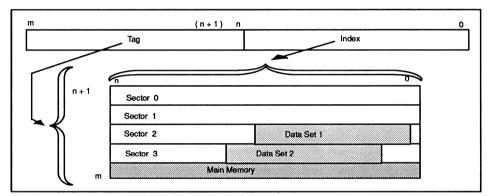

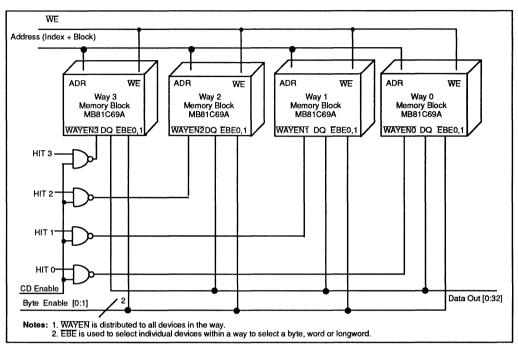

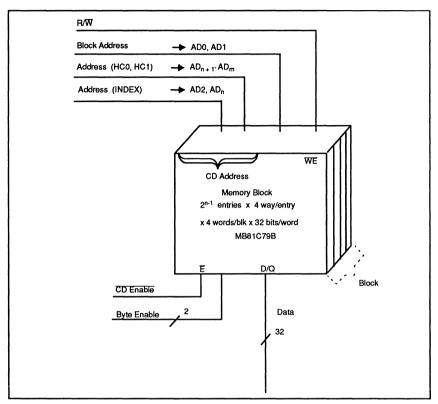

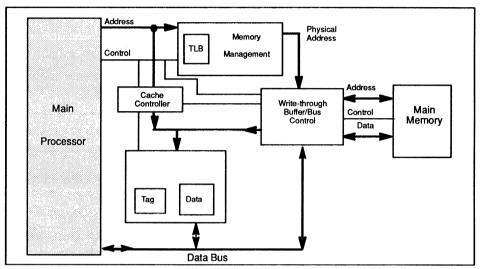

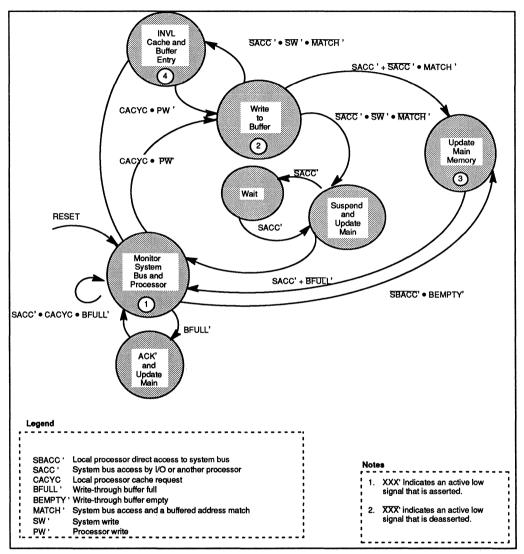

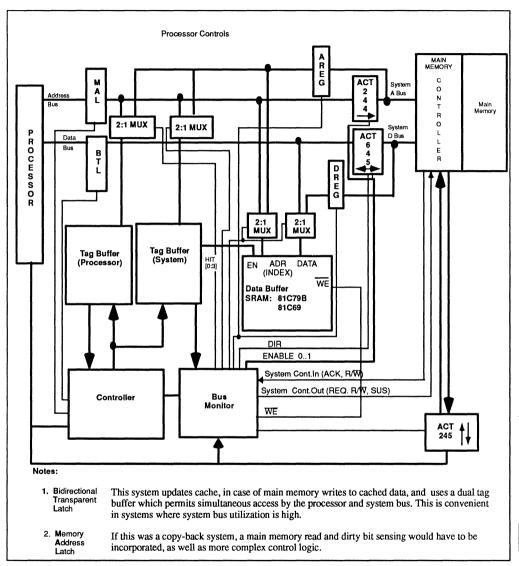

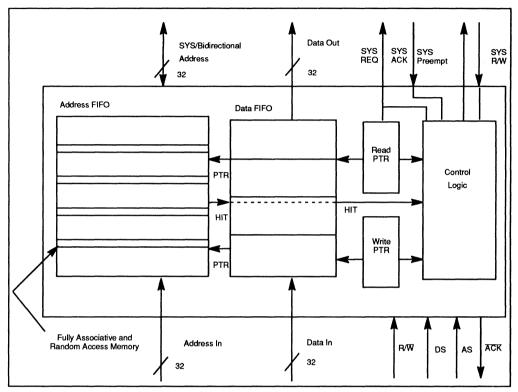

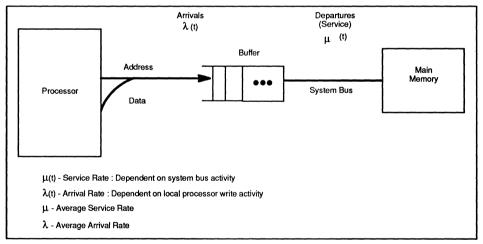

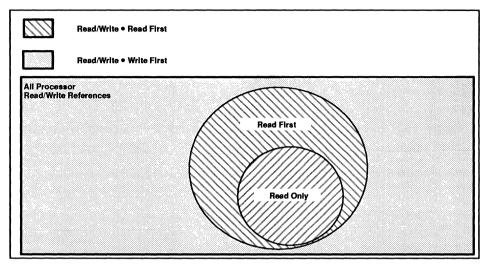

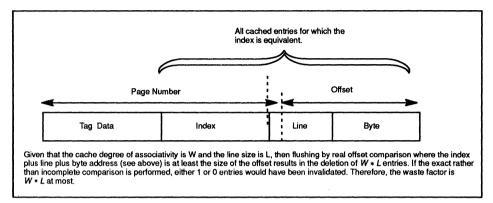

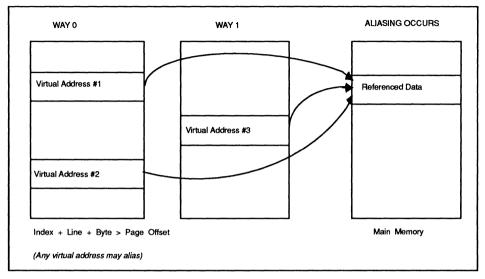

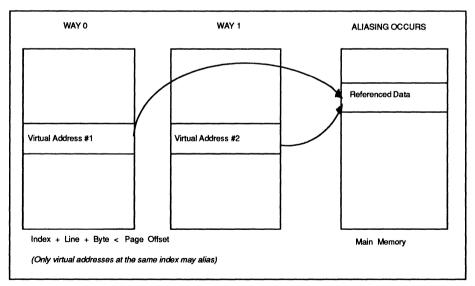

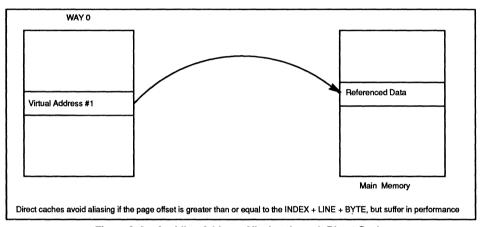

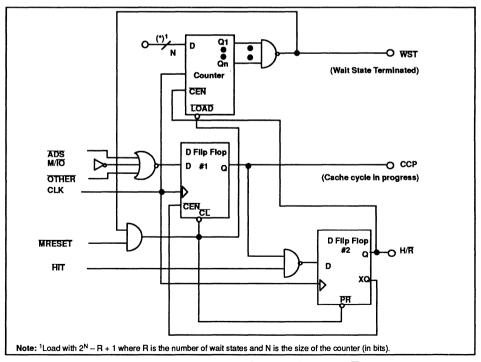

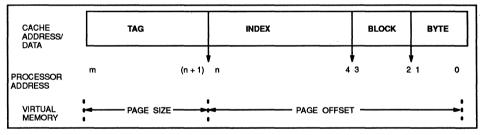

| Append          | dix 3. Application Handbook: The Effective Design of CMOS-ba       | sed           |

|                 | Caches in CISC- and RISC-based Architectures                       |               |

### Contents and Alphanumeric Product List (Continued)

### SRAM PRODUCTS

### Alphanumeric List of Fujitsu Part Numbers

| MB81C51-25/-30 4–3       |

|--------------------------|

| MB81C67-35/-45/-55 1–3   |

| MB81C68A-25/-30/-35 1-15 |

| MB81C68A-45W 5–3         |

| MB81C69A-25/-30/-35 1–27 |

| MB81C71A-25/-35 1–39     |

| MB81C74-25/-35 1–51      |

| MB81C75-25/-35 1–61      |

| MB81C78A-35/-45 1–73     |

| MB81C78A-45W 5-11        |

| MB81C79A-35/-45 1-87     |

| MB81C79A-45W 5–23        |

| MB81C79B-35/-45 4–19     |

| MB81C81A-35/-45 1–101    |

| MB81C84A-35/-45 1–113    |

| MB81C86-55/-70 1–123     |

| MB8279RT-20/-25 4-31     |

| MB8287-25/-35 4-43       |

| MB8289-25/-35 1–131      |

| MB82B001-25/-35 2–3      |

| MB82B005-25/-35 2–11     |

| MB82B006-25/-35 2–19     |

| MB82B71-15/-20           |

|                          |

| MB82B74-15/-20              |

|-----------------------------|

| MB82B75-15/-20              |

| MB82B79-15/-20              |

| MB82B81-15/-20              |

| MB82B84-15/-20              |

| MB8421-90/-12/L             |

| MB8422-90/-12/L 4–55        |

| MB8431-90/-12/L/LL 4–69     |

| MB8432-90/-12/L/LL          |

| MB8464A-10W/-15W            |

| MB8464A-80/L/LL, -10/L/LL,  |

|                             |

| -15/L/LL 3–3                |

| MB84256A-70/L/LL, -10/L/LL, |

| -12/L/LL, -15/L/LL 3–25     |

| MB84256 -10/L/LL, -12/L/LL, |

| -15/L/LL 3–15               |

| MB84F256-25                 |

| MB841000-80/-10/-12/L 3-47  |

| MB85402-30/-40 6–3          |

| MB85403-40/-50 6-11         |

| MB85410-30/-40              |

| MB85414-30/-40              |

|                             |

| MB85420-40/-50 6–35         |

### Introduction

Page

ix Fujitsu's Static RAM Products

\_\_\_\_\_

#### Fujitsu's Static RAM Products

#### Introduction

Fujitsu manufactures a wide range of integrated circuits that includes linear products, microprocessors, telecommunications circuits, ASICs, high-speed ECL logic, power components (consisting of both discrete transistors and transistor arrays), and both static and dynamic RAMs.

The static RAM product line offers devices for use in a wide range of applications. These memories are manufactured to meet the high standard of quality and reliability that is found in all Fujitsu products.

This data book includes product information on the following SRAM products:

#### High-speed CMOS SRAMs

Fujitsu's high-speed CMOS SRAMs offer the advantages of low power dissipation, low cost, and high performance. Features include TTL compatibility and a separate chip-select pin that simplifies multipackage systems design.

#### High-speed BiCMOS SRAMs

Advanced BiCMOS technology adds ultra-fast access times to CMOS low power dissipation in Fujitsu's new family of static RAMs. Most devices feature an automatic power-down mode and are generally available in small outline packages with J-leads (SOJ).

#### Low-speed CMOS SRAMs

Our low-power CMOS SRAMs are ideally suited for use in microprocessor systems and other applications where fast access time and ease of use are required. The memories use asynchronous circuitry and may be maintained in any state for an indefinite period of time.

#### **Application-Specific SRAMs**

To address the system needs of cache memory chips, Fujitsu's application-specific memory line includes both cache TAG RAM and high-speed static RAM, as well as port RAMs for multiprocessor systems.

### Fujitsu's Static RAM Products (Continued)

#### Wide Temperature Range SRAMs

For applications requiring MIL-STD-883 processing, Fujitsu offers a selection of high-performance, TTL-compatible CMOS static RAM products. All of these devices operate in the "W" temperature range, generally 55° to 125°C. (See product specifications for specific temperature range.)

#### **CMOS SRAM Modules**

x

Fujitsu manufactures a complete family of reliable CMOS static RAM memory modules for those applications requiring high density and large memory storage capability. Fujitsu's family of memory modules are pin-compatible with JEDEC standards.

### ----- Section 1

1

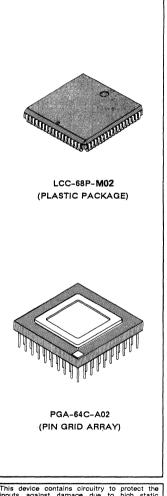

| Page  | Device                    | Maximum<br>Access<br>Time (ns) | Capacity                      | Packag<br>Options          |                               |                        |

|-------|---------------------------|--------------------------------|-------------------------------|----------------------------|-------------------------------|------------------------|

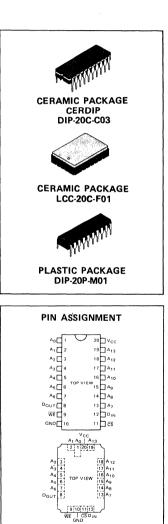

| 1–3   | MB81C67-35<br>-45<br>-55  | 35<br>45<br>55                 | 16384 bits<br>(16384w x 1b)   | 20-pin<br>20-pin<br>20-pad | Plastic<br>Ceramic<br>Ceramic | DIP<br>DIP<br>LCC      |

| 1–15  | MB81C68A-25<br>-30<br>-35 | 25<br>30<br>35                 | 16384 bits<br>(4096w x 4b)    | 20-pin<br>20-pin           | Plastic<br>Ceramic            | dip, Zip<br>Dip        |

| 1–27  | MB81C69A-25<br>-30<br>-35 | 25<br>30<br>35                 | 16384 bits<br>(4096w x 4b)    | 20-pin<br>20-pin           | Plastic<br>Ceramic            | DIP<br>DIP             |

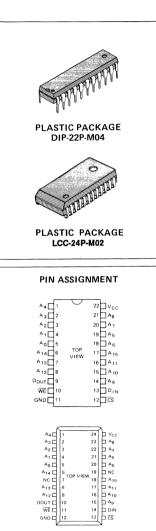

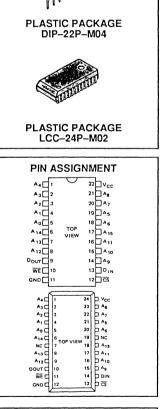

| 1–39  | MB81C71A-25<br>-35        | 25<br>35                       | 65536 bits<br>(65536w x 1b)   | 22-pin<br>24-pin<br>22-pad | Plastic<br>Plastic<br>Ceramic | DIP<br>LCC<br>LCC      |

| 1–51  | MB81C74-25<br>-35         | 25<br>35                       | 65536 bits<br>(16384w x 4b)   | 22-pin<br>22-pad           | Plastic<br>Ceramic            | DIP<br>LCC             |

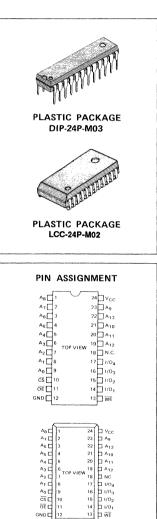

| 1–61  | MB81C75-25<br>-35         | 25<br>35                       | 65536 bits<br>(16384w x 4b)   | 24-pin<br>24-pin           | Plastic<br>Plastic            | DIP<br>LCC             |

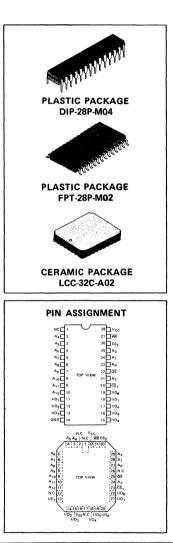

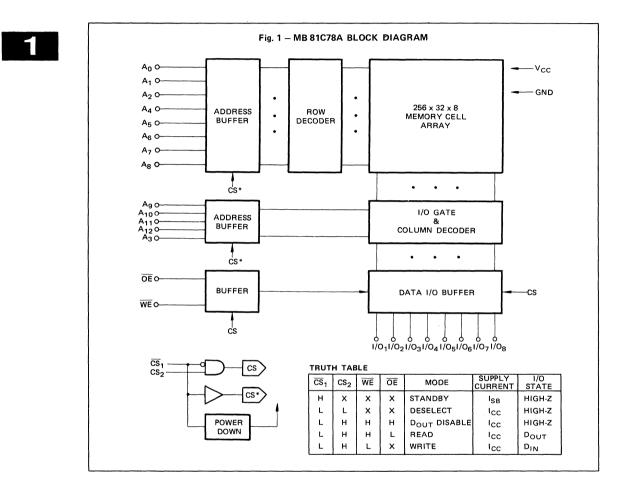

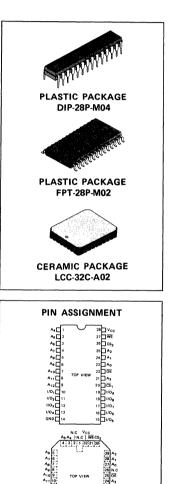

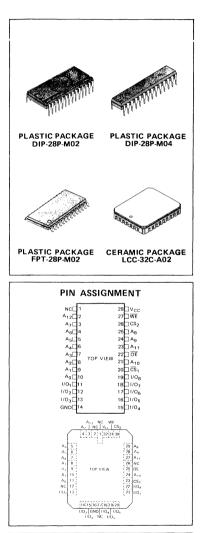

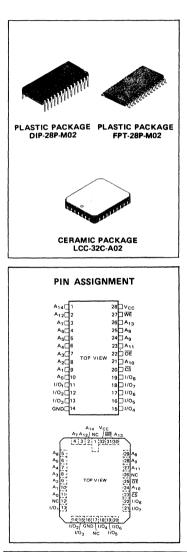

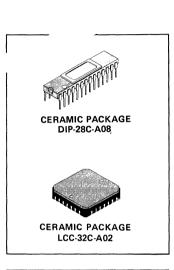

| 173   | MB81C78A-35<br>-45        | 35<br>45                       | 65536 bits<br>(8192w x 8b)    | 28-pin<br>32-pad           | Plastic<br>Ceramic            | DIP, FPT<br>LCC        |

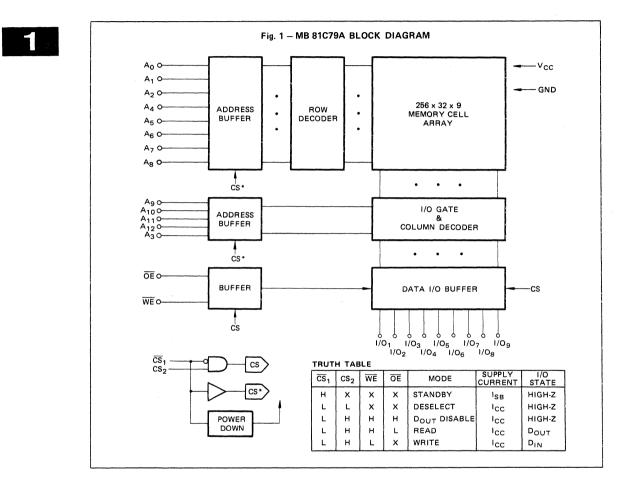

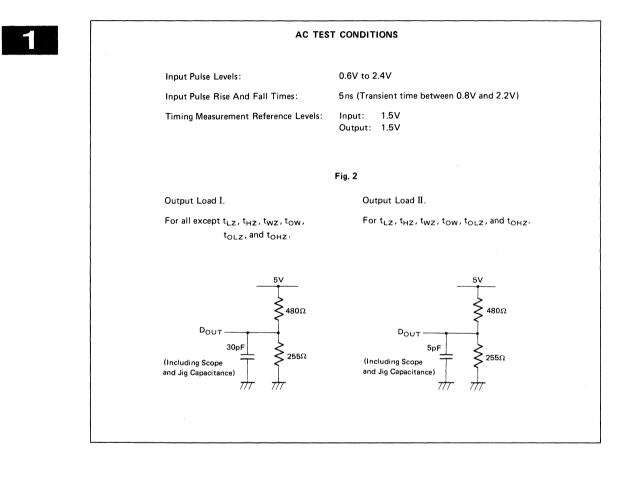

| 1–87  | MB81C79A-35<br>-45        | 35<br>45                       | 73728 bits<br>(8192w x 9b)    | 28-pin<br>32-pad           | Plastic<br>Ceramic            | DIP, FPT<br>LCC        |

| 1–101 | MB81C81A-35<br>-45        | 35<br>45                       | 262144 bits<br>(262144w x 1b) | 24-pin<br>24-pin<br>24-pad | Plastic<br>Ceramic<br>Ceramic | DIP, LCC<br>DIP<br>LCC |

| 1–113 | MB81C84A-35<br>-45        | 35<br>45                       | 262144 bits<br>(65536w x 4b)  | 24-pin                     | Plastic                       | DIP, LCC               |

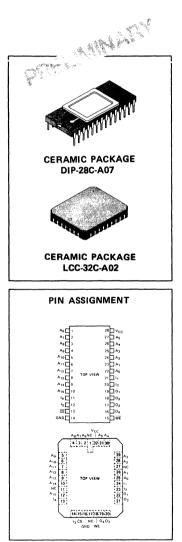

| 1–123 | MB81C86-55<br>-70         | 55<br>70                       | 262144 bits<br>(65536w x 4b)  | 28-pin<br>32-pad           | Ceramic<br>Ceramic            | DIP<br>LCC             |

| 1–131 | MB8289-25<br>-35          | 25<br>35                       | 262144 bits<br>(32768w x 9b)  | 32-pin                     | Plastic                       | DIP, FPT               |

### High-Speed CMOS SRAMs — At a Glance

### MB 81C67-35 MB 81C67-45 MB 81C67-55

March 1986 Edition 2.0

#### 16,384 WORDS ×1 BIT HIGH SPEED CMOS STATIC RANDOM ACCESS MEMORY

CMOS 16384-BIT STATIC RANDOM ACCESS MEMORY

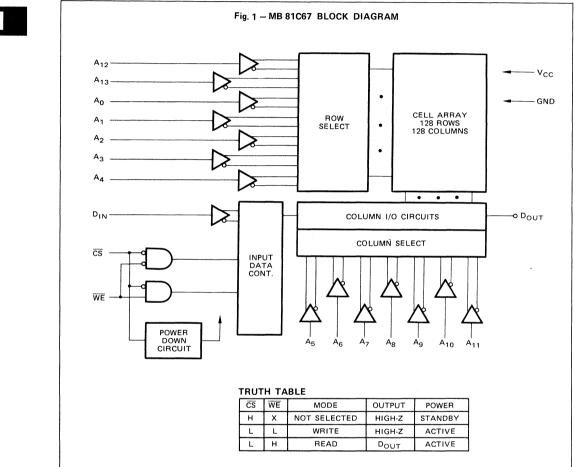

The Fujitsu MB 81C67 is 16,384 words x 1 bit static random access memory fabricated with a CMOS silicon gate process. All pins are TTL compatible and a single 5 volts power supply is required.

For ease of use, chip select ( $\overline{CS}$ ) permits the selection of an individual package when outputs are OR-tied, and automatically power down the MB 81C67. All devices offer the advantages of low power dissipation, low cost, and high performance.

- Organization: 16,384 words x 1 bit

- Static operation: No clocks or refresh required

- Fast access time: 35 ns max. (MB 81C67-35) 45 ns max. (MB 81C67-45)

- 45 ns max. (MB 81C67-45) 55 ns max. (MB 81C67-55)

- Single +5 V supply, ±10% tolerance

- Single 10 V supply, 210% totela

Separate data input and output

- TTL compatible inputs and output

- Three-state output with OR-tie capability

- Chip select for simplified memory expansion, automatic power down

- All inputs and output have protection against static charge

- Standard 20-pin DIP package (Suffix: CZ, Suffix: P)

- Standard 20-pad Leadless Chip Carrier (Suffix: TV)

- Pin compatible with Fujitsu MB 8167A

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating                                           |                | Symbol Value      |              | Unit |

|--------------------------------------------------|----------------|-------------------|--------------|------|

| Supply Voltage                                   | Supply Voltage |                   | -0.5 to +7.0 | V    |

| Input Voltage on any pin<br>with respect to GND  |                | V <sub>IN</sub>   | -3.5 to +7.0 | v    |

| Output Voltage on any pin<br>with respect to GND |                | V <sub>out</sub>  | -0.5 to +7.0 | v    |

| Output Current                                   |                | lout              | ±50          | mA   |

| Power Dissipation                                |                | PD                | 1.2          | W    |

| Temperature under Bias                           |                | T <sub>BIAS</sub> | -10 to +85   | °C   |

| Storage                                          | Ceramic        | T <sub>STG</sub>  | -65 to +150  | °c   |

| Temperature                                      | Plastic        | 'STG              | -45 to +125  | J    |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

|         | MB | 81C67-35 |

|---------|----|----------|

| FUJITSU | MB | 81C67-45 |

|         | MB | 81C67-55 |

### CAPACITANCE (T<sub>A</sub> = 25°C, f = 1 MHz)

| Parameter                                                  | Symbol           | Тур | Max | Unit |

|------------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (V <sub>IN</sub> = 0 V)                  | C <sub>IN</sub>  |     | 5   | pF   |

| $\overline{\text{CS}}$ Capacitance (V <sub>CS</sub> = 0 V) | C <sub>CS</sub>  |     | 7   | pF   |

| Output Capacitance (V <sub>OUT</sub> = 0 V)                | C <sub>OUT</sub> |     | 8   | pF   |

| MB | 81C67-35 |         |

|----|----------|---------|

| MB | 81C67-45 | FUJITSU |

| MB | 81C67-55 |         |

### **RECOMMENDED OPERATING CONDITIONS**

(Referenced to GND)

| Parameter           | Symbol          | Min   | Тур | Max | Unit |

|---------------------|-----------------|-------|-----|-----|------|

| Supply Voltage      | V <sub>cc</sub> | 4.5   | 5.0 | 5.5 | V    |

| Input Low Voltage   | VIL             | -3.0* |     | 0.8 | V    |

| Input High Voltage  | V <sub>1H</sub> | 2.2   |     | 6.0 | V    |

| Ambient Temperature | T <sub>A</sub>  | 0     |     | 70  | °C   |

\*-3.0V Min. for pulse width less than 20ns. ( $V_{1L}$  Min = -1.0 V at DC level)

### **DC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

| Parameter                   | Test Condition                                                                                                                                       | Symbol           | Min  | Тур | Max | Unit |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|-----|------|

| Input Leakage<br>Current    | $V_{IN} = 0 V$ to $V_{CC}$                                                                                                                           | I <sub>LI</sub>  | -2.0 |     | 2.0 | μΑ   |

| Output Leakage<br>Current   | $\overline{CS} = V_{IH},$ $V_{OUT} = 0 V \text{ to } V_{CC}$                                                                                         | ILO              | -2.0 |     | 2.0 | μΑ   |

| Active Supply<br>Current    | $\overline{CS} = V_{IL}, I_{OUT} = 0 \text{ mA}$ $V_{IN} = V_{IL} \text{ or } V_{IH}$                                                                | I <sub>CC1</sub> |      | 25  | 40  | mA   |

| Operating Supply<br>Current | $\overline{CS} = V_{IL}, I_{OUT} = 0 \text{ mA}$<br>Cycle = Min, C <sub>L</sub> = 0 pF                                                               | I <sub>CC2</sub> |      | 35  | 60  | mA   |

| Standby Supply<br>Current   | $\label{eq:constraint} \begin{split} \overline{CS} &\geq V_{CC} - 0.2 \ V \\ V_{IN} &\geq V_{CC} - 0.2 \ V \ or \\ V_{IN} &\leq 0.2 \ V \end{split}$ | I <sub>SB1</sub> |      | 2   | 15  | mA   |

| Standby Supply<br>Current   | $\overline{CS} = V_{1H}$                                                                                                                             | I <sub>SB2</sub> |      | 15  | 25  | mA   |

| Output Low<br>Voltage       | I <sub>OL</sub> ≈ 16 mA                                                                                                                              | V <sub>OL</sub>  |      |     | 0.4 | V    |

| Output High<br>Voltage      | I <sub>OH</sub> = -4 mA                                                                                                                              | V <sub>OH</sub>  | 2.4  |     |     | V    |

|         | MB | 81C67-35 |

|---------|----|----------|

| FUJITSU | MB | 81C67-45 |

|         | MB | 81C67-55 |

### **AC CHARACTERISTICS**

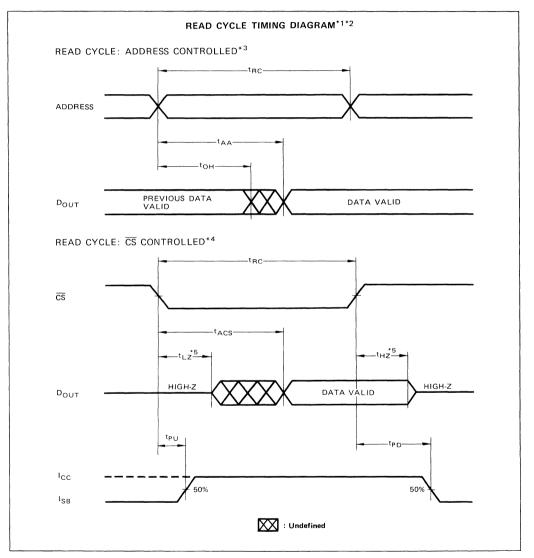

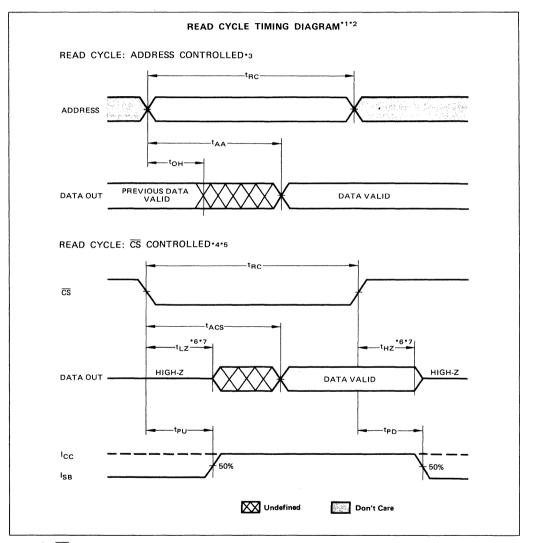

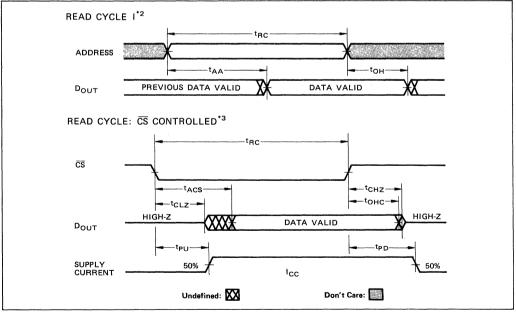

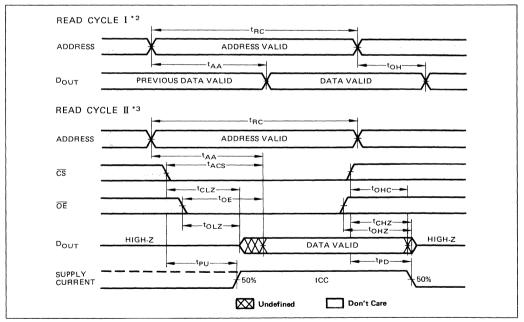

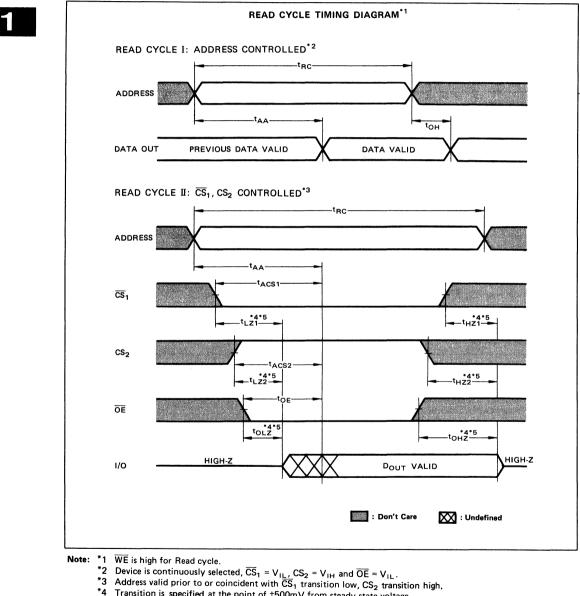

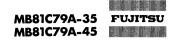

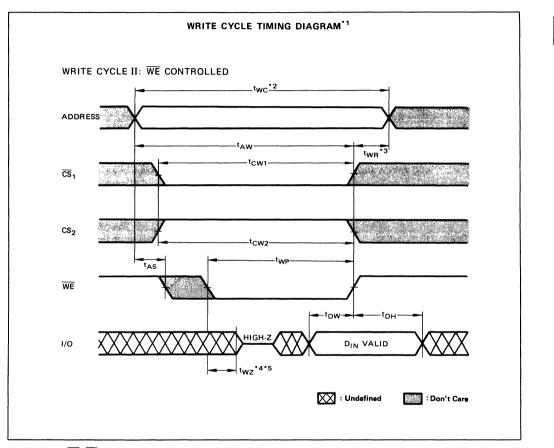

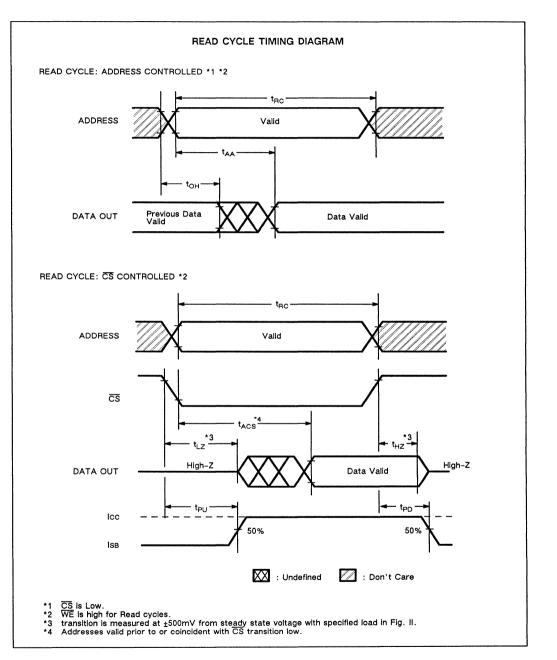

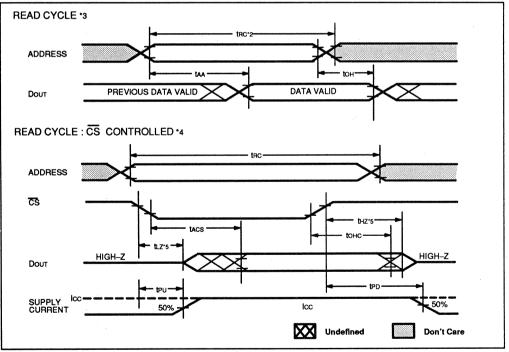

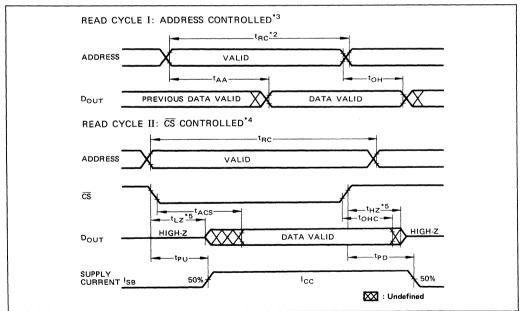

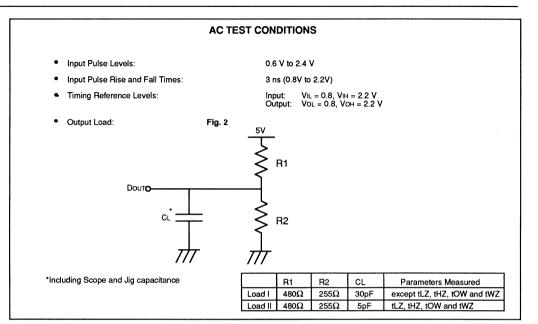

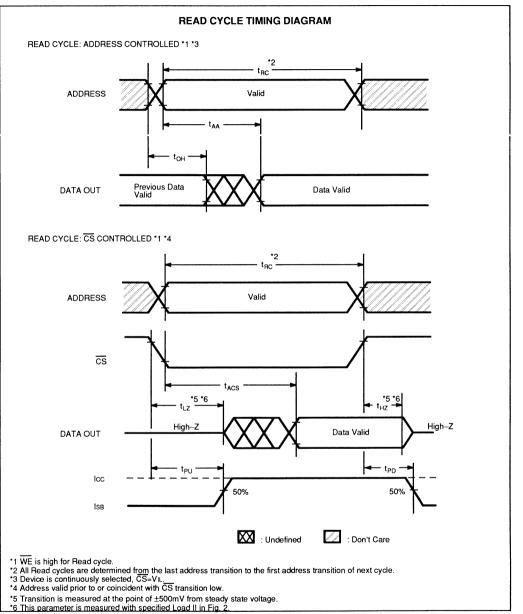

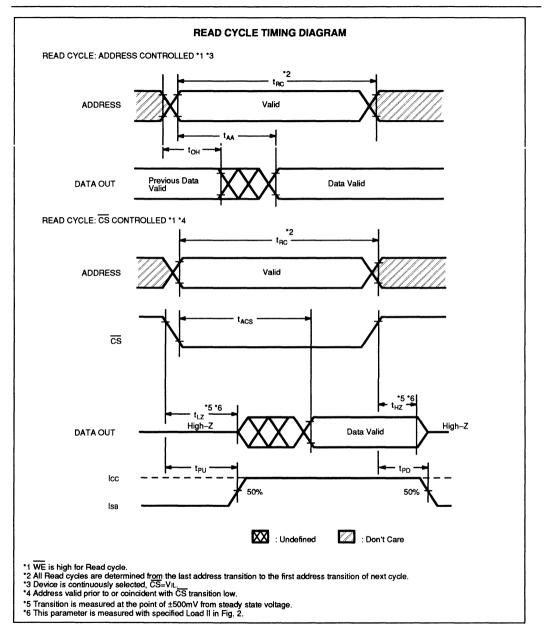

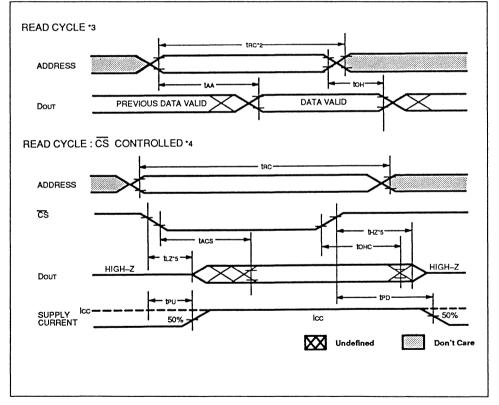

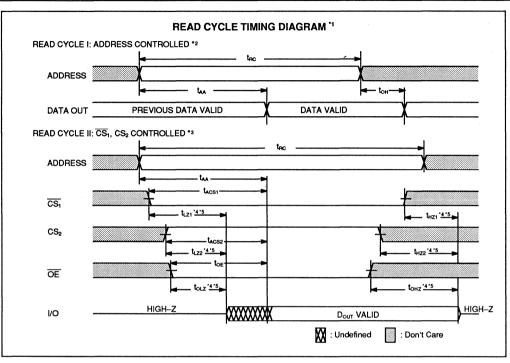

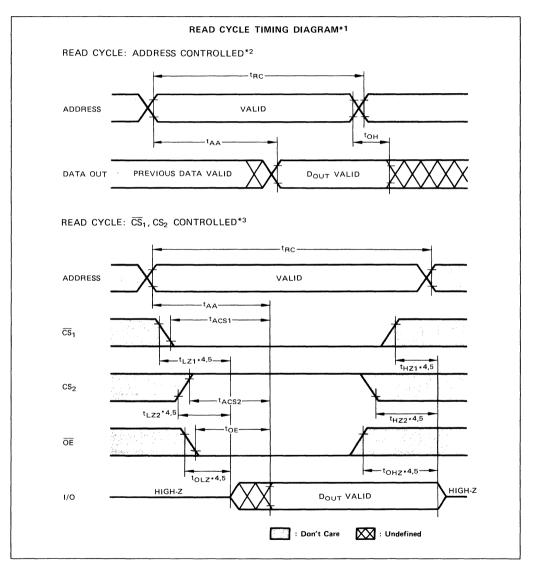

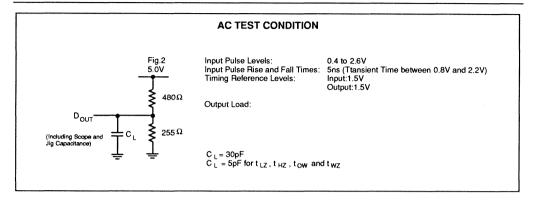

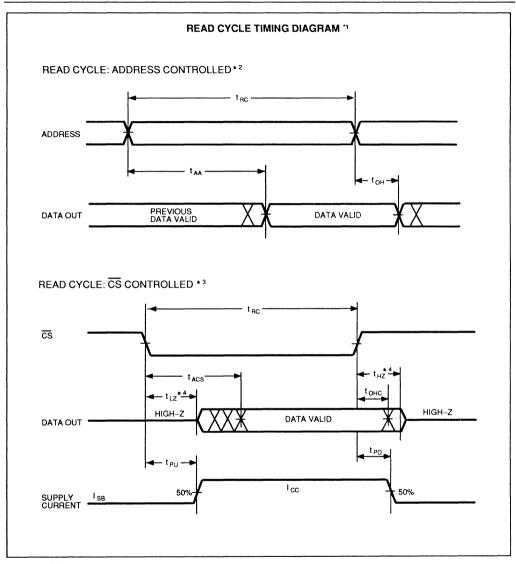

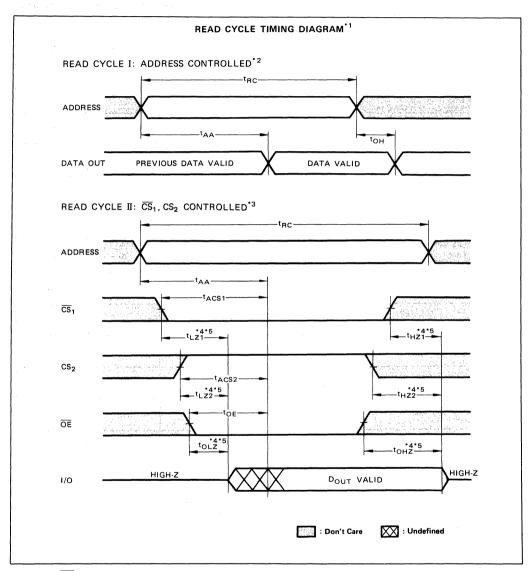

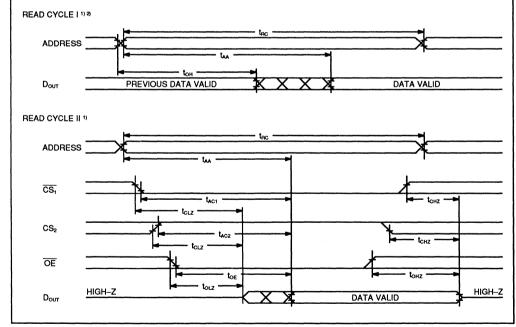

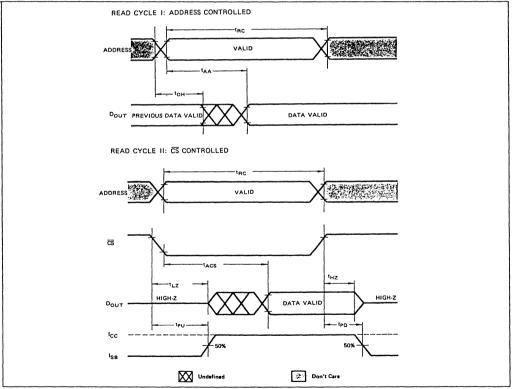

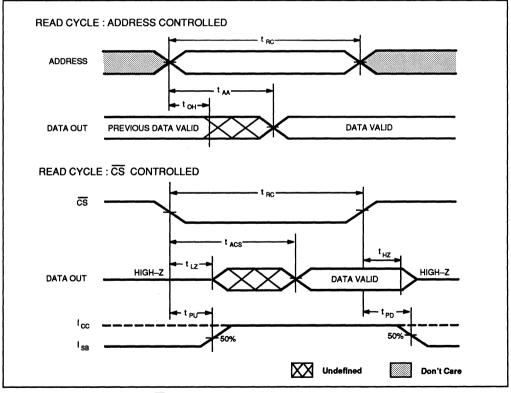

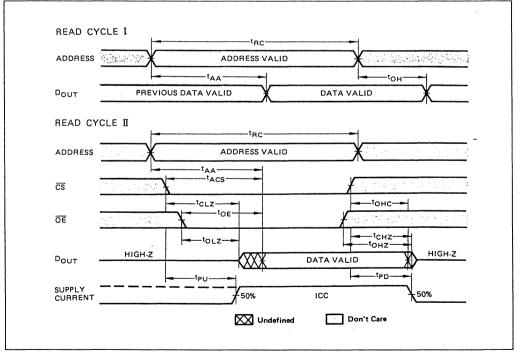

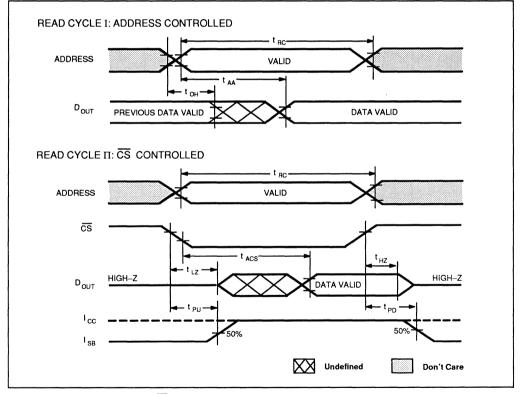

(Recommended operating conditions unless otherwise noted.) READ CYCLE\*1

| D                                                  | Cumbal           | MB 81 | C67-35 | MB 81C67-45 MB 81C6 |     | C67-55 | Unit |      |

|----------------------------------------------------|------------------|-------|--------|---------------------|-----|--------|------|------|

| Parameter                                          | Symbol           | Min   | Max    | Min                 | Max | Min    | Max  | Unit |

| Read Cycle Time *2                                 | t <sub>RC</sub>  | 35    |        | 45                  |     | 55     |      | ns   |

| Address Access Time <sup>*3</sup>                  | t <sub>AA</sub>  |       | 35     |                     | 45  |        | 55   | ns   |

| Chip Select Access Time *4                         | t <sub>ACS</sub> |       | 35     |                     | 45  |        | 55   | ns   |

| Output Hold from Address Change                    | t <sub>он</sub>  | 5     |        | 5                   |     | 5      |      | ns   |

| Chip Selection to Output in Low-Z <sup>*5</sup>    | t <sub>LZ</sub>  | 5     |        | 5                   |     | 5      |      | ns   |

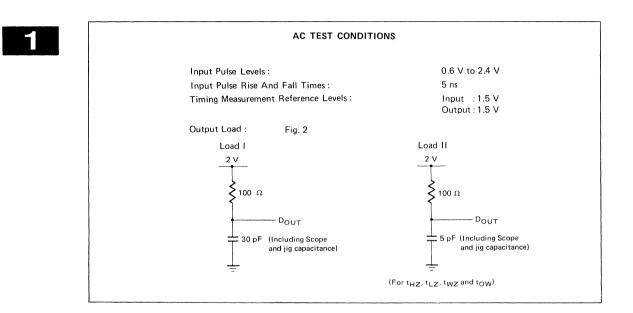

| Chip Deselection to Output in High-Z <sup>*5</sup> | t <sub>HZ</sub>  | 0     | 25     | 0                   | 25  | 0      | 30   | ns   |

| Chip Selection to Power Up                         | t <sub>PU</sub>  | 0     |        | 0                   |     | 0      |      | ns   |

| Chip Deselection to Power Down                     | t <sub>PD</sub>  |       | 30     |                     | 40  |        | 50   | ns   |

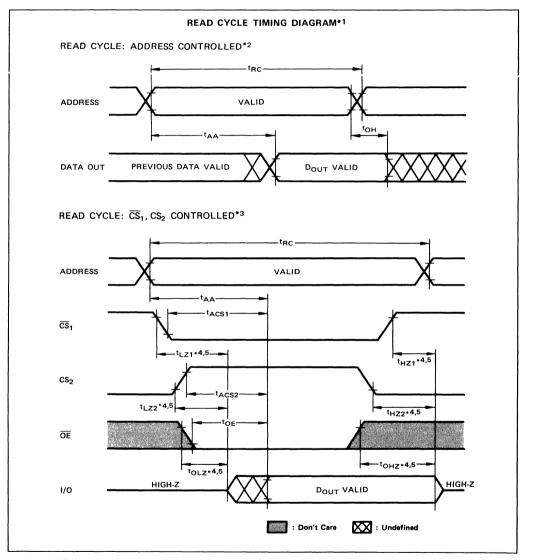

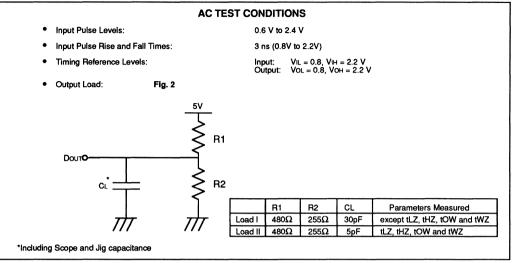

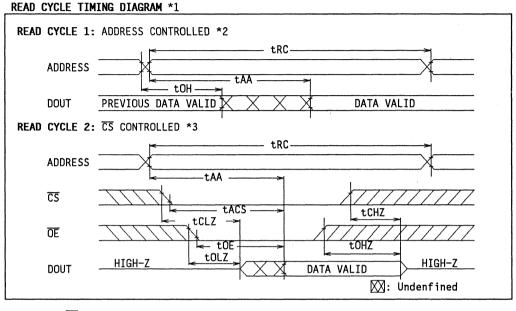

Note: \*1 WE is high for Read cycle.

\*2 All Read cycle are determined from the last address transition to the first address transition of the next address.

- \*3 Device is continuously selected,  $\overline{CS} = V_{1L}$ . \*4 Address valid prior to or coincident with  $\overline{CS}$  transition low.

- \*5 Transition is measured at the point of ±500mV from steady state voltage.

1-6

| MB | 81C67-35 |         |

|----|----------|---------|

| MB | 81C67-45 | FUJITSU |

| MB | 81C67-55 |         |

Note: \*1 WE is high for Read cycle.

\*3 Device is continuously selected,  $\overline{CS} = V_{1L}$ . \*4 Address valid prior to or coincident with  $\overline{CS}$  transition low.

\*5 Transition is measured at the point of ±500mV from steady state voltage.

1-7

<sup>\*2</sup> All Read cycle are determined from the last address transition to the first address transition of the next address.

|         | MB | 81C67-35 |

|---------|----|----------|

| FUJITSU | MB | 81C67-45 |

|         | MB | 81C67-55 |

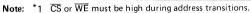

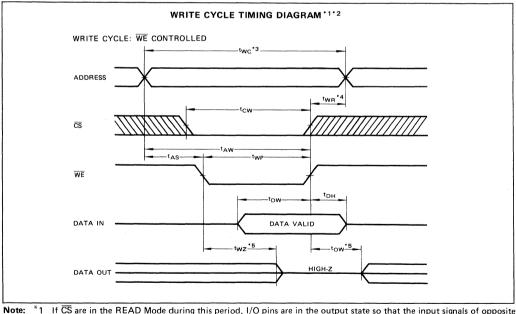

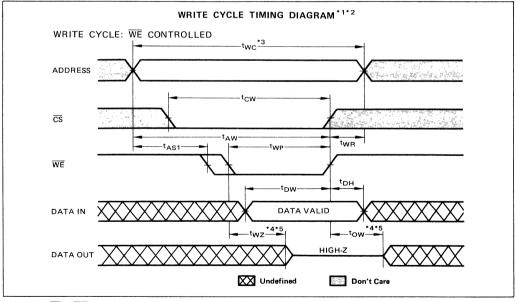

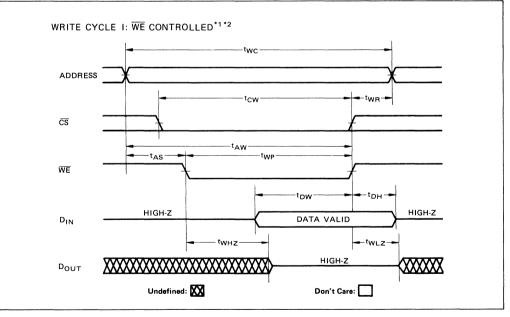

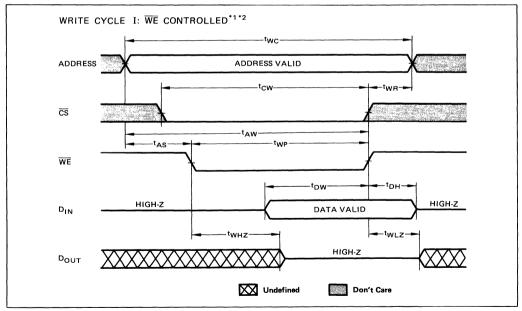

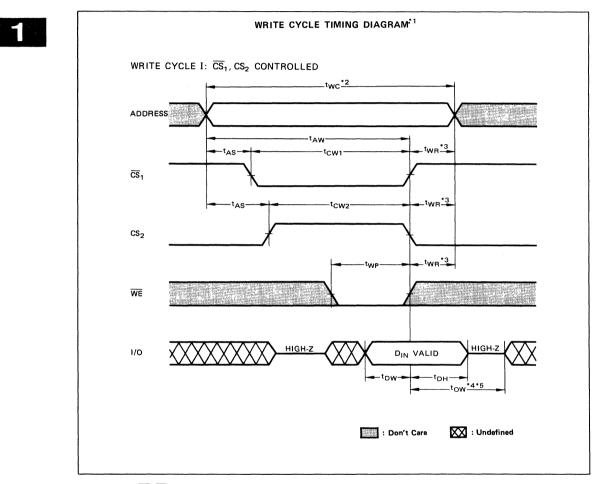

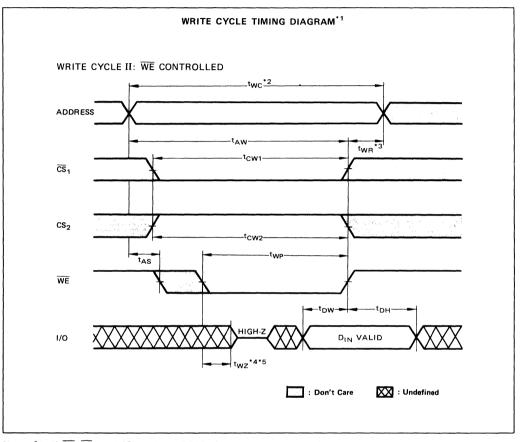

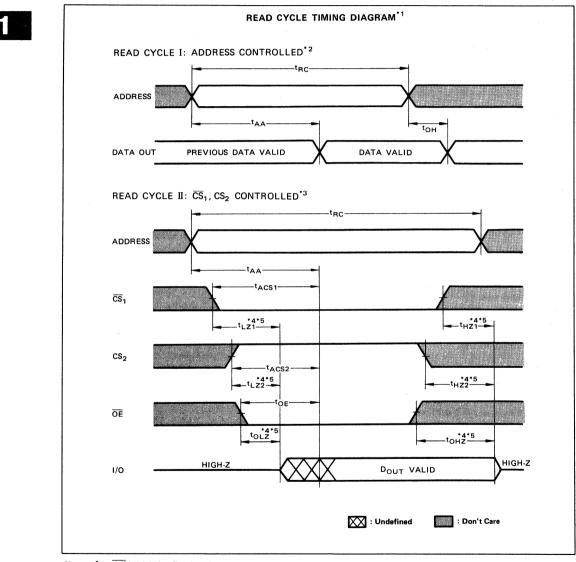

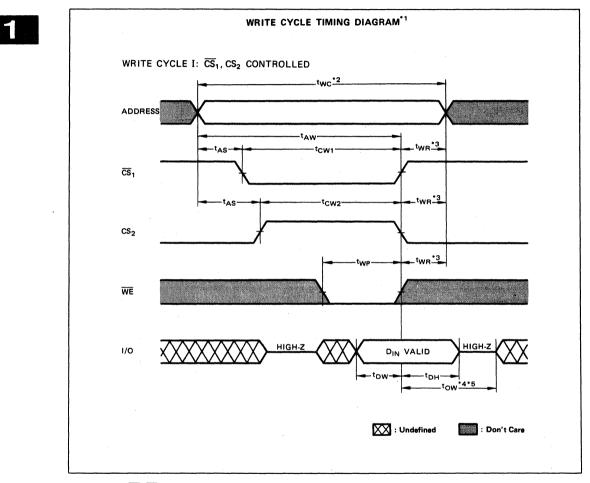

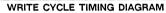

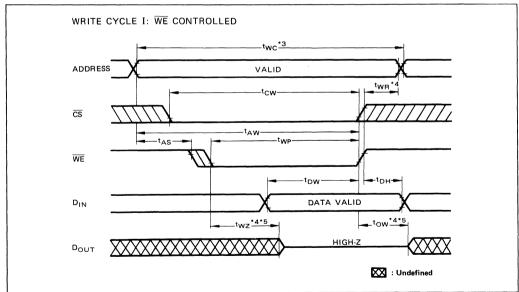

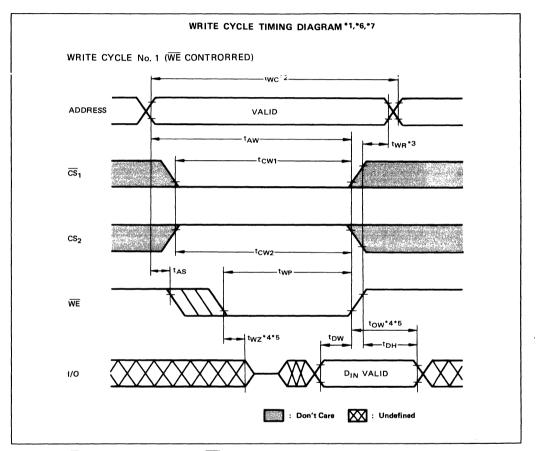

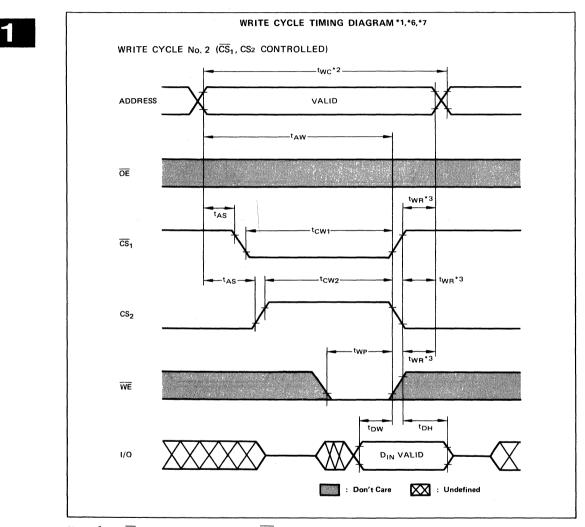

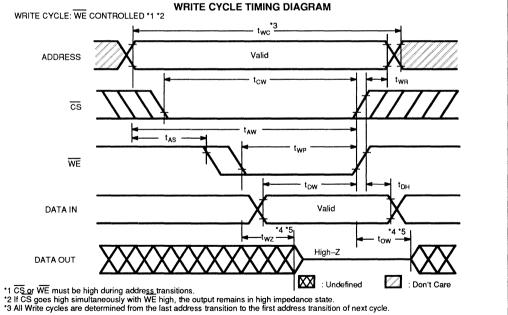

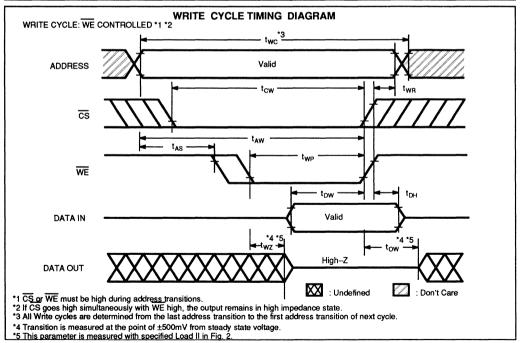

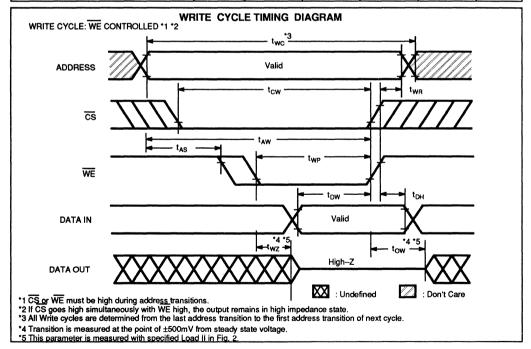

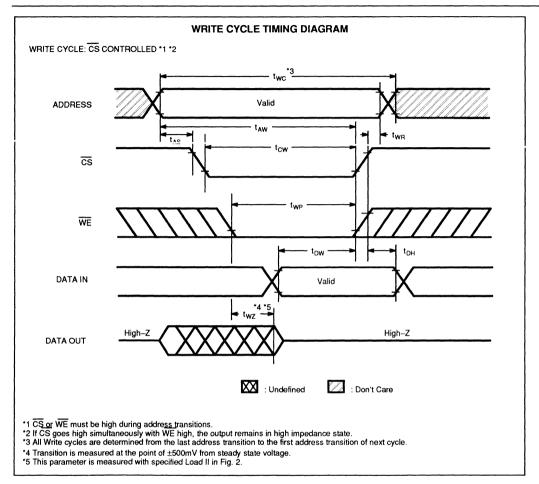

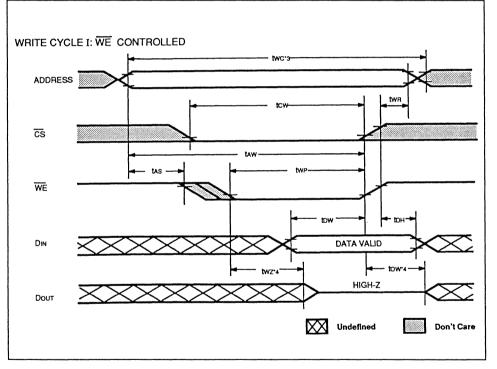

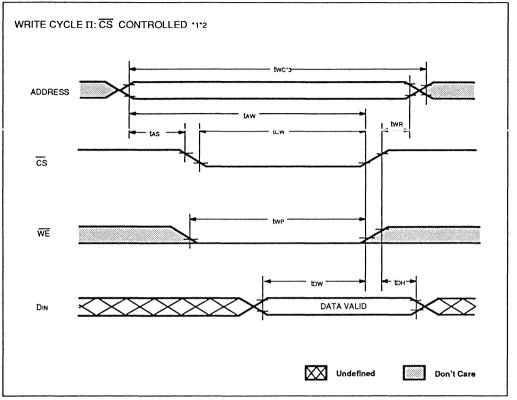

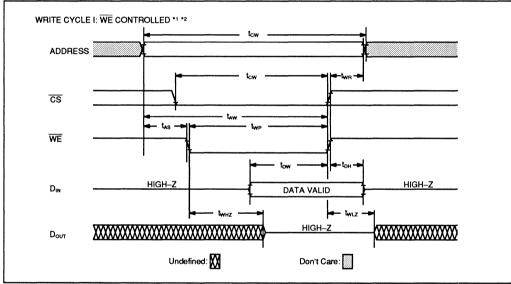

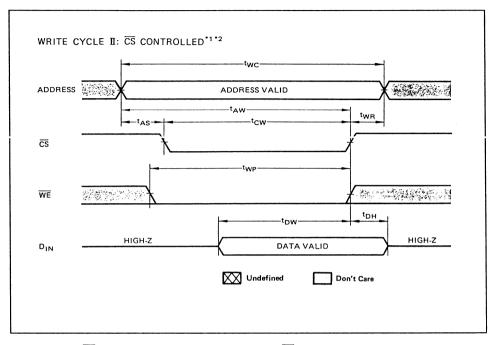

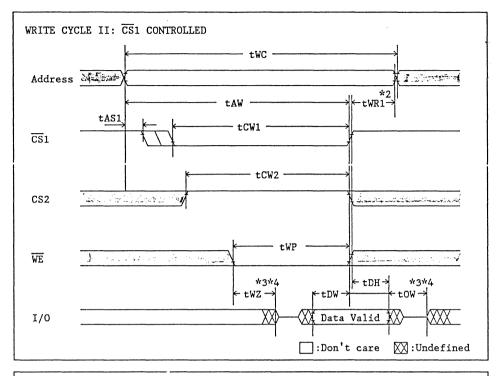

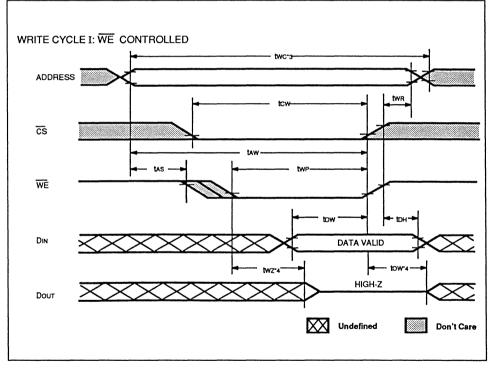

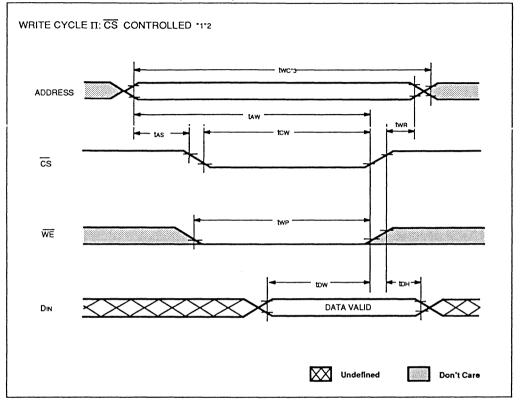

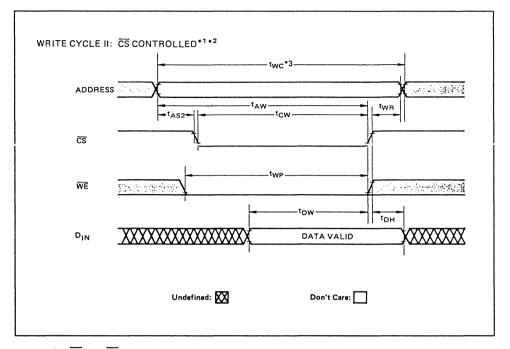

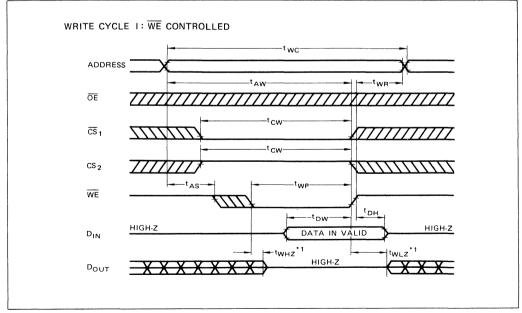

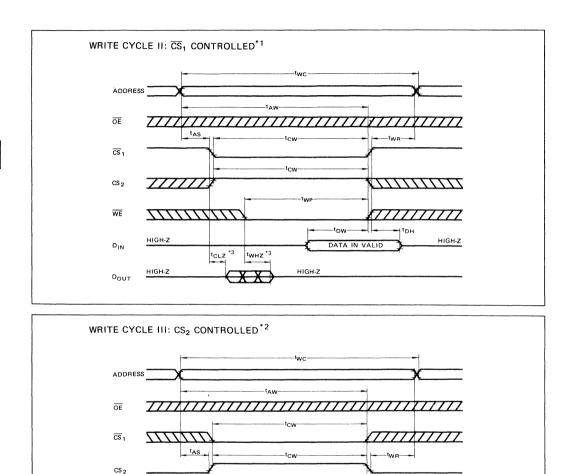

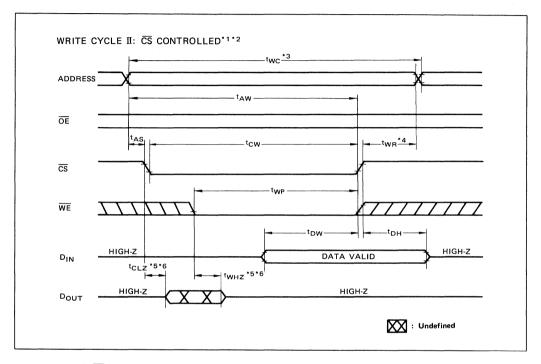

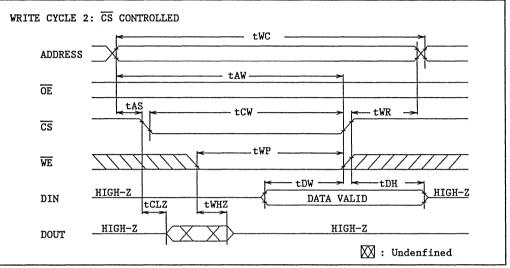

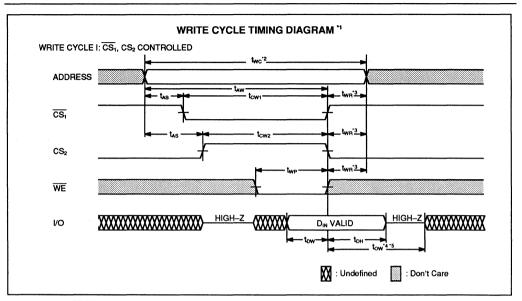

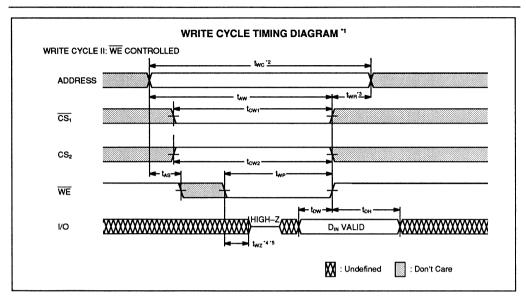

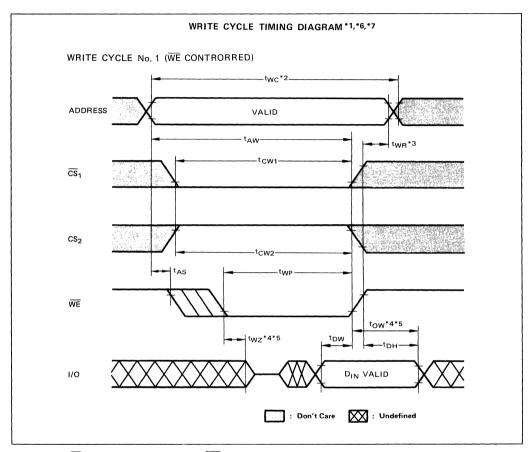

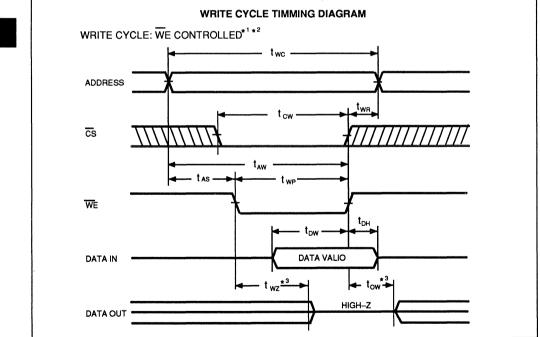

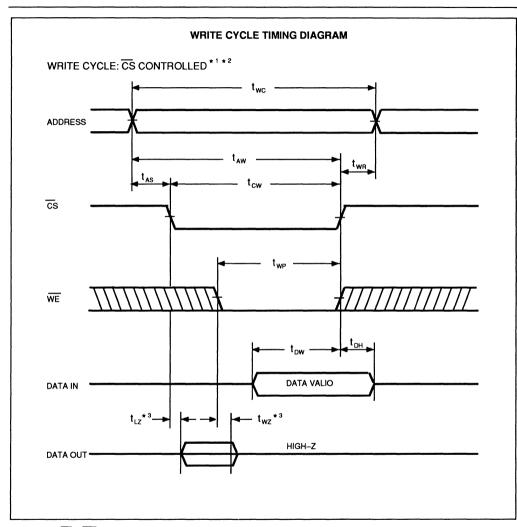

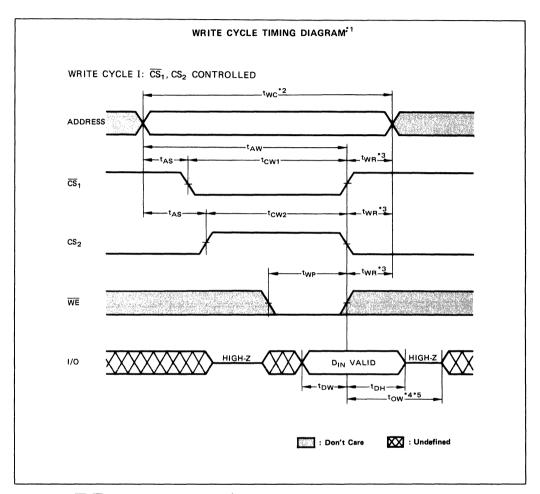

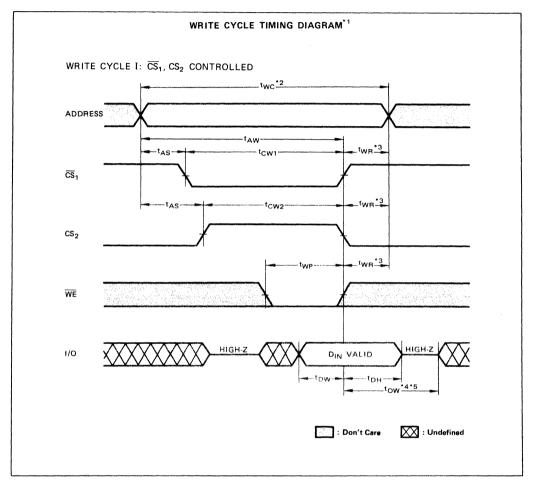

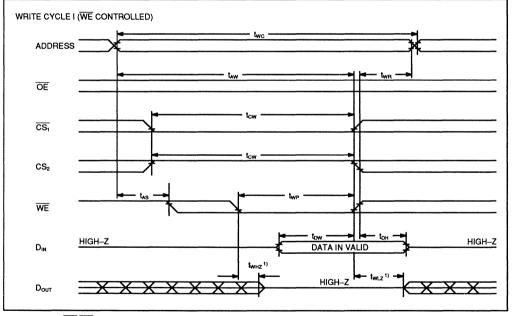

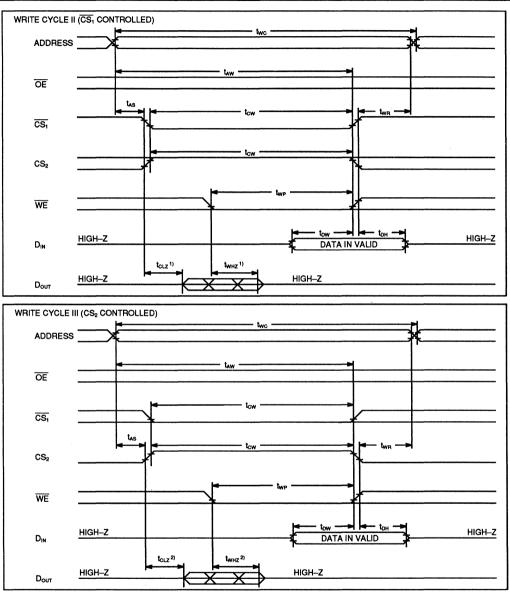

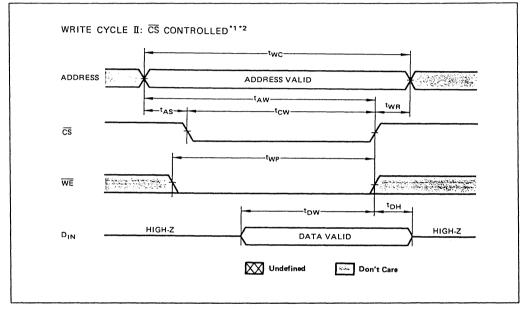

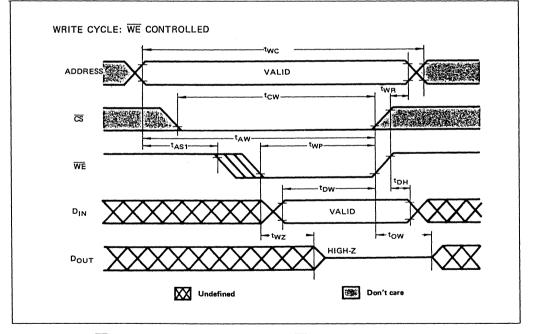

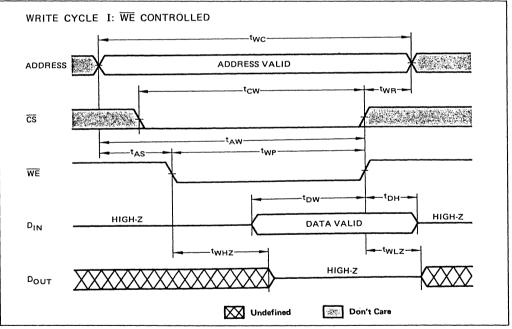

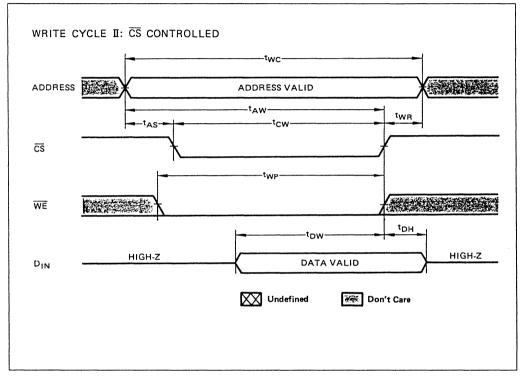

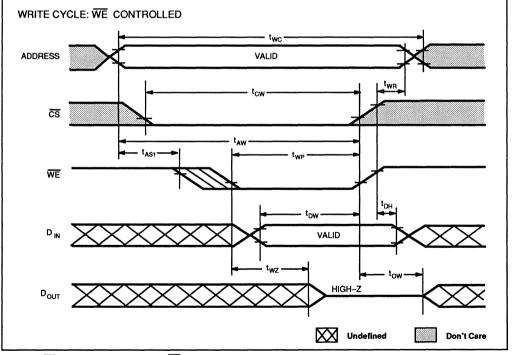

#### WRITE CYCLE\*1\*2

| Parameter                                      | Symbol          | MB 81 | C67-35 | MB 81 | C67-45 | MB 810 | C67-55 | 5<br>Unit |  |

|------------------------------------------------|-----------------|-------|--------|-------|--------|--------|--------|-----------|--|

|                                                | Jymbol          | Min   | Max    | Min   | Max    | Min    | Max    | Onit      |  |

| Write Cycle Time <sup>*3</sup>                 | twc             | 35    |        | 45    |        | 55     |        | ns        |  |

| Chip Selection to End of Write                 | tcw             | 30    |        | 35    |        | 50     |        | ns        |  |

| Address Valid to End of Write                  | t <sub>AW</sub> | 30    |        | 35    |        | 50     |        | ns        |  |

| Address Setup Time                             | t <sub>AS</sub> | 0     |        | 0     |        | 0      |        | ns        |  |

| Write Pulse Width                              | t <sub>WP</sub> | 20    |        | 25    |        | 30     |        | ns        |  |

| Data Valid to End of Write                     | t <sub>DW</sub> | 20    |        | 20    |        | 25     |        | ns        |  |

| Write Recovery Time                            | t <sub>wR</sub> | 0     |        | 0     |        | 0      |        | ns        |  |

| Data Hold Time                                 | t <sub>DH</sub> | 0     |        | 0     |        | 0      |        | ns        |  |

| Write Enable to Output in High-Z <sup>*4</sup> | twz             | 0     | 25     | 0     | 25     | 0      | 30     | ns        |  |

| Output Active from End of Write*4              | tow             | 0     | 25     | 0     | 25     | 0      | 30     | ns        |  |

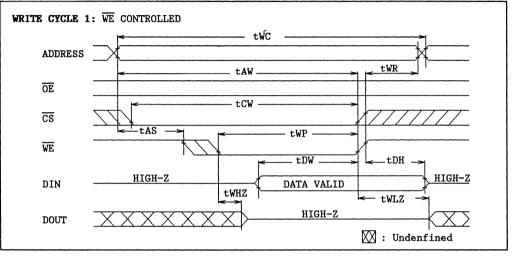

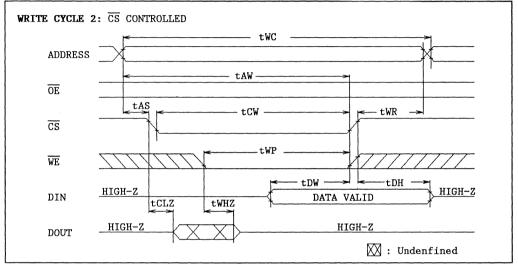

Note: \*1 CS or WE must be high during address transition.

\*2 If CS goes high simultaneously with WE high, the output remains in high impedance state.

\*3 All Write cycle are determined from the last address transition to the first address transition of next address.

\*4 Transition is measured at the point of  $\pm$ 500mV from steady state voltage.

| MB | 81C67-35 |         |

|----|----------|---------|

| MB | 81C67-45 | FUJITSU |

| MB | 81C67-55 |         |

Note: \*1  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  must be high during address transistion.

\*2 If CS goes high simultaneously with WE high, the output remains in high impedance state.

\*3 All Write cycle are determined from the last address transistion to the first address transition of next address.

\*4 Transition is measured at the point of ±500mV from steady state voltage.

|         | MB | 81C67-35 |

|---------|----|----------|

| FUJITSU | MB | 81C67-45 |

|         | MB | 81C67-55 |

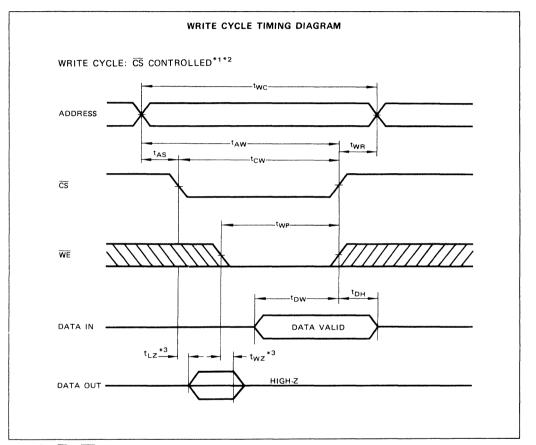

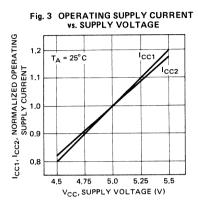

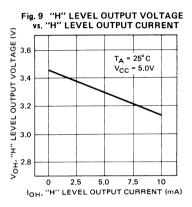

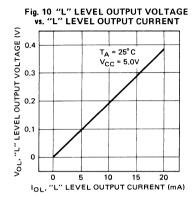

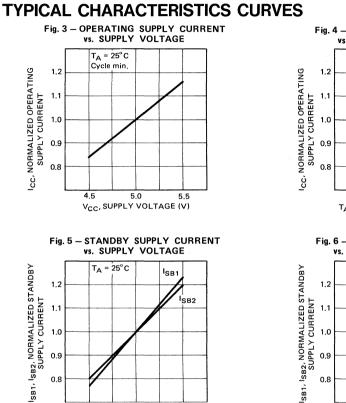

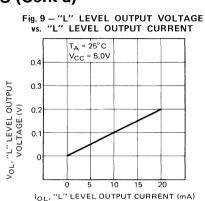

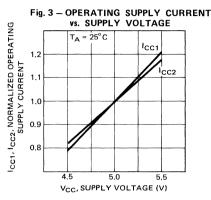

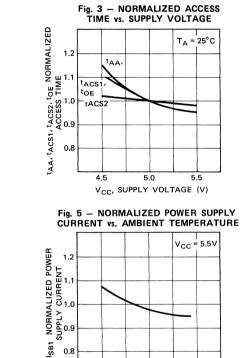

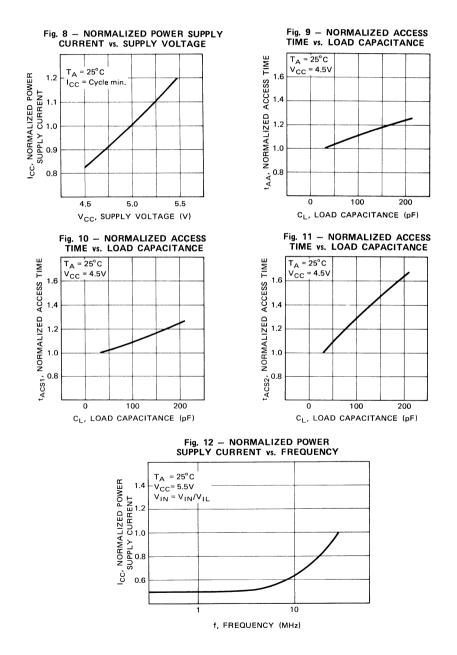

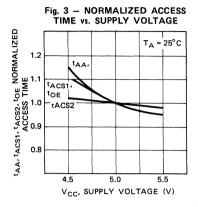

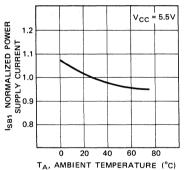

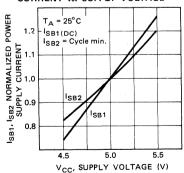

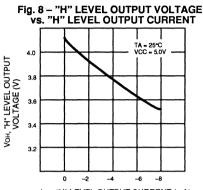

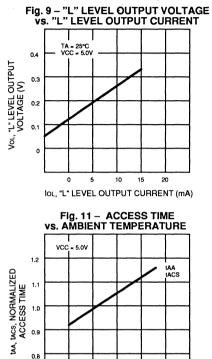

### **TYPICAL CHARACTERISTICS CURVES**

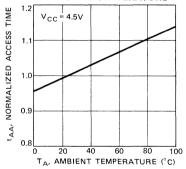

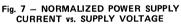

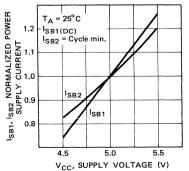

Fig. 7 – NORMALIZED POWER SUPPLY CURRENT vs. SUPPLY VOLTAGE

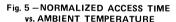

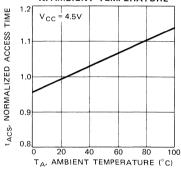

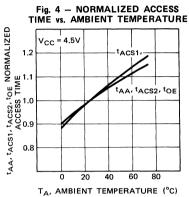

Fig. 6 – NORMALIZED ACCESS TIME vs. AMBIENT TEMPERATURE

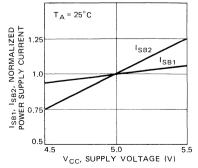

Fig. 8 – NORMALIZED POWER SUPPLY CURRENT vs. SUPPLY VOLTAGE

| MB | 81C67-35 |         |

|----|----------|---------|

| MB | 81C67-45 | FUJITSU |

| MB | 81C67-55 |         |

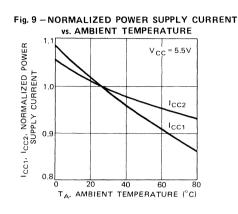

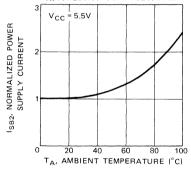

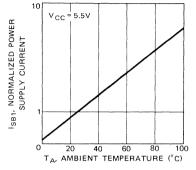

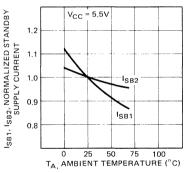

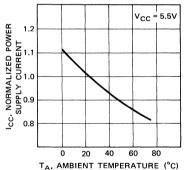

Fig. 11 -- NORMALIZED POWER SUPPLY CURRENT vs. AMBIENT TEMPERATURE

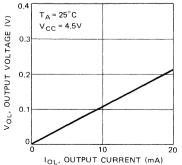

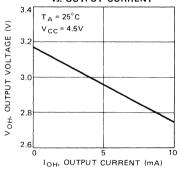

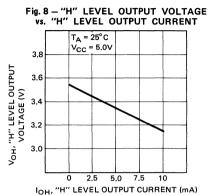

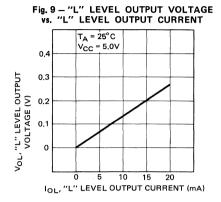

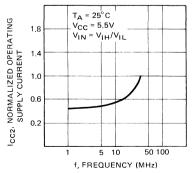

Fig. 13 – OUTPUT VOLTAGE vs. OUTPUT CURRENT

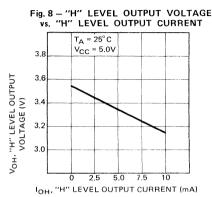

Fig. 10-NORMALIZED POWER SUPPLY CURRENT vs. AMBIENT TEMPERATURE

Fig. 12 – OUTPUT VOLTAGE vs. OUTPUT CURRENT

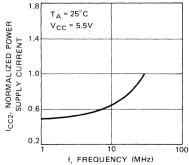

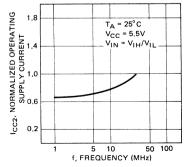

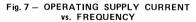

Fig. 14 - NORMALIZED POWER SUPPLY CURRENT vs. FREQUENCY

|         | MB | 81C67-35 |

|---------|----|----------|

| FUJITSU | MB | 81C67-45 |

|         | MB | 81C67-55 |

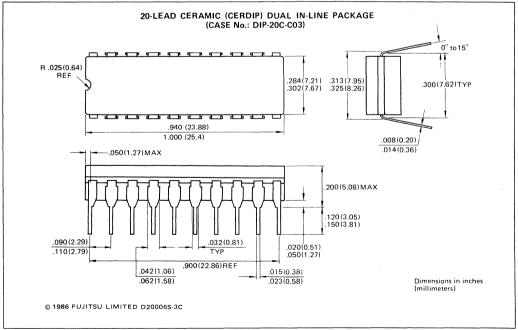

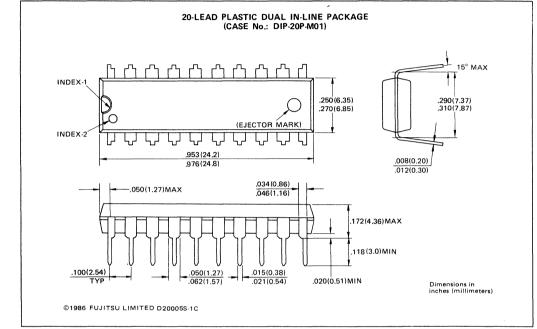

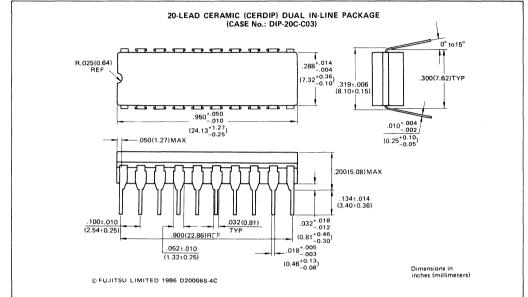

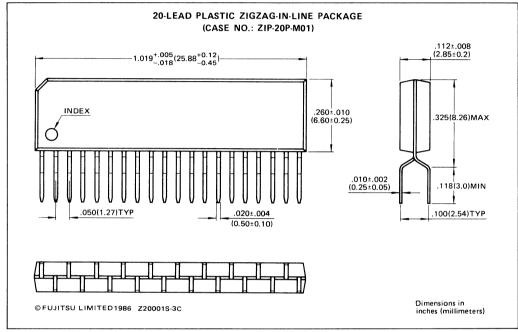

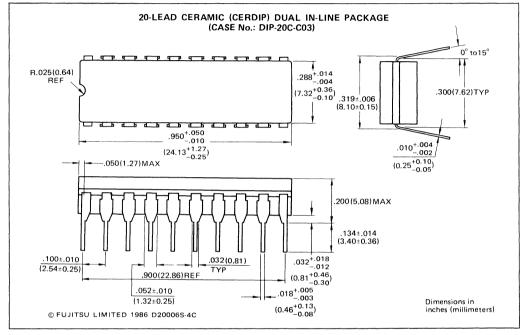

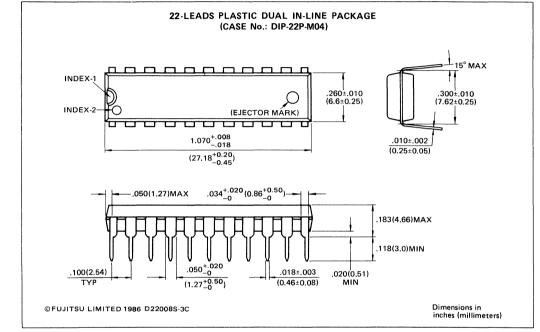

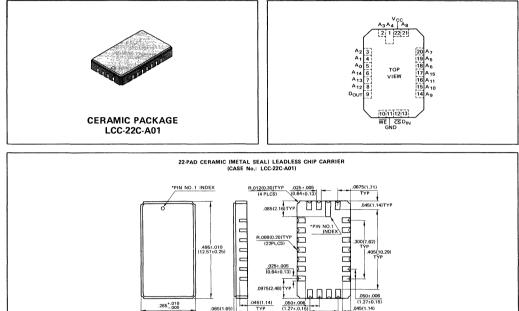

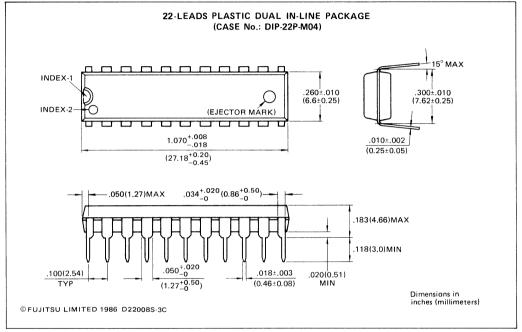

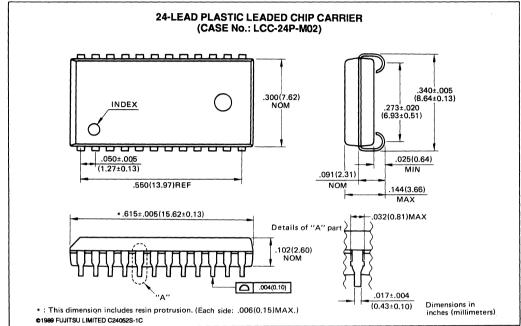

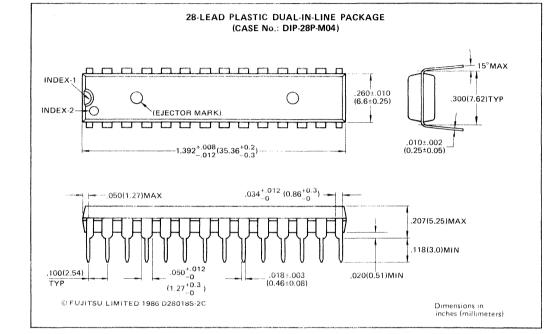

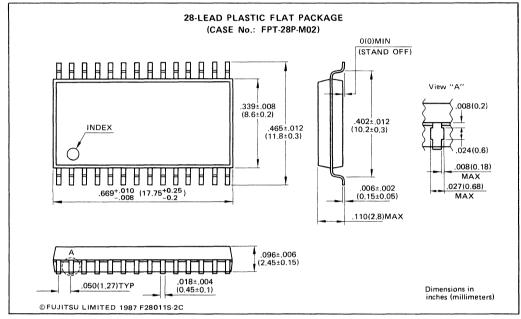

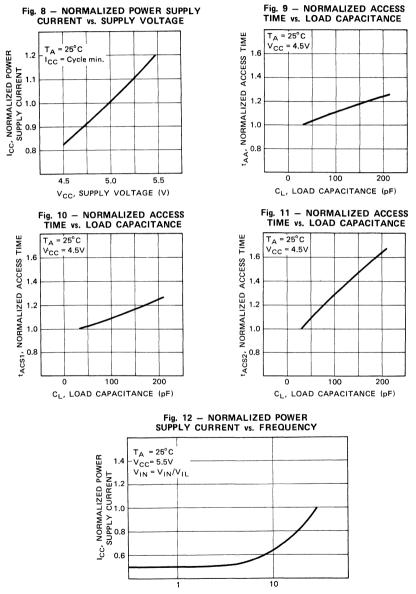

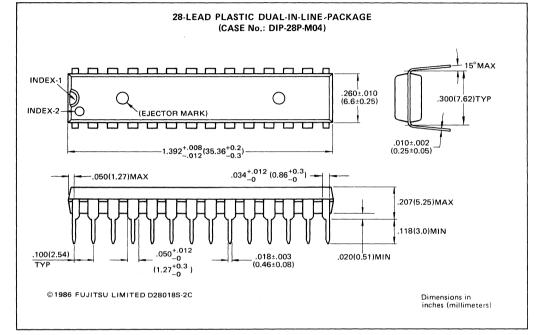

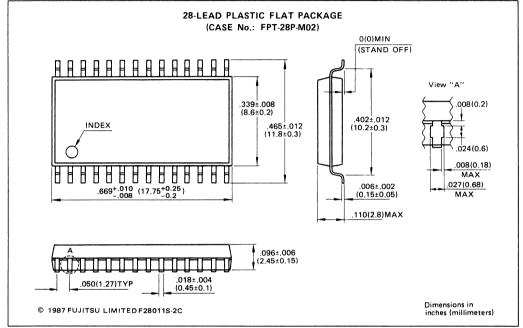

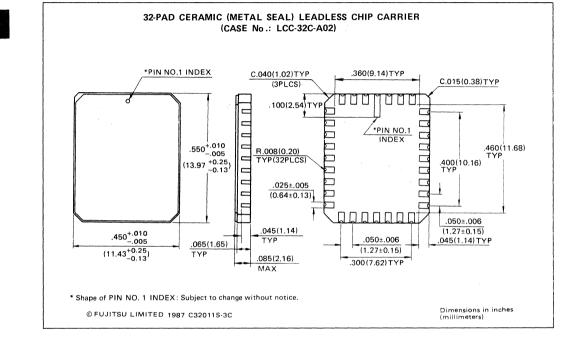

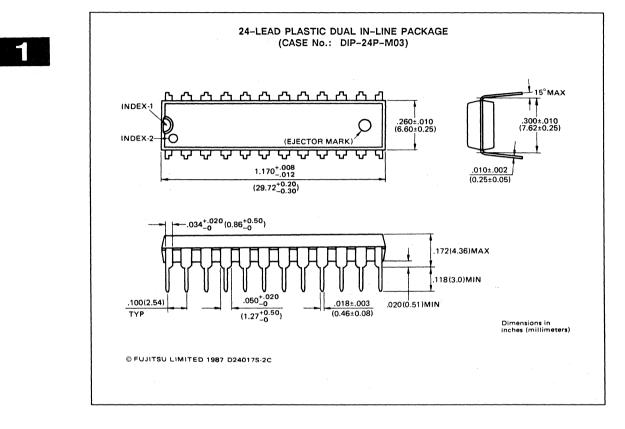

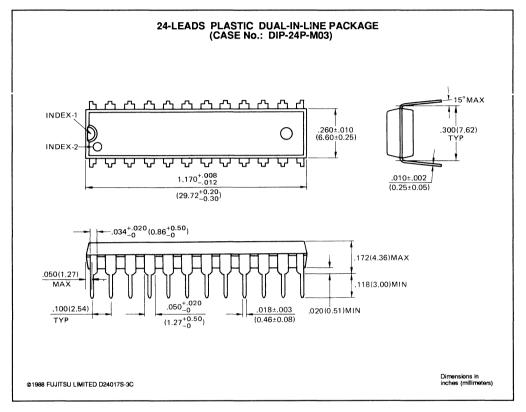

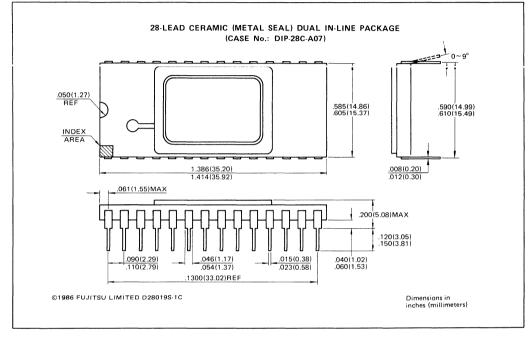

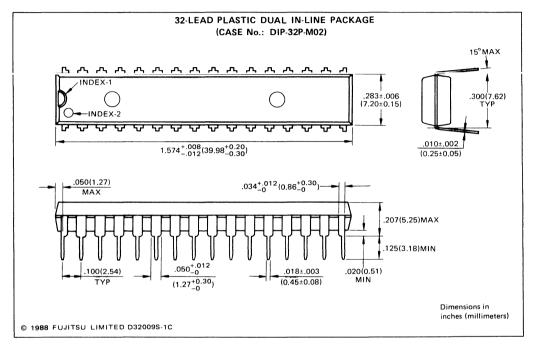

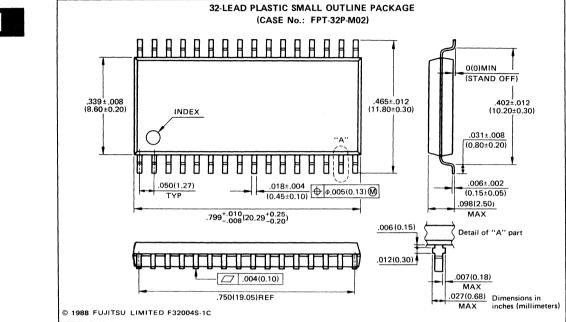

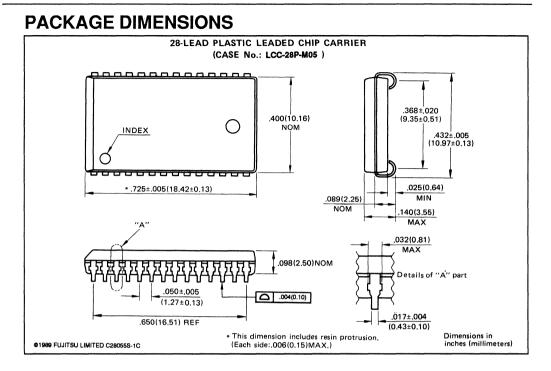

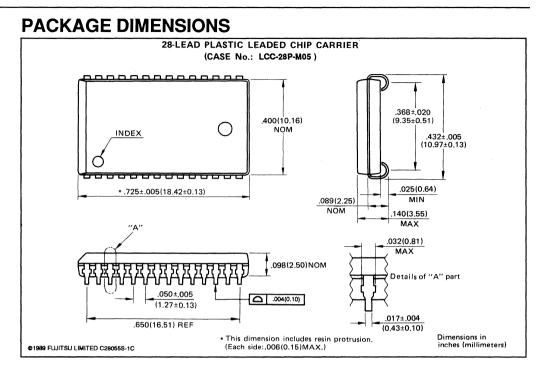

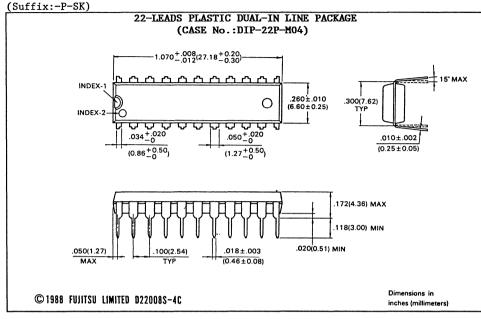

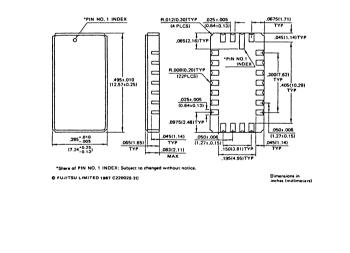

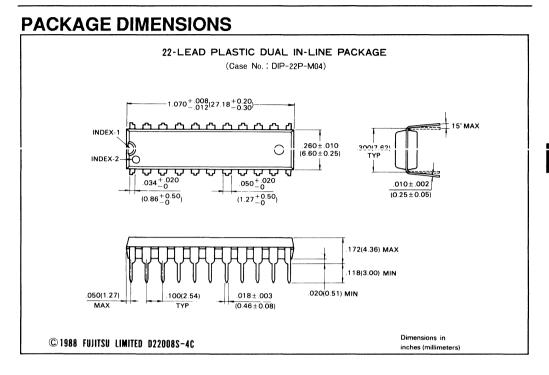

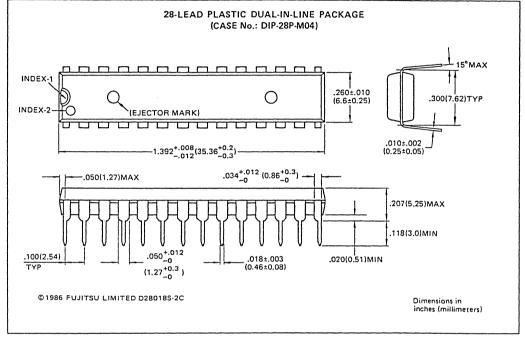

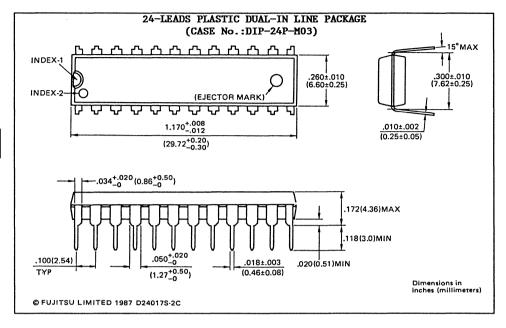

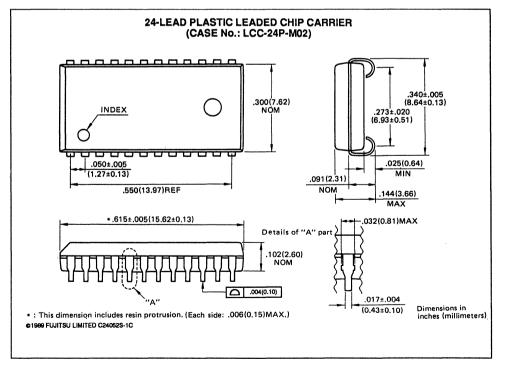

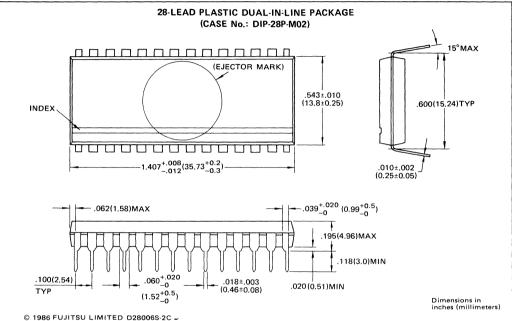

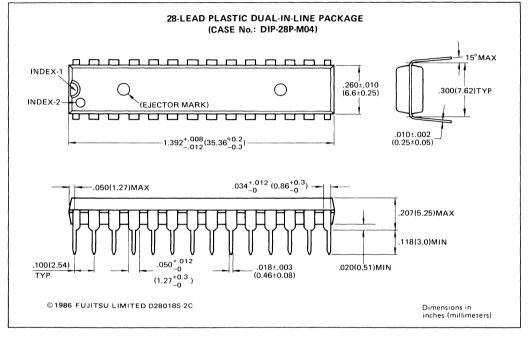

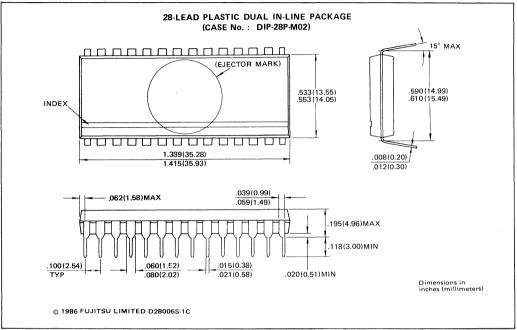

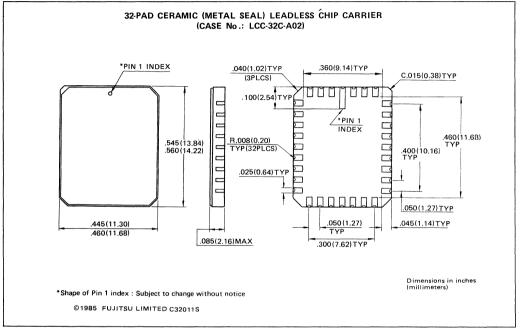

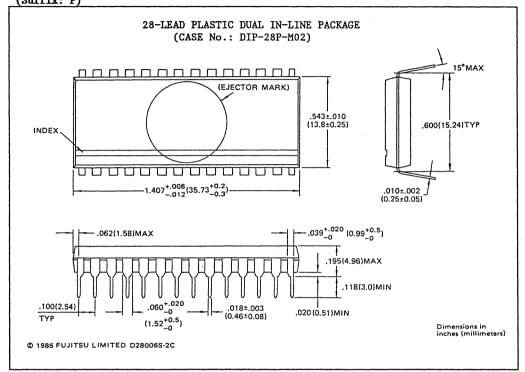

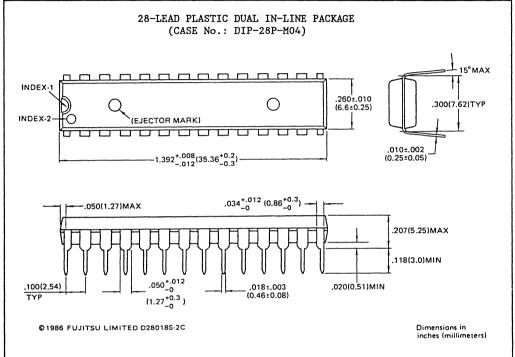

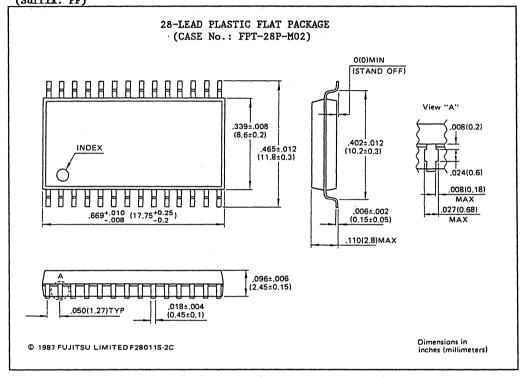

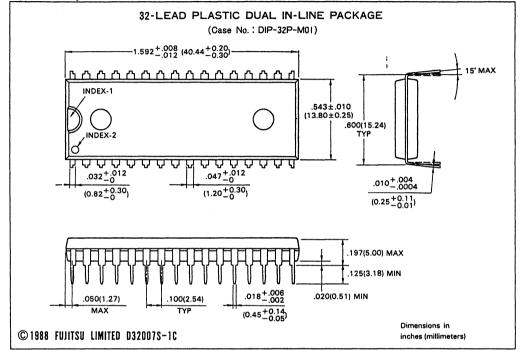

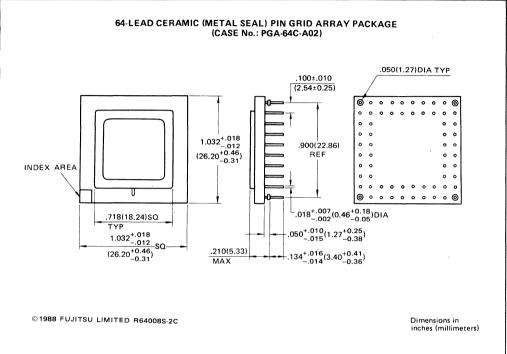

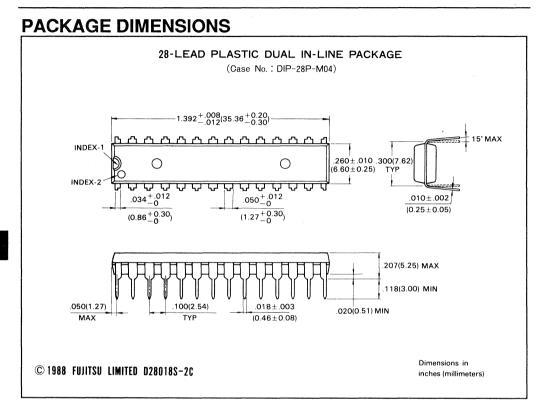

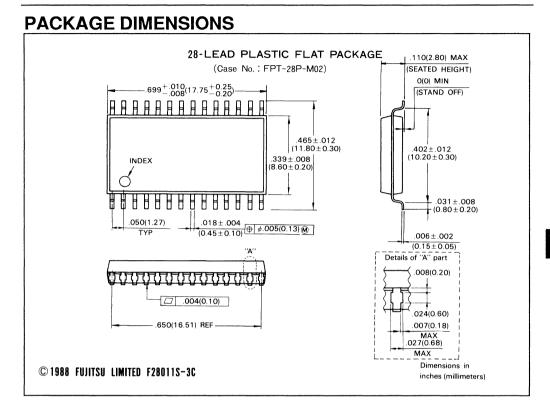

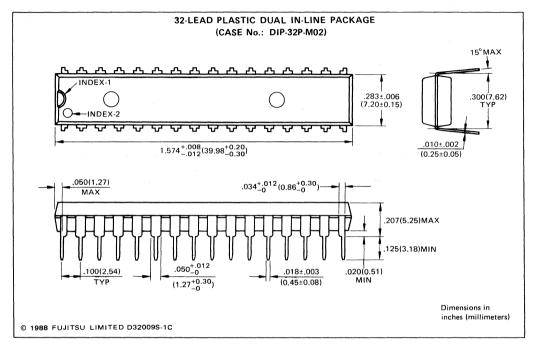

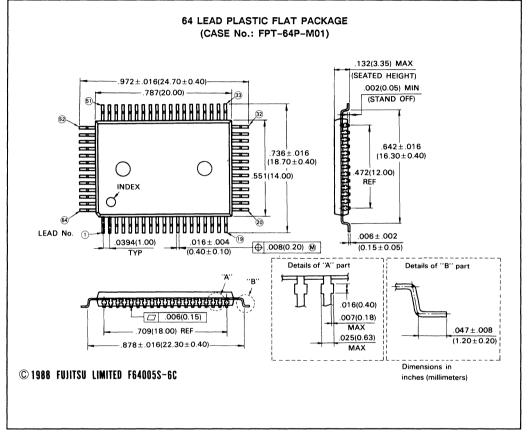

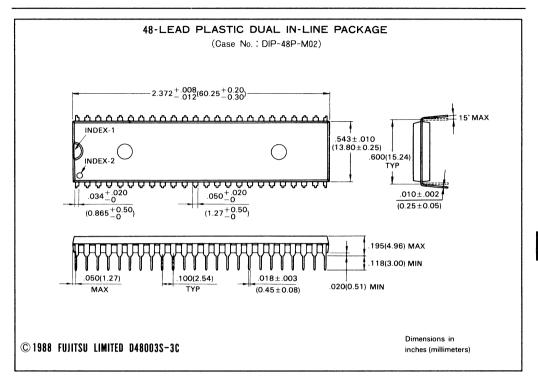

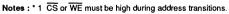

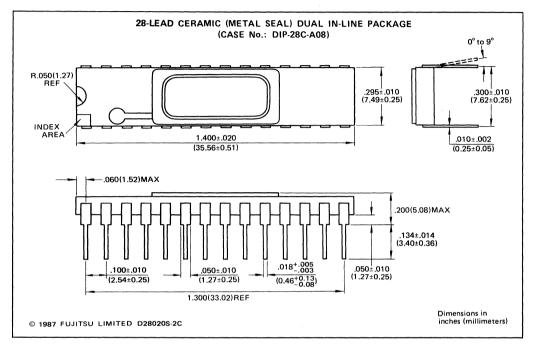

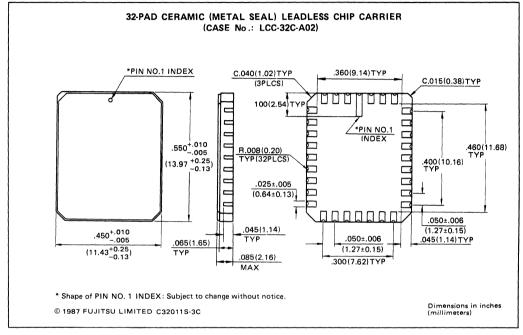

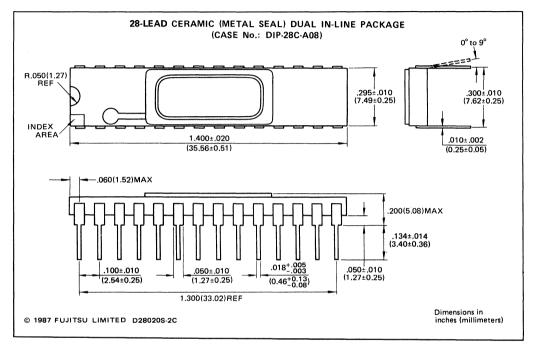

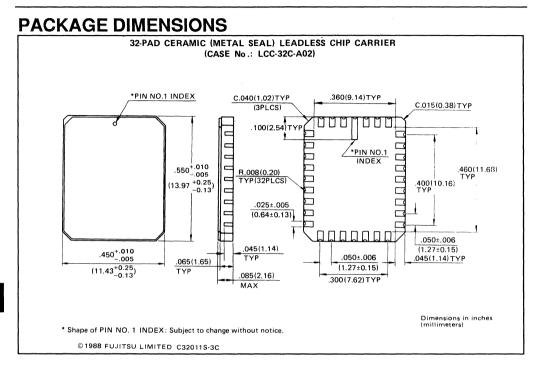

### PACKAGE DIMENSIONS

(Suffix: CZ)

1

| MB | 81C67-35 |         |

|----|----------|---------|

| MB | 81C67-45 | FUJITSU |

| MB | 81C67-55 |         |

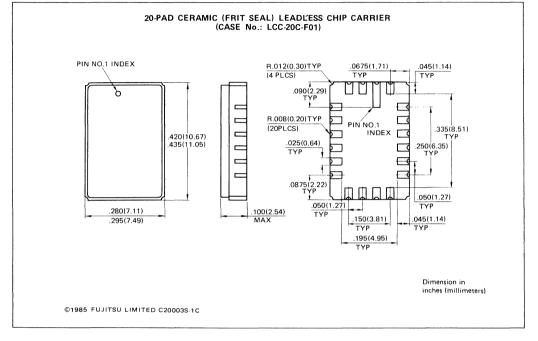

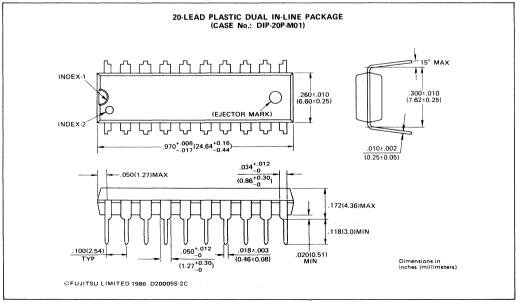

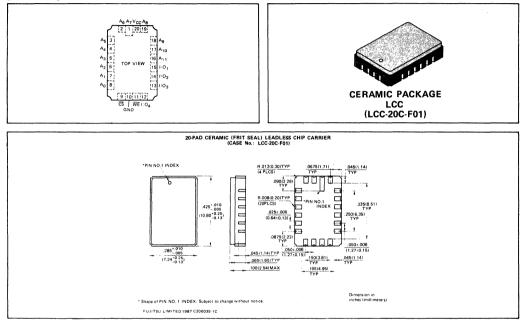

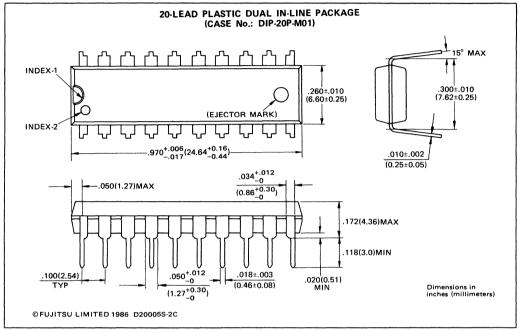

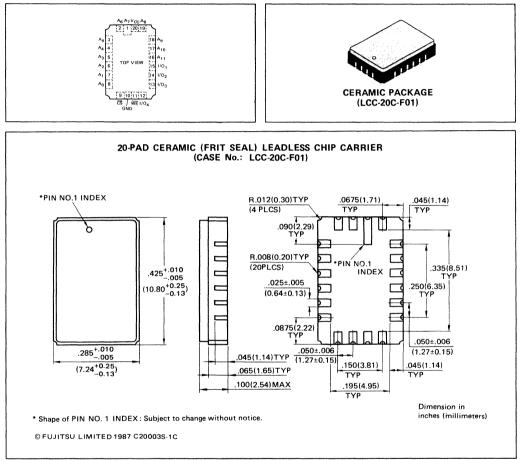

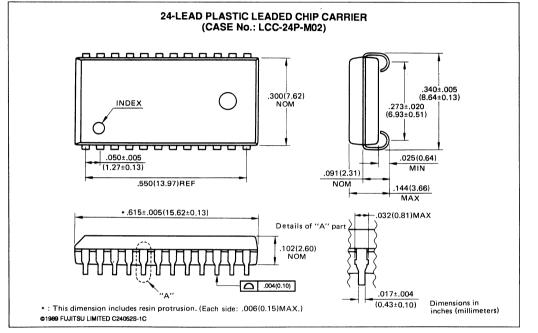

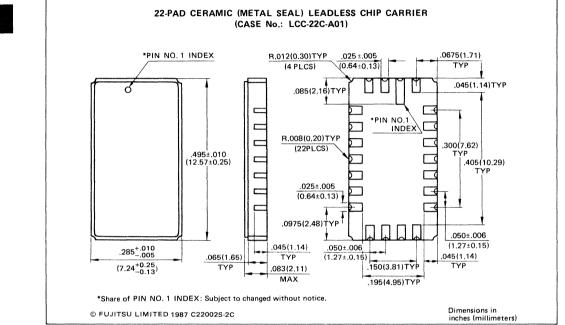

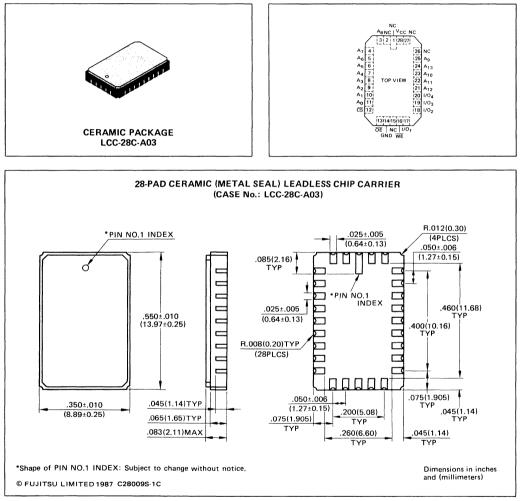

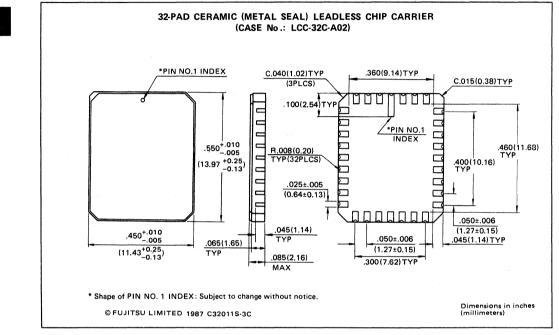

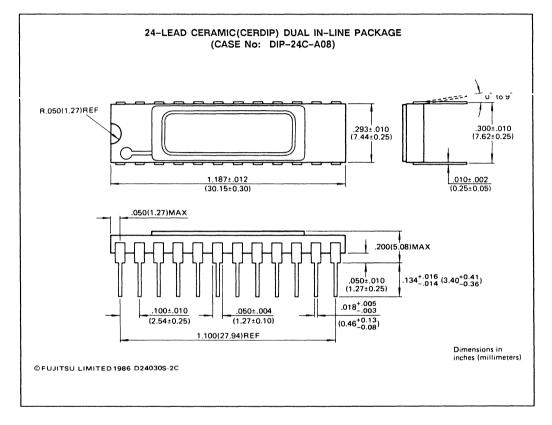

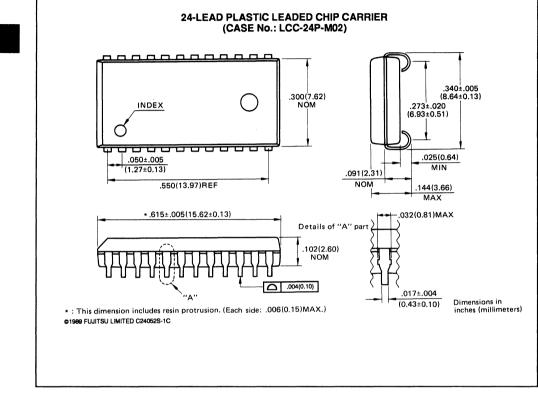

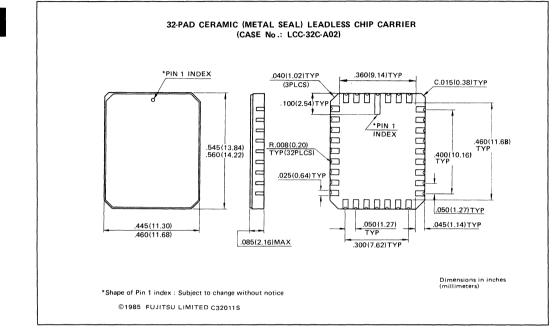

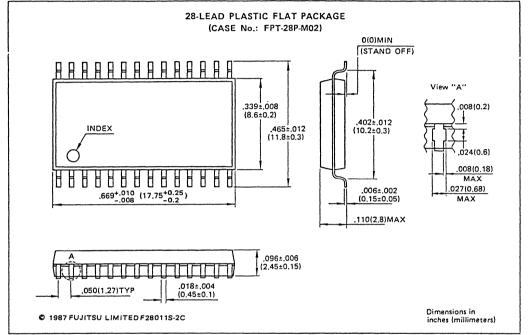

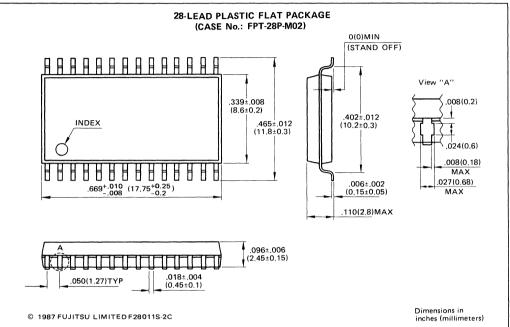

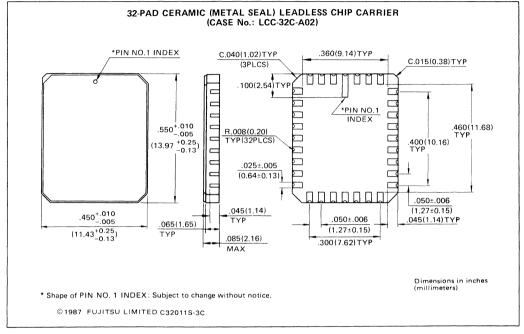

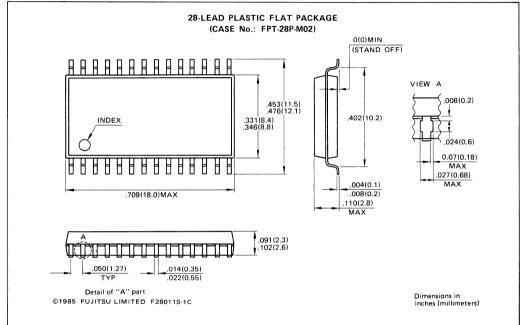

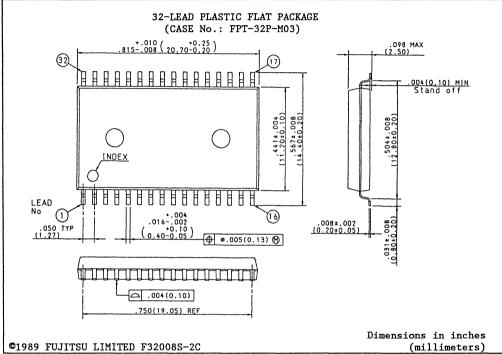

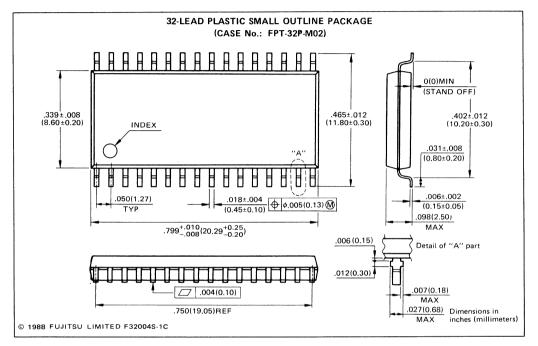

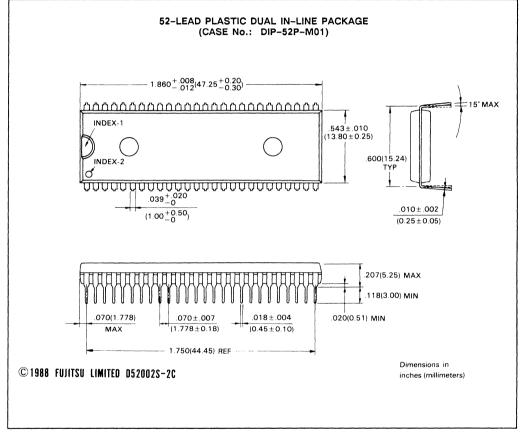

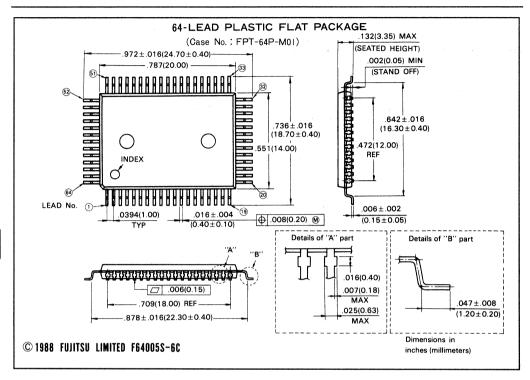

### PACKAGE DIMENSIONS

(Suffix: TV)

1

|         | MB | 81C67-35 |

|---------|----|----------|

| FUJITSU | MB | 81C67-45 |

|         | MB | 81C67-55 |

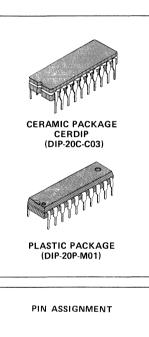

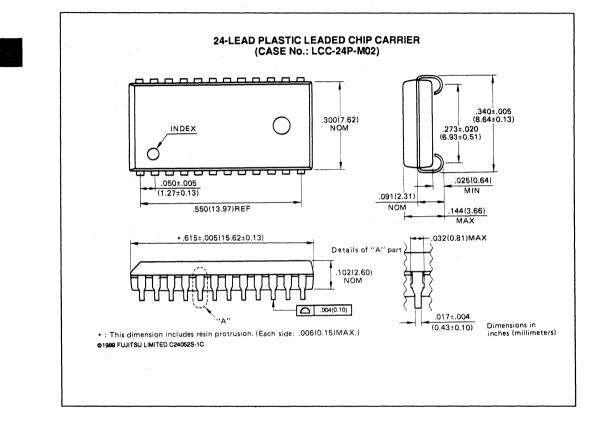

(Suffix: P)

## CMOS 16384-BIT STATIC RANDOM ACCESS MEMORY

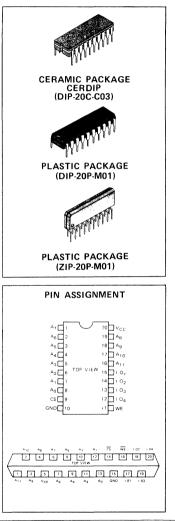

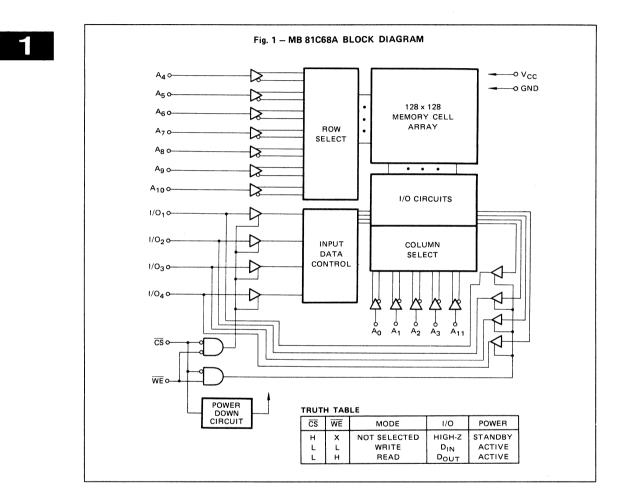

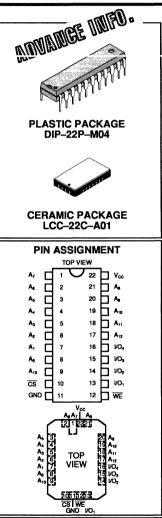

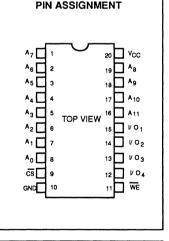

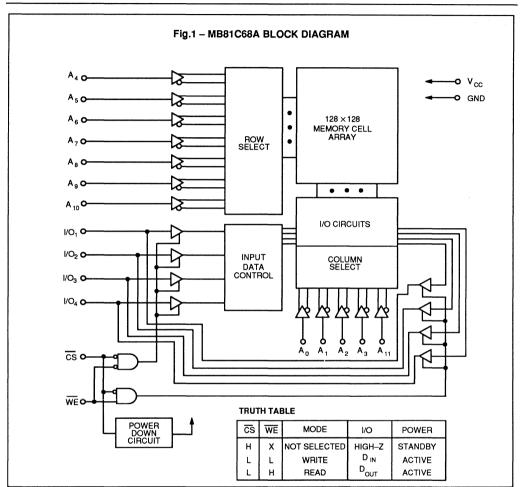

### MB81C68A-25 MB81C68A-30 MB81C68A-35

#### 4K x 4 (16,384-BIT) STATIC RANDOM ACCESS MEMORY WITH SUPER HIGH SPEED AND AUTOMATIC POWER DOWN

The Fujitsu MB 81C68A is 4096 words x 4 bits static random access memory fabricated with a CMOS silicon gate process. The memory utilizes asynchronous circuitry and all pins are TTL compatible and a single 5 volts power supply is required.

A separate chip select ( $\overline{CS}$ ) pin simplifies multipackage systems design. It permits the selection of an individual package when outputs are OR-tied, and furthermore on selecting a single package by  $\overline{CS}$ , the other deselected packages automatically power down.

All devices offer the advantages of low power dissipation, low cost, and high performance.

- Organization: 4096 words x 4 bits

- Static operation: No clocks or timing strobe required

- Fast access time: t<sub>AA</sub> = t<sub>ACS</sub> = 25 ns max. (MB 81C68A-25)

- $t_{AA} = t_{ACS} = 30 \text{ ns max.}$  (MB 81C68A-30)  $t_{AA} = t_{ACS} = 35 \text{ ns max.}$  (MB 81C68A-35)

- Low power consumption: 385 mW max. (MB 81C68A-3

- 138 mW max. (Standby, TTL level) 83 mW max. (Standby, CMOS level)

- Single +5V supply ±10% tolerance

- TTL compatible inputs and outputs

- Three-state outputs with OR-tie capability

- Chip select for simplified memory expansion, automatic power down

- All inputs and outputs have protection against static charge

- Standard 20-pin DIP (Suffix -P(plastic)/Suffix: -Z(cerdip))

- Standard 20-pad LCC (Suffix: -TV)

- Standard 20-pin ZIP (Suffix: -PSZ)

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating                                               |                   | Symbol           | Value       | Unit |

|------------------------------------------------------|-------------------|------------------|-------------|------|

| Supply Voltage                                       |                   | V <sub>cc</sub>  | -0.5 to +7  | V    |

| Input Voltage on Any Pin with respect to GND         |                   | V <sub>IN</sub>  | -3.5 to +7  | V    |

| Output Voltage on Any I/O Pin<br>with respect to GND |                   | V <sub>OUT</sub> | -0.5 to +7  | V    |

| Output current                                       | Output current    |                  | ±20         | mA   |

| Power dissipation                                    | Power dissipation |                  | 1.0         | w    |

| Temperature under Bias                               |                   | TBIAS            | -10 to +85  | °C   |

| Storage Temperature                                  | CERAMIC           | т                | -65 to +150 | °c   |

| Storage Temperature                                  | PLASTIC           | T <sub>STG</sub> | -45 to +125 |      |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit

January 1988 Edition 2.0

|         | MB81C68A-25 |

|---------|-------------|

| FUJITSU | MB81C68A-30 |

|         | MB81C68A-35 |

### CAPACITANCE (T<sub>A</sub> = 25°C, f = 1 MHz)

| Parameter                                                  | Symbol           | Тур | Max | Unit |

|------------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (V <sub>IN</sub> = 0 V)                  | C <sub>IN</sub>  |     | 5   | pF   |

| $\overline{\text{CS}}$ Capacitance (V <sub>CS</sub> = 0 V) | C <sub>CS</sub>  |     | 6   | pF   |

| I/O Capacitance (V <sub>I/O</sub> = 0 V)                   | C <sub>1/O</sub> |     | 7   | pF   |

### **RECOMMENDED OPERATING CONDITIONS**

(Referenced to GND)

| Parameter           | Symbol          | Min   | Тур | Max | Unit |

|---------------------|-----------------|-------|-----|-----|------|

| Supply Voltage      | V <sub>cc</sub> | 4.5   | 5.0 | 5.5 | V    |

| Input Low Voltage   | VIL             | -2.0* |     | 0.8 | v    |

| Input High Voltage  | V <sub>IH</sub> | 2.2   |     | 6.0 | v    |

| Ambient Temperature | T <sub>A</sub>  | 0     |     | 70  | °C   |

Note: \* -2.0V Min. for pulse width less than 20 ns. ( $V_{1L}$  Min = -0.5V at DC level)

### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                     | Test Condition                                                                                                                                                                                                           | Symbol           | Min | Тур | Max | Unit |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Input Leakage<br>Current      | $V_{IN} = 0 V \text{ to } V_{CC}$                                                                                                                                                                                        | I <sub>LI</sub>  | -10 |     | 10  | μΑ   |

| Output Leakage<br>Current     | $\overline{\text{CS}} = V_{1H},$ $V_{1/O} = 0 \text{ V to } V_{CC}$                                                                                                                                                      | I <sub>LO</sub>  | -10 |     | 10  | μΑ   |

| Active (DC) Supply<br>Current | $I_{OUT} = 0 \text{ mA } \overline{CS} = V_{IL},$<br>$V_{IN} = V_{IL} \text{ or } V_{IH}$                                                                                                                                | I <sub>CC1</sub> |     | 25  | 50  | mA   |

| Operating Supply<br>Current   | <del>CS</del> = V <sub>IL</sub><br>I <sub>OUT</sub> = 0 mA, Cycle = Min                                                                                                                                                  | lcc2             |     | 40  | 70  | mA   |

| Standby Supply Current        | $\label{eq:cs} \begin{split} \overline{\text{CS}} &= \text{V}_{\text{CC}} - 0.2\text{V}, \text{V}_{\text{IN}} \leqq 0.2\text{V} \\ \text{or } \text{V}_{\text{IN}} \geqq \text{V}_{\text{CC}} - 0.2\text{V} \end{split}$ | I <sub>SB1</sub> |     | 0.5 | 15  | mA   |

| Standby Supply Current        | $\overline{\text{CS}} = V_{1\text{H}}$                                                                                                                                                                                   | I <sub>SB2</sub> |     | 10  | 25  | mA   |

| Output Low Voltage            | I <sub>OL</sub> = 8 mA                                                                                                                                                                                                   | V <sub>OL</sub>  |     |     | 0.4 | v    |

| Output High Voltage           | I <sub>ОН</sub> = -4 mA                                                                                                                                                                                                  | V <sub>он</sub>  | 2.4 |     |     | v    |

|         | MB81C68A-25 |

|---------|-------------|

| FUJITSU | MB81C68A-30 |

|         | MB81C68A-35 |

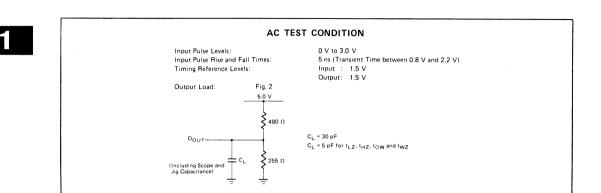

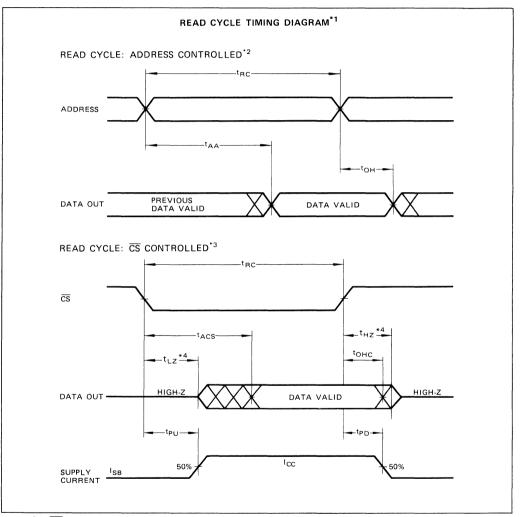

# AC CHARACTERISTICS (Recommended operating conditions unless otherwise noted.)

READ CYCLE\*1

| Parameter                                          | Cumb al          | MB 81C68A-25 |     | MB 81C68A-30 |     | MB 81C68A-35 |     |      |

|----------------------------------------------------|------------------|--------------|-----|--------------|-----|--------------|-----|------|

| Parameter                                          | Symbol           | Min          | Max | Min          | Max | Min          | Max | Unit |

| Read Cycle Time                                    | t <sub>RC</sub>  | 25           |     | 30           |     | 35           |     | ns   |

| Address Access Time*2                              | t <sub>AA</sub>  |              | 25  |              | 30  |              | 35  | ns   |

| Chip Select Access Time <sup>*3</sup>              | t <sub>ACS</sub> |              | 25  |              | 30  |              | 35  | ns   |

| Output Hold from Address Change                    | t <sub>он</sub>  | 3            |     | 3            |     | 3            |     | ns   |

| Output Hold from CS                                | t <sub>онс</sub> | 0            |     | 0            |     | 0            |     | ns   |

| Chip Selection to Output in Low-Z*4                | t <sub>LZ</sub>  | 5            |     | 5            |     | 5            |     | ns   |

| Chip Deselection to Output in High-Z <sup>*4</sup> | t <sub>HZ</sub>  |              | 10  |              | 13  |              | 15  | ns   |

| Power Up from CS                                   | t <sub>PU</sub>  | 0            |     | 0            |     | 0            |     | ns   |

| Power Down from CS                                 | t <sub>PD</sub>  |              | 20  |              | 25  |              | 30  | ns   |

Note:

\*1

$\overline{WE}$  is high for Read cycle.

\*2

Device is continuously selected,  $\overline{CS} = V_{1L}$

\*3

Address valid prior to or coincident with  $\overline{CS}$  transition low.

\*4 Transition is specified at the point of ±500 mV from steady state voltage.

| MB81C68A-25 |         |

|-------------|---------|

| MB81C68A-30 | FUJITSU |

| MB81C68A-35 |         |

Note: \*1 WE is high for Read cycle.

- 2 Device is continuously selected, CS = V<sub>IL</sub>

3 Address valid prior to or coincident with CS transition low.

\*4 Transition is specified at the point of ±500 mV from steady state voltage.

|         | MB81C68A-25 |

|---------|-------------|

| FUJITSU | MB81C68A-30 |

|         | MB81C68A-35 |

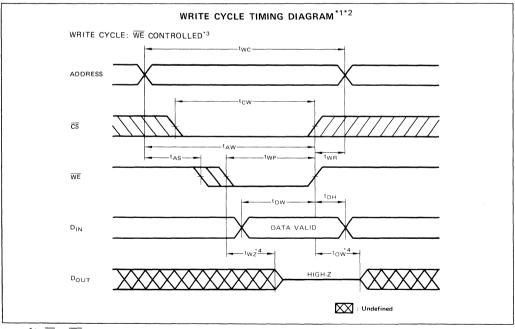

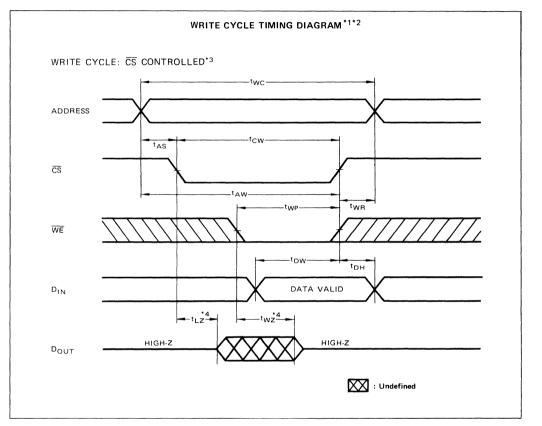

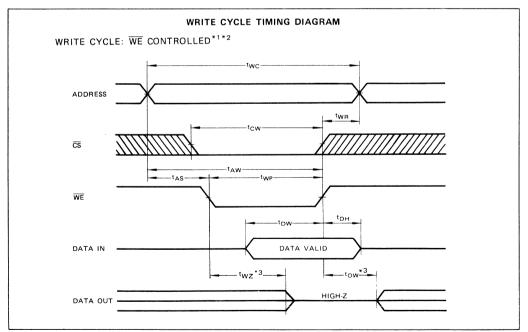

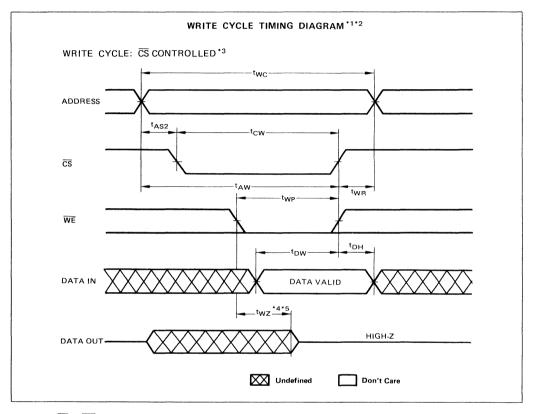

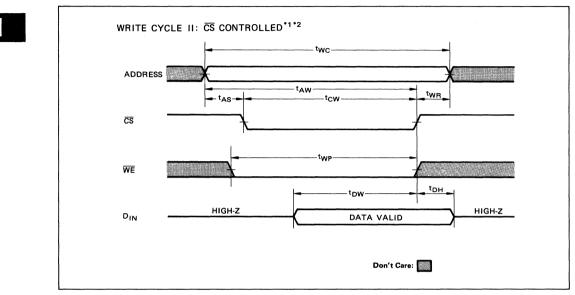

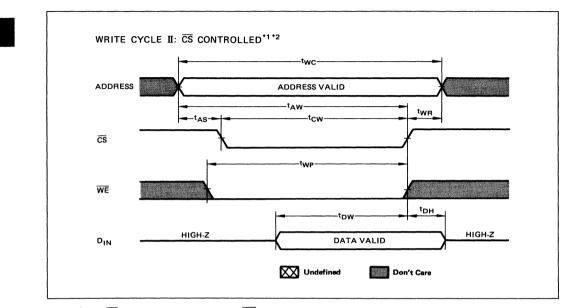

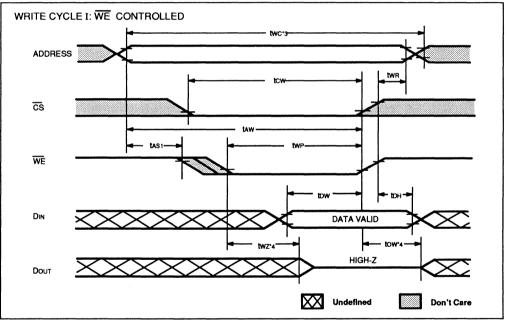

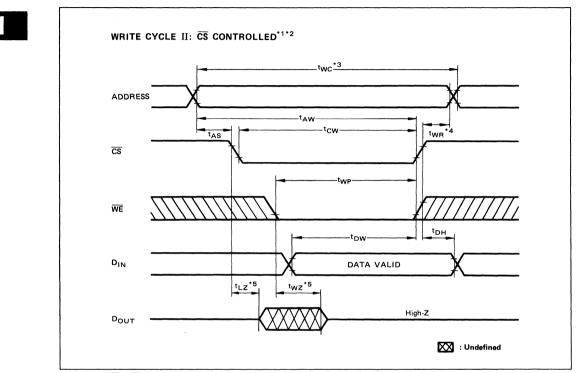

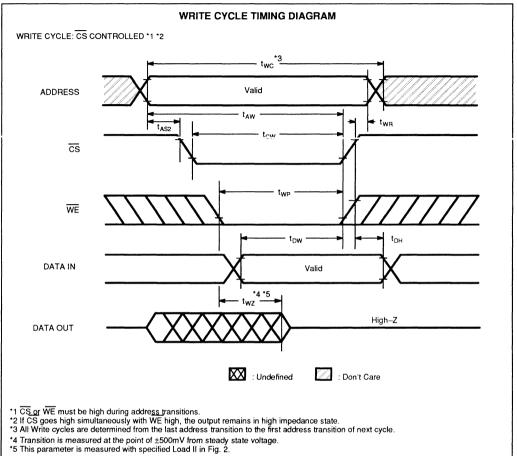

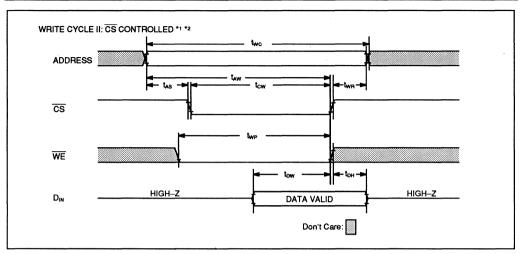

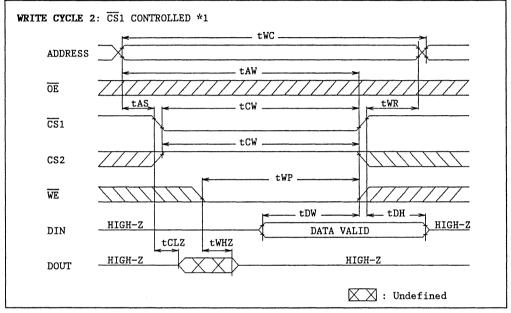

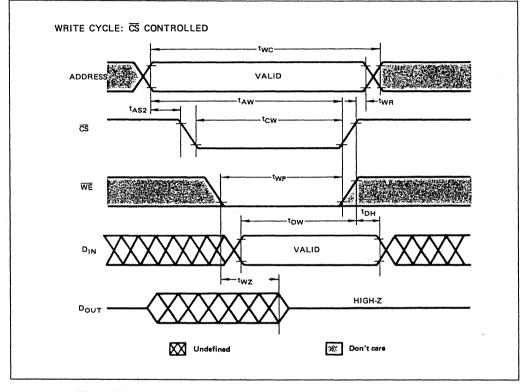

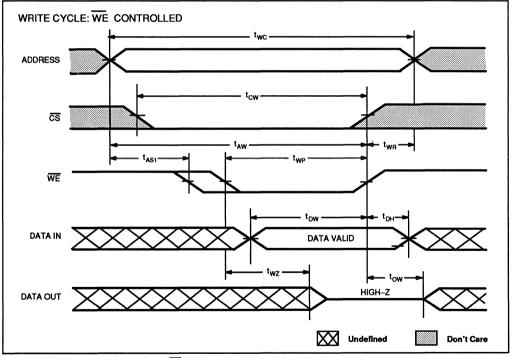

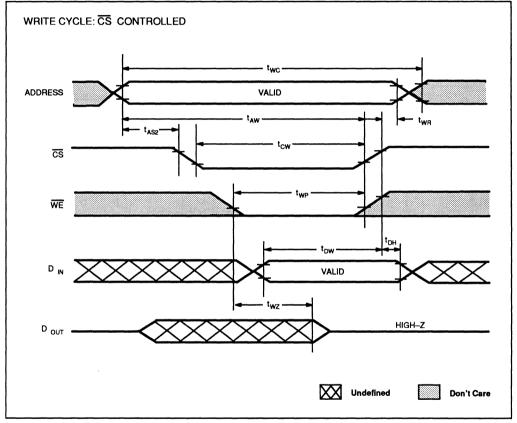

### WRITE CYCLE\*1\*2

|                                        | Guntal          | MB 81C68A-25 |     | MB 81C68A-30 |     | MB 81C68A-35 |     |      |

|----------------------------------------|-----------------|--------------|-----|--------------|-----|--------------|-----|------|

| Parameter                              | Symbol          | Min          | Max | Min          | Max | Min          | Max | Unit |

| Write Cycle Time                       | twc             | 25           |     | 30           |     | 35           |     | ns   |

| Chip Selection to End of Write         | t <sub>cw</sub> | 20           |     | 25           |     | 30           |     | ns   |

| Address Valid to End of Write          | t <sub>AW</sub> | 20           |     | 25           |     | 30           |     | ns   |

| Address Setup Time                     | t <sub>AS</sub> | 0            |     | 0            |     | 0            |     | ns   |

| Write Pulse Width                      | twp             | 20           |     | 25           |     | 30           |     | ns   |

| Data Setup Time                        | t <sub>DW</sub> | 13           |     | 15           |     | 15           |     | ns   |

| Write Recovery Time                    | t <sub>wR</sub> | 2            |     | 2            |     | 2            |     | ns   |

| Data Hold Time                         | t <sub>DH</sub> | 0            |     | 0            |     | 0            |     | ns   |

| Output High-Z from WE*3                | t <sub>wz</sub> |              | 10  |              | 13  |              | 15  | ns   |

| Output Low-Z from $\overline{WE}^{*3}$ | tow             | 5            |     | 5            |     | 5            |     | ns   |

\*2 If  $\overline{CS}$  goes high simultaneously with  $\overline{WE}$  high, the output remains in a high impedance state. \*3 Transition is specified at the point of ±500 mV from steady state voltage.

| MB81C68A-25 |         |

|-------------|---------|

| MB81C68A-30 | FUJITSU |

| MB81C68A-35 |         |

Note: \*1  $\overline{CS}$  or  $\overline{WE}$  must be high during address transitions.

\*2 If  $\overline{CS}$  goes high simultaneously with  $\overline{WE}$  high, the output remains in a high impedance state.

\*3 Transition is specified at the point of  $\pm 500$  mV from steady state voltage.

|         | MB 81C68A-25 |

|---------|--------------|

| FUJITSU | MB 81C68A-30 |

|         | MB81C68A-35  |

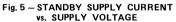

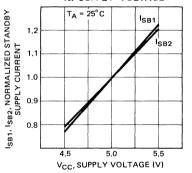

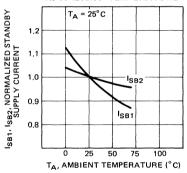

### **TYPICAL CHARACTERISTICS CURVES**

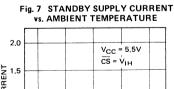

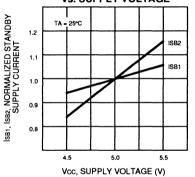

Fig. 5 STANDBY SUPPLY CURRENT vs. SUPPLY VOLTAGE

TA, AMBIENT TEMPERATURE (°C)

Fig. 6 STANDBY SUPPLY CURRENT vs. AMBIENT TEMPERATURE

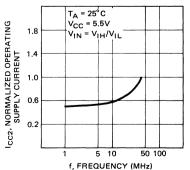

Fig. 8 OPERATING SUPPLY CURRENT vs. FREQUENCY

| MB81C68A-25 |         |

|-------------|---------|

| MB81C68A-30 | FUJITSU |

| MB81C68A-35 |         |

### TYPICAL CHARACTERISTICS CURVES (Cont'd)

Fig. 12 ACCESS TIME vs. AMBIENT TEMPERATURE

|         | MB81C68A-25 |

|---------|-------------|

| FUJITSU | MB81C68A-30 |

|         | MB81C68A-35 |

(Suffix: -Z)

| MB81C68A-25 |         |

|-------------|---------|

| MB81C68A-30 | FUJITSU |

| MB81C68A-35 |         |

(Suffix: -PSZ)

5

|         | MB81C68A-25 |

|---------|-------------|

| FUJITSU | MB81C68A-30 |

|         | MB81C68A-35 |

# CMOS 16384-BIT STATIC RANDOM ACCESS MEMORY

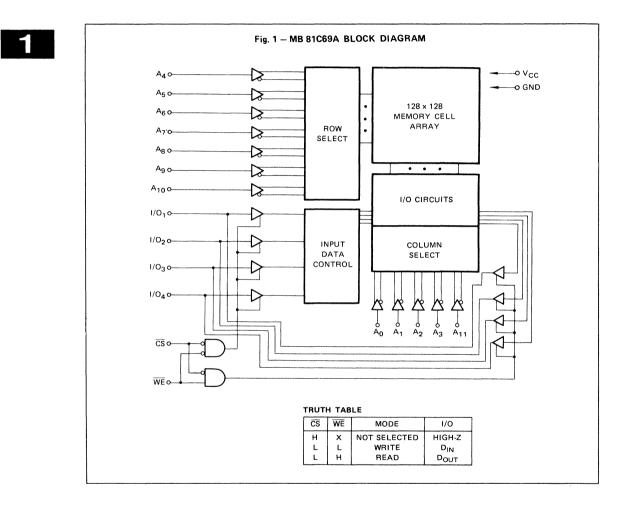

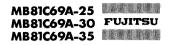

#### MB81C69A-25 MB81C69A-30 MB81C69A-35

January 1988 Edition 2.0

#### 4K x 4 (16,384-BIT) STATIC RANDOM ACCESS MEMORY WITH SUPPER HIGH SPEED

The Fujitsu MB 81C69A is 4096 words x 4 bits static random access memory fabricated with a CMOS silicon gate process. The memory utilizes asynchronous circuitry and all pins are TTL compatible and a single 5 volts power supply is required.

A separate chip select ( $\overline{CS}$ ) pin simplifies multipackage systems design. It permits the selection of an individual package when outputs are OR-tied.

All devices offer the advantages of low power dissipation, low cost, and high performance.

- Organization: 4096 words x 4 bits

- Static operation: No clocks or timing strobe required

- Fast access time:  $t_{AA}$  = 25 ns max,  $t_{ACS}$  = 15 ns max (MB 81C69A-25)  $t_{AA}$  = 30 ns max,  $t_{ACS}$  = 18 ns max (MB 81C69A-30)

- $t_{AA} = 35 \text{ ns max}, t_{ACS} = 20 \text{ ns max} (MB 81C69A-35)$

- Low power consumption: 385 mW max. (Active)

- Single +5V supply ±10% tolerance

- TTL compatible inputs and outputs

- Three-state outputs with OR-tie capability

- Chip select for simplified memory expansion

- All inputs and outputs have protection against static charge

- Standard 20-pin DIP (Suffix: -P(plastic)/Suffix: -Z(cerdip))

- Standard 20-pad LCC (Suffix: -TV)

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating                                        | Symbol            | Value            | Unit        |    |

|-----------------------------------------------|-------------------|------------------|-------------|----|

| Supply Voltage                                |                   | V <sub>cc</sub>  | -0.5 to +7  | V  |

| Input Voltage on Any P<br>with respect to GND | V <sub>IN</sub>   | -3.5 to +7       | V           |    |

| Output Volage on Any I<br>with respect to GND | V <sub>out</sub>  | -0.5 to +7       | V           |    |

| Output current                                | Output current    |                  |             | mA |

| Power dissipation                             | Power dissipation |                  |             | W  |

| Temperature under Bias                        | TBIAS             | -10 to +85       | °C          |    |

| Storage Temperature                           | CERAMIC           | т                | -65 to +150 | °C |

| Storage remperature                           | PLASTIC           | Τ <sub>STG</sub> | -45 to +125 | L  |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

|         | MB81C69A-25 |

|---------|-------------|

| FUJITSU | MB81C69A-30 |

|         | MB81C69A-35 |

#### CAPACITANCE (T<sub>A</sub> = 25°C, f = 1 MHz)

| Parameter                                           | Symbol           | Тур | Max | Unit |

|-----------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (V <sub>IN</sub> = 0 V)           | C <sub>IN</sub>  |     | 5   | pF   |

| $\overline{CS}$ Capacitance (V <sub>CS</sub> = 0 V) | Ccs              |     | 6   | pF   |

| I/O Capacitance (V <sub>I/O</sub> = 0 V)            | C <sub>I/O</sub> |     | 7   | pF   |

### **RECOMMENDED OPERATING CONDITIONS**

(Referenced to GND)

| Parameter           | Symbol          | Min   | Тур | Max | Unit |

|---------------------|-----------------|-------|-----|-----|------|

| Supply Voltage      | V <sub>cc</sub> | 4.5   | 5.0 | 5.5 | v    |

| Input Low Voltage   | V <sub>IL</sub> | -2.0* |     | 0.8 | v    |

| Input High Voltage  | V <sub>IH</sub> | 2.2   |     | 6.0 | v    |

| Ambient Temperature | T <sub>A</sub>  | 0     |     | 70  | °C   |

Note: \* -2.0 V Min. for pulse width less than 20 ns. ( $V_{IL}$  Min. = -0.5 V at DC level)

# DC CHARACTERISTICS (Recommended operating conditions unless otherwise noted.)

| Parameter                | Test Condition                                                                                    | Symbol           | Min | Тур | Max | Unit |

|--------------------------|---------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Input Leakage Current    | $V_{IN} = 0V$ to $V_{CC}$                                                                         | l <sub>L1</sub>  | -10 |     | 10  | μA   |

| Output Leakage Current   | $\overline{\text{CS}} = \text{V}_{1\text{H}}, \text{V}_{1/\text{O}} = 0\text{V to V}_{\text{CC}}$ | I <sub>LO</sub>  | -10 |     | 10  | μA   |

| Active Supply Current    | $\overline{CS} = V_{1L},$ $I_{OUT} = 0 \text{ mA}$ $V_{1N} = V_{1L} \text{ or } V_{1H}$           | I <sub>CC1</sub> |     | 25  | 50  | mA   |

| Operating Supply Current | <del>CS</del> = V <sub>IL</sub><br>Ι <sub>Ουτ</sub> = 0 mA, Cycle = Min                           | I <sub>CC2</sub> |     | 40  | 70  | mA   |

| Output Low Voltage       | I <sub>OL</sub> = 8 mA                                                                            | V <sub>ol</sub>  |     |     | 0.4 | v    |

| Output High Voltage      | I <sub>ОН</sub> = -4 mA                                                                           | V <sub>он</sub>  | 2.4 |     |     | v    |

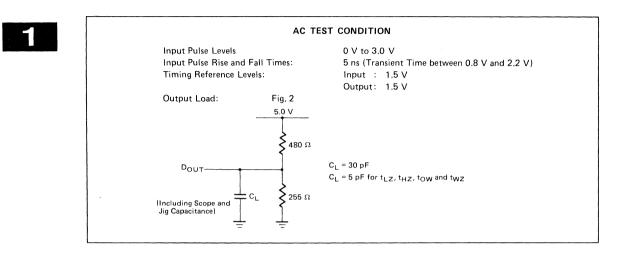

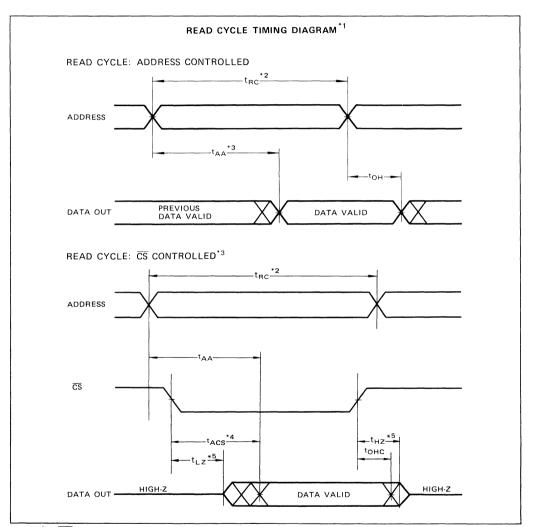

#### **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

**READ CYCLE\*1**

| Parameter                                          | Cumb al          | MB 81C69A-25 |     | MB 81C69A-30 |     | MB 81C69A-35 |     |      |

|----------------------------------------------------|------------------|--------------|-----|--------------|-----|--------------|-----|------|

| Farameter                                          | Symbol           | Min          | Max | Min          | Max | Min          | Max | Unit |

| Read Cycle Time <sup>*2</sup>                      | t <sub>RC</sub>  | 25           |     | 30           |     | 35           |     | ns   |

| Address Access Time <sup>*3</sup>                  | t <sub>AA</sub>  |              | 25  |              | 30  |              | 35  | ns   |

| Chip Select Access Time <sup>*4</sup>              | t <sub>ACS</sub> |              | 15  |              | 18  |              | 20  | ns   |

| Output Hold from Address Change                    | t <sub>он</sub>  | 3            |     | 3            |     | 3            |     | ns   |

| Output Hold from $\overline{CS}$                   | <sup>t</sup> онс | 0            |     | 0            |     | 0            |     | ns   |

| Chip Selection to Output in Low-Z <sup>*5</sup>    | t <sub>LZ</sub>  | 0            |     | 0            |     | 0            |     | ns   |

| Chip Deselection to Output in High-Z <sup>*5</sup> | t <sub>HZ</sub>  |              | 10  |              | 13  |              | 15  | ns   |

Note: \*1 WE is high for Raed cycle. \*2 All read cycles are determined from the last address transition to the first address transition of next cycle.

\*3 Device is continuously selected,  $\overline{CS} = V_{|L}$ . \*4 Address valid prior to or coincident with  $\overline{CS}$  transition low.

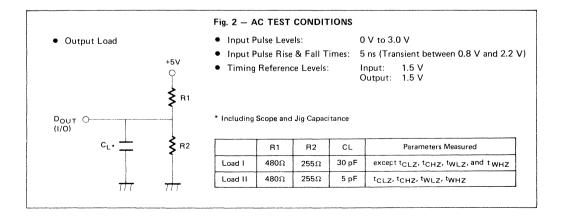

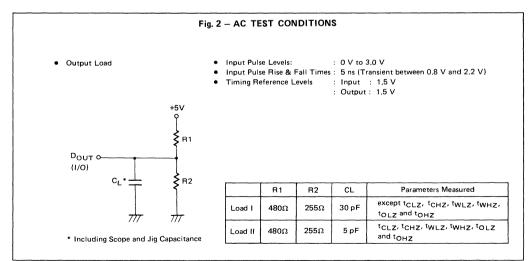

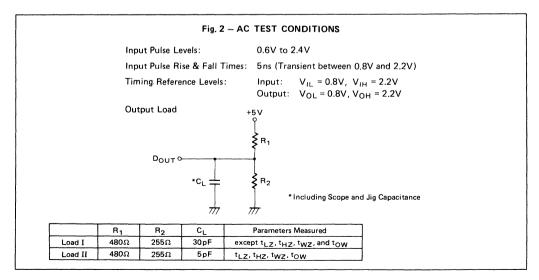

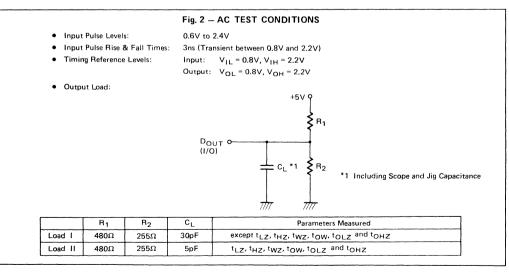

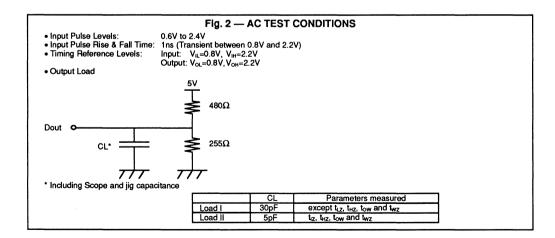

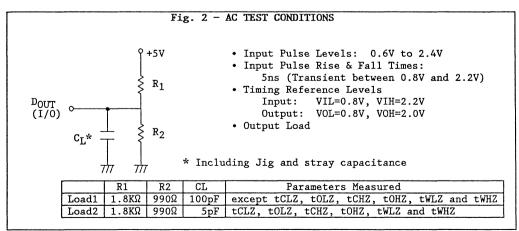

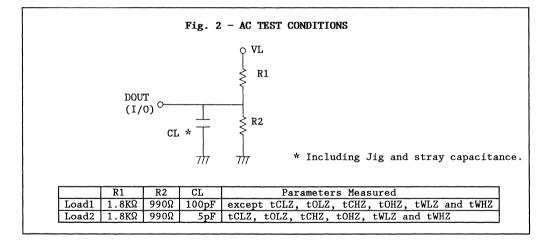

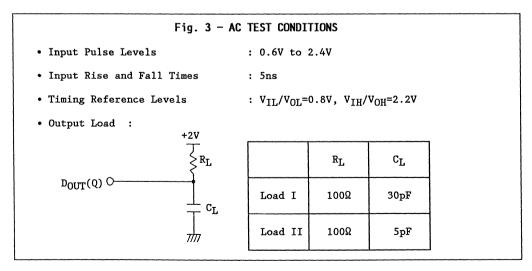

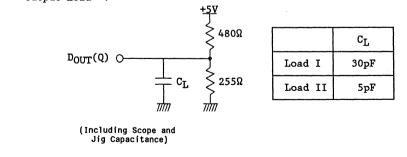

\*5 Transition is specified at the point of  $\pm 500 \text{mV}$  from steady state Voltage with Load II in Fig. 2.

MB81C69A-25 MB81C69A-30 FUJITSU MB81C69A-35

\*1 WE is high for Read cycle. Note:

- \*2 All read cycles are determined from the last address transition to the first address transition of next cycle.

- \*3 Device is continuously selected,  $\overline{CS} = V_{1L}$ . \*4 Address valid prior to or coincident with  $\overline{CS}$  transition low.

- \*5 Transition is specified at the point of ±500 mV from steady state voltage with Lead II in Fig. 2.

|         | MB81C69A-25 |

|---------|-------------|

| FUJITSU | MB81C69A-30 |

|         | MB81C69A-35 |

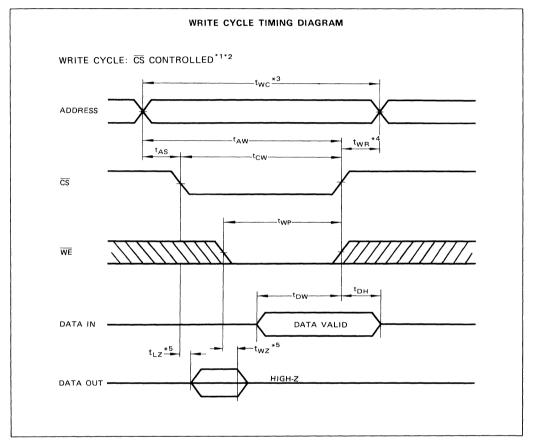

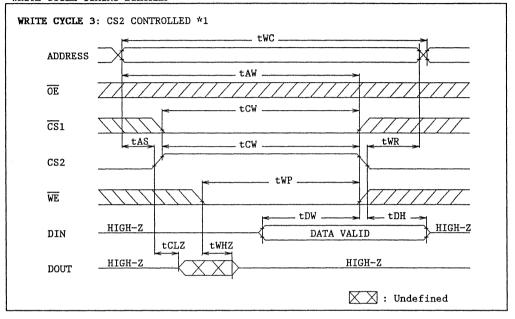

#### WRITE CYCLE \*1\*2

| Parameter                      | Cumhal          | MB 810 | C69A-25 | MB 810 | C69A-30 | MB 81 | C69A-35 |      |

|--------------------------------|-----------------|--------|---------|--------|---------|-------|---------|------|

| Carameter                      | Symbol          | Min    | Max     | Min    | Max     | Min   | Max     | Unit |

| Write Cycle Time <sup>*3</sup> | twc             | 25     |         | 30     |         | 35    |         | ns   |

| Chip Selection to End of Write | tcw             | 20     |         | 25     |         | 30    |         | ns   |

| Address Valid to End of Write  | t <sub>AW</sub> | 20     |         | 25     |         | 30    |         | ns   |

| Address Setup Time             | t <sub>AS</sub> | 0      |         | 0      |         | 0     |         | ns   |

| Write Pulse Width              | t <sub>wP</sub> | 20     |         | 25     |         | 30    |         | ns   |

| Data Setup Time                | t <sub>DW</sub> | 13     |         | 15     |         | 15    |         | ns   |

| Write Recovery Time *4         | twR             | 2      |         | 2      |         | 2     |         | ns   |

| Data Hold Time                 | t <sub>DH</sub> | 0      |         | 0      |         | 0     |         | ns   |

| Output High-Z from WE*5        | t <sub>wz</sub> |        | 10      |        | 13      |       | 15      | ns   |

| Output Low-Z from WE*5         | tow             | 5      |         | 5      |         | 5     |         | ns   |

Note: \*1 If CS are in the READ Mode during this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

\*2 If  $\overline{CS}$  goes high simulatneously with  $\overline{WE}$  high, the output remains in high impedance state.

\*3 All write cycle are determined from last address transition to the first address transition of the next address.

\*4  $t_{WR}$  is defined from the end point of WRITE Mode.

\*5 Transition is specified at the point of  $\pm$ 500mV from steady state voltage, with Load II in Fig. 2.

| MB81C69A-25 |         |

|-------------|---------|

| MB81C69A-30 | FUJITSU |

| MB81C69A-35 |         |

Note: \*1 If CS are in the READ Mode during this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

\*2 If  $\overline{CS}$  goes high simultaneously with  $\overline{WE}$  high, the output remains in high impedance state.

\*3 All write cycle are determined from last address transition to the first address transition of the next address.

- \*4  $t_{WB}$  is defined from the end point of WRITE Mode.

- \*5 Transition is specified at the point of ±500mV from steady state voltage with Load II in Fig. 2.

### **TYPICAL CHARACTERISTICS CURVES**

| MB81C69A-25 |         |

|-------------|---------|

| MB81C69A-30 | FUJITSU |

| MB81C69A-35 |         |

CERAMIC DIP (Suffix: -Z)

5

|         | MB81C69A-25 |

|---------|-------------|

| FUJITSU | MB81C69A-30 |

|         | MB81C69A-35 |

PLASTIC DIP (Suffix: -P)

| MB81C69A-25 |         |

|-------------|---------|

| MB81C69A-30 | FUJITSU |

| MB81C69A-35 |         |

CERAMIC LCC (Suffix: -TV)

# CMOS 65,536-BIT STATIC RANDOM ACCESS MEMORY

# MB81C71A-25 MB81C71A-35

February 1988 Edition 2.0

#### 65,536 WORDS X 1 BIT HIGH SPEED CMOS STATIC RANDOM ACCESS MEMORY

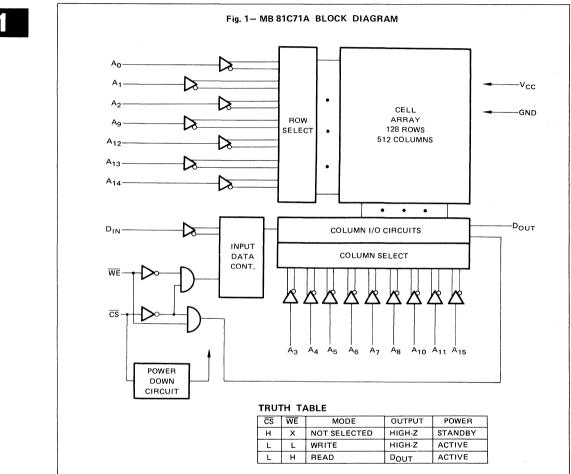

The Fujitsu MB 81C71A is 65,536 words x 1 bit static random access memory fabricated with a CMOS technology.

It uses fully static circuitry throughout and therefore requires no clocks or refreshing to operate.

The MB 81C71A is designed for memory applications where high performance, low cost, large bit storage and simple interfacing are required.

MB 81C71A is compatible with TTL logic families in all respects; input, output and a single +5 V supply.

- Organization : 65,536 words x 1 bit

- Static operation : No clocks or refresh required

- Fast access time :  $t_{AA} = t_{ACS} = 25$  ns (MB 81C71A-25)  $t_{AA} = t_{ACS} = 35$  ns (MB 81C71A-35)

- Single +5 V supply ±10% tolerance

- Separate data input and output

- TTL compatible inputs and output

- Three-state output with OR-tie capability

- · Chip select for simplified memory expansion, automatic power down

- All inputs and output have protection against static charge

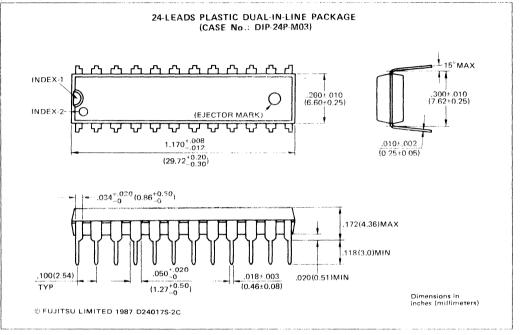

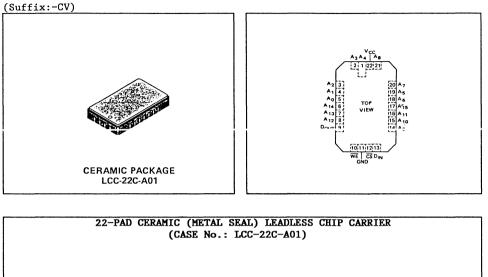

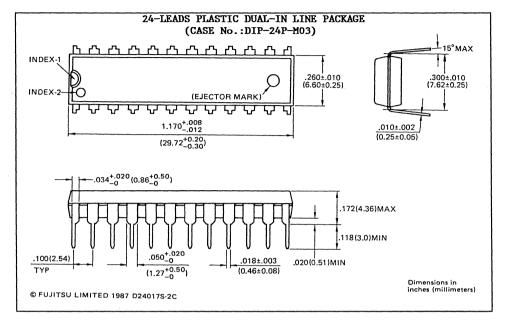

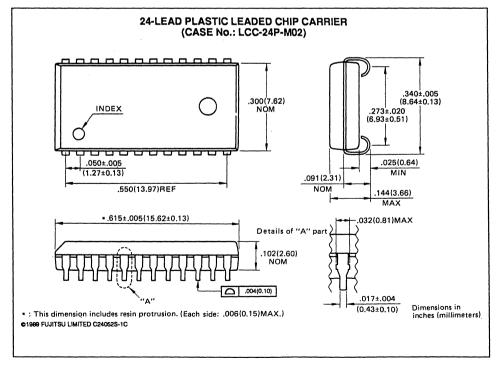

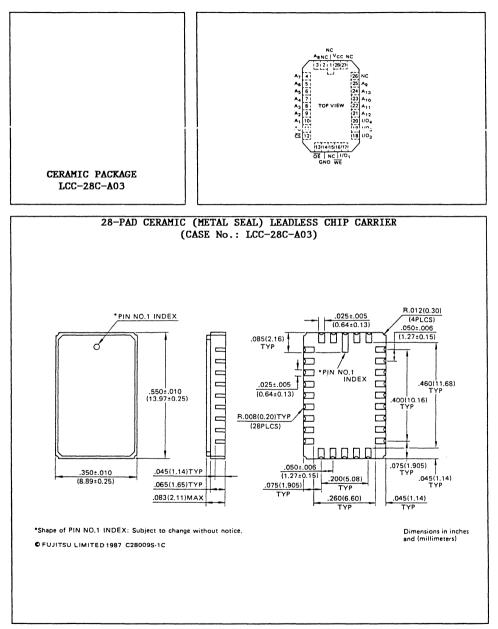

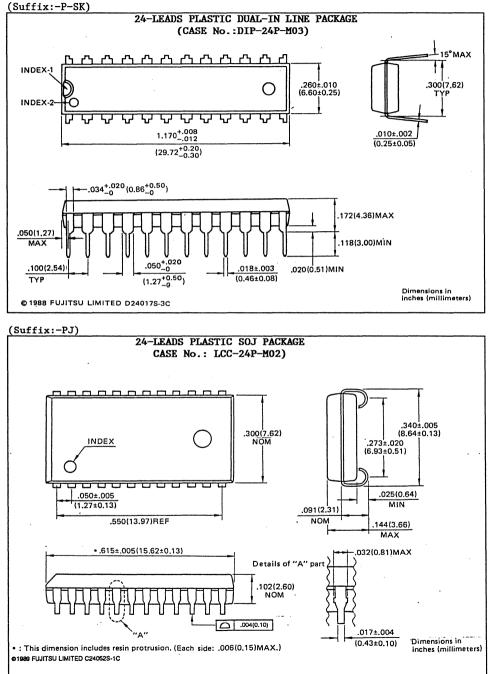

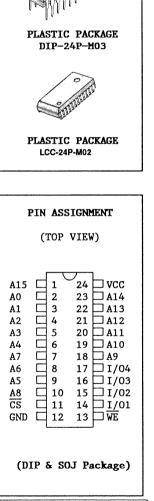

- Standard 22-pin DIP (300 mil) (Suffix: P)

- Standard 22-pad LCC (Suffix: CV)

- Standard 24-pin SOJ (300 mil) : (Suffix : PJ)

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating                                           |         | Symbol            | Value       | Unit |

|--------------------------------------------------|---------|-------------------|-------------|------|

| Supply Voltage                                   |         | V <sub>cc</sub>   | -0.5 to +7  | V    |

| Input Voltage on any pin<br>with respect to GND  |         | V <sub>IN</sub>   | -3.5 to +7  | v    |

| Output Voltage on any pin<br>with respect to GND |         | Vout              | -0.5 to +7  | V    |

| Output Current                                   |         | lout              | ±50         | mA   |

| Power Dissipation                                |         | PD                | 1.0         | w    |

| Temperature Under Bias                           |         | T <sub>BIAS</sub> | - 10 to +85 | °C   |

| Storage                                          | Ceramic | т                 | -65 to +150 | °c   |

| Temperature                                      | Plastic | Т <sub>STG</sub>  | -45 to +125 | C    |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### CAPACITANCE (T<sub>A</sub> = 25°C, f = 1 MHz)

| Parameter                                           | Sumb al         | Va  | Unit |    |  |

|-----------------------------------------------------|-----------------|-----|------|----|--|

| Parameter                                           | Symbol          | Тур | Ma×  |    |  |

| Input Capacitance (V <sub>IN</sub> = 0 V)           | C <sub>IN</sub> |     | 7    | pF |  |

| $\overline{CS}$ Capacitance (V <sub>CS</sub> = 0 V) | C <sub>CS</sub> |     | 7    | pF |  |

| Output Capacitance (V <sub>OUT</sub> = 0 V)         | Cout            |     | 7    | pF |  |

### **RECOMMENDED OPERATING CONDITIONS**

(Referenced to GND)

| Parameter           | Symbol          |       | Unit |     |      |

|---------------------|-----------------|-------|------|-----|------|

| Falaneter           |                 | Min   | Тур  | Max | Unit |

| Supply Voltage      | V <sub>cc</sub> | 4.5   | 5.0  | 5.5 | V    |

| Input Low Voltage   | V <sub>IL</sub> | -2.0* |      | 0.8 | V    |

| Input High Voltage  | V <sub>IH</sub> | 2.2   |      | 6.0 | V    |

| Ambient Temperature | TA              | 0     |      | 70  | °C   |

$^{*}$  -2.0 V Min, for pulse width less than 20 ns. (V\_{1L} Min = -0.5 V at DC Level )

#### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| <b>D</b>                 | Parameter Test Condition                                                                                                                                                       |                  | Value |     |      |      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-----|------|------|

| Parameter                |                                                                                                                                                                                | Symbol           | Min   | Тур | Max  | Unit |

| Input Leakage Current    | $V_{IN} = 0 V \text{ to } V_{CC}$<br>$V_{CC} = Max.$                                                                                                                           | ار،              | - 10  |     | 10   | μΑ   |

| Output Leakage Current   | $\overline{CS} = V_{IH},$<br>$V_{OUT} = 0 V \text{ to } 4.5 V$<br>$V_{CC} = Max.$                                                                                              | I <sub>LO</sub>  | - 10  |     | 10   | μΑ   |

| Operating Supply Current | $\overline{CS} = V_{IL}, V_{CC} = Max.$<br>$D_{OUT} = Open,$<br>Cycle = Min.                                                                                                   | I <sub>cc</sub>  |       |     | 80   | mA   |

| Standby Current          | $\begin{array}{l} V_{CC} = \text{Min. to Max.} \\ \overline{CS} \geq V_{CC} - 0.2 \text{ V} \\ V_{IN} \leq 0.2 \text{ V or} \\ V_{IN} \geq V_{CC} - 0.2 \text{ V} \end{array}$ | I <sub>SB1</sub> |       |     | 10   | mA   |

| Standby Current          | V <sub>CC</sub> = Min. to Max.<br>CS = V <sub>IH</sub>                                                                                                                         | I <sub>SB2</sub> |       |     | 20   | mA   |

| Output Low Voltage       | I <sub>OL</sub> = 16 mA                                                                                                                                                        | Vol              |       |     | 0.45 | v    |

| Output High Voltage      | I <sub>ОН</sub> = -4 mA                                                                                                                                                        | V <sub>он</sub>  | 2.4   |     |      | v    |

| Peak Power on Current    | $V_{CC} = 0 V$ to $V_{CC}$ Min.<br>$\overline{CS} = Lower of V_{CC} or$<br>$V_{IH}$ Min.                                                                                       | IPO              |       |     | 30   | mA   |

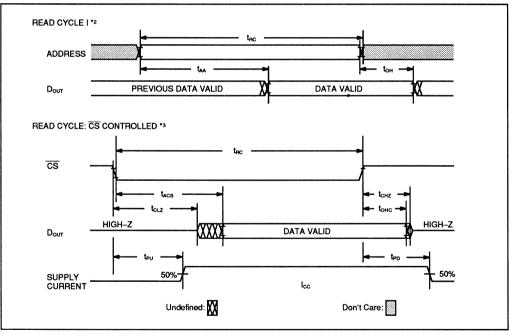

#### AC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.) READ CYCLE\*1

| Parameter                                            | Symbol           | MB 81C71A-25 |     | MB 81C71A-35 |     | 11-1-1- |

|------------------------------------------------------|------------------|--------------|-----|--------------|-----|---------|

| Faranteter                                           | Symbol           | Min          | Max | Min          | Max | Unit    |

| Read Cycle Time <sup>*2</sup>                        | t <sub>RC</sub>  | 25           |     | 35           |     | ns      |

| Address Access Time *3                               | t <sub>AA</sub>  |              | 25  |              | 35  | ns      |

| Chip Select Access Time *4 *5                        | t <sub>ACS</sub> |              | 25  |              | 35  | ns      |

| Output Hold from Address Change                      | t <sub>он</sub>  | 5            |     | 5            |     | ns      |

| Chip Selection to Output in Low-Z <sup>*6*7</sup>    | t <sub>LZ</sub>  | 5            |     | 5            |     | ns      |

| Chip Deselection to Output in High-Z <sup>*6*7</sup> | t <sub>HZ</sub>  | 0            | 10  | 0            | 15  | ns      |

| Chip Selection to Power Up Time                      | t <sub>PU</sub>  | 0            |     | 0            |     | ns      |

| Chip Deselction to Power Down time                   | t <sub>PD</sub>  |              | 20  |              | 30  | ns      |

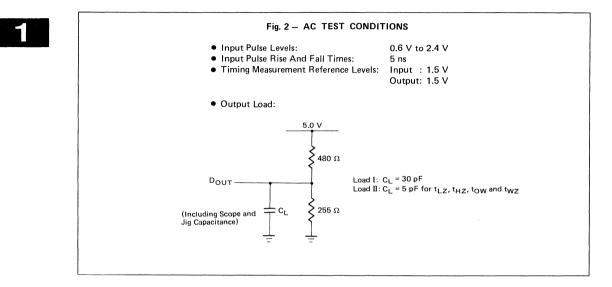

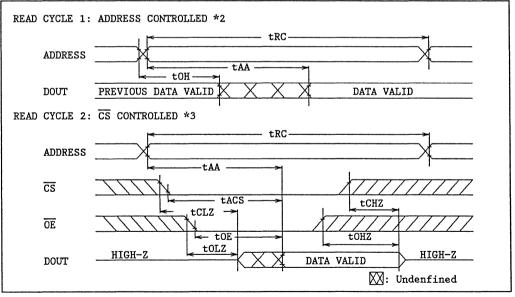

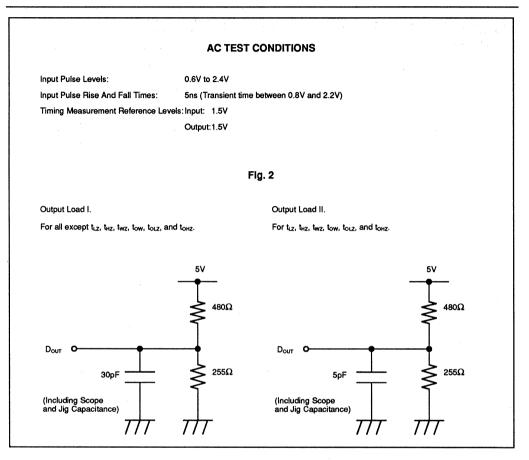

Note: \*1 WE is high for Read cycle.

\*2 All Read cycles are determined from the last address transition to the first address transition of next cycle.

- \*3 Device is continuously selected,  $\overline{CS} = V_{1L}$ . \*4 Address valid prior to or coincident with  $\overline{CS}$  transition low.

- \*5 Chip deselection for a finite time is less than  $t_{RC}$  prior to selection.

- \*6 Transition is measured at the point of  $\pm$ 500mV from steady state voltage.

- \*7 This parameter is measured with specified loading Load II in Fig. 2.

| MB81C71A-25<br>MB81C71A-35 | FUJITSU |

|----------------------------|---------|

- Note: \*1 WE is high for Read cycle.

- \*2 All Read cycles are determined from the last address transition to the first address transition of next cycle.

- \*3 Device is continuously selected,  $CS = V_{1,L}$ . \*4 Address valid prior to or coincident with CS transition low.

- \*5 Chip deselection for a finite time is less than  $t_{\text{RC}}$  prior to selection.

- \*6 Transition is measured at the point of  $\pm$ 500mV from steady state voltage.

- \*7 This parameter is measured with specified loading Load II in Fig. 2.

1 - 43

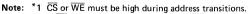

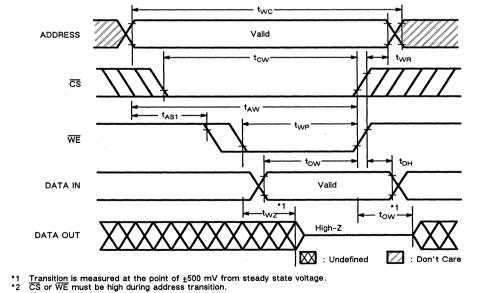

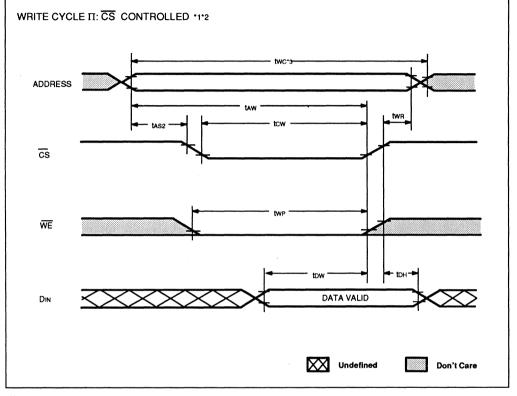

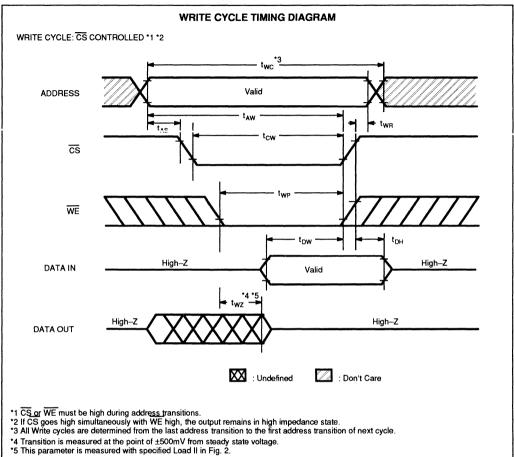

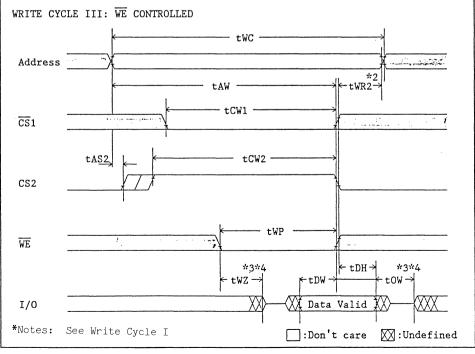

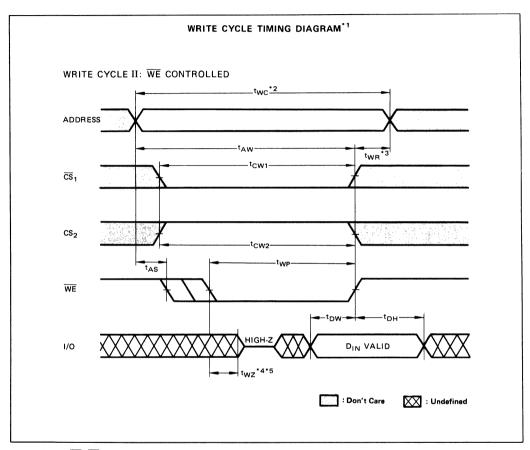

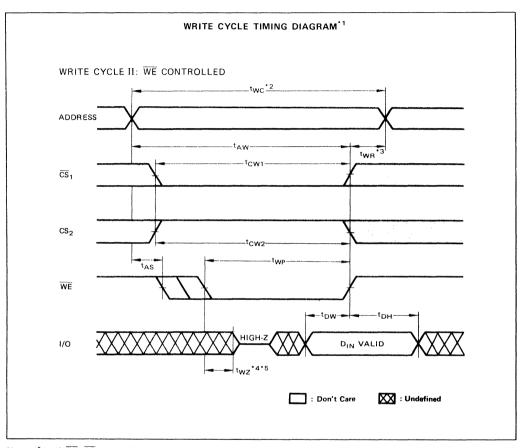

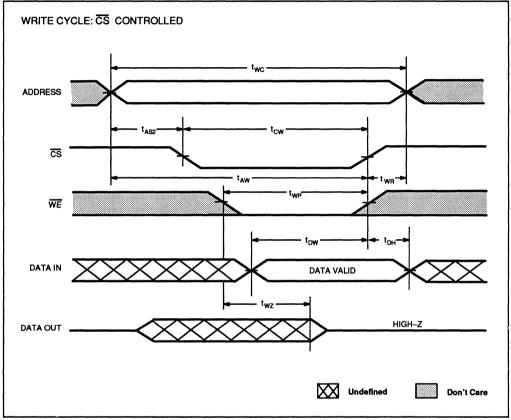

#### WRITE CYCLE\*1\*2

| Parameter                            | Question         | MB 81C71A-25 |     | MB 81C71A-35 |     |      |

|--------------------------------------|------------------|--------------|-----|--------------|-----|------|

| Parameter                            | Symbol           | Min          | Max | Min          | Max | Unit |

| Write Cycle Time <sup>*3</sup>       | twc              | 25           |     | 35           |     | ns   |

| Chip Selection to End of Write       | tcw              | 20           |     | 30           |     | ns   |

| Address Valid to End of Write        | t <sub>AW</sub>  | 20           |     | 30           |     | ns   |

| Address Setup Time                   | t <sub>AS1</sub> | 0            |     | 0            |     | ns   |

| Address Setup Time                   | t <sub>AS2</sub> | 0            |     | 0            |     | ns   |

| Write Pulse Width                    | t <sub>WP</sub>  | 20           |     | 30           |     | ns   |

| Data Valid to End of Write           | t <sub>DW</sub>  | 15           |     | 20           |     | ns   |

| Write Recovery Time                  | twr              | 2            |     | 2            |     | ns   |

| Data Hold Time                       | t <sub>DH</sub>  | 2            |     | 2            |     | ns   |

| Write Enable to Output in High-Z*4*5 | t <sub>wz</sub>  | 0            | 10  | 0            | 15  | ns   |

| Output Active from End of Write *4*5 | tow              | 0            |     | 0            |     | ns   |

- 2 If CS goes high simultaneously with WE high, the output remains in high impedance state.

3 All Write cycles are determined from the last address transition to the first address transition of next cycle.

- \*4 Transition is measured at the point of ±500mV from steady state voltage.

- \*5 This parameter is measured with specified Load II in Fig. 2.

| MB81C71A-25<br>MB81C71A-35 | FUJITSU |

|----------------------------|---------|

| MBBIC/IA-35                |         |

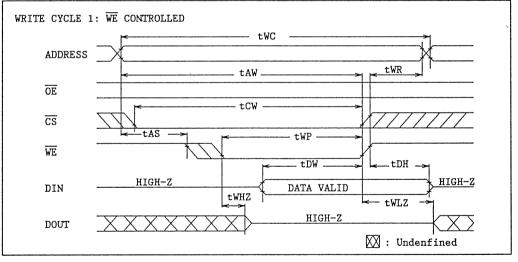

Note: \*1  $\overline{CS}$  or  $\overline{WE}$  must be high during address transitions.

- \*2 If CS goes high simultaneously with WE high, the output remains in high impedance state.

- \*3 All Write cycles are determined from the last address transition to the first address transition of next cycle.

\*4 Transition is measured at the point of ±500mV from steady state voltage.

- \*5 This parameter is measured with specified Load II in Fig. 2.

| FUJITSU | MB81C71A-25<br>MB81C71A-35 |

|---------|----------------------------|

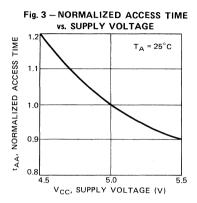

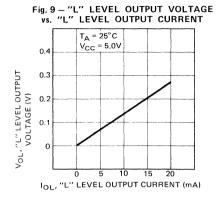

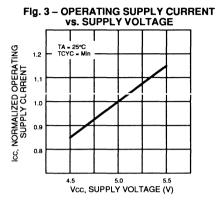

0.8

45

5.0

V<sub>CC</sub>, SUPPLY VOLTAGE (V)

5.5

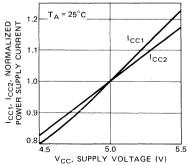

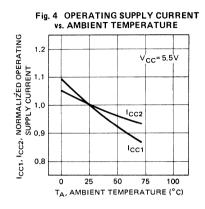

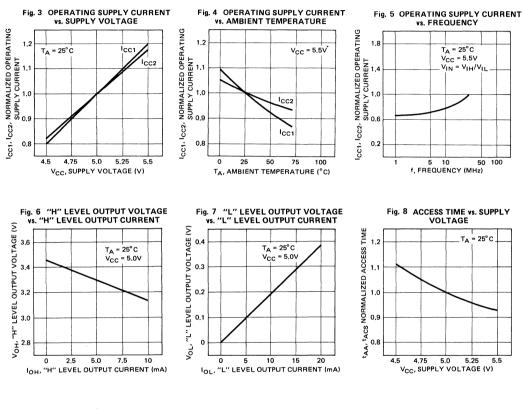

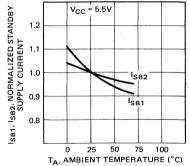

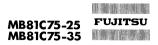

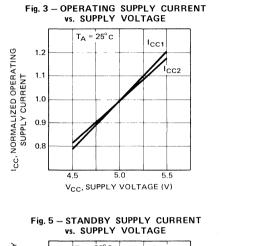

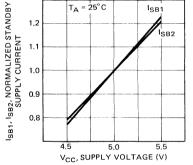

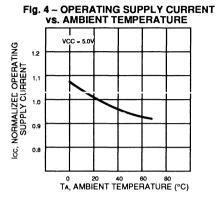

## Fig. 4 - OPERATING SUPPLY CURRENT vs. AMBIENT TEMPERATURE V<sub>CC</sub> = 5.5V Cycle min. 0 25 50 75 100 TA, AMBIENT TEMPERATURE (°C)

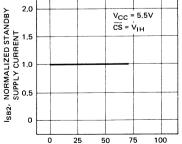

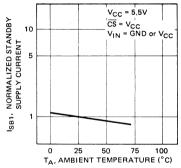

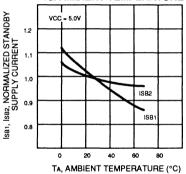

Fig. 6 – STANDBY SUPPLY CURRENT vs. AMBIENT TEMPERATURE

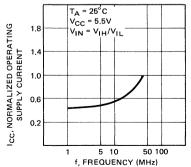

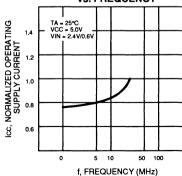

Fig. 7 - OPERATING SUPPLY CURRENT vs. FREQUENCY

| MB81C71A-25<br>MB81C71A-35 | FUJITSU |

|----------------------------|---------|

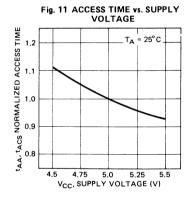

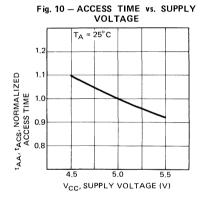

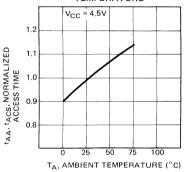

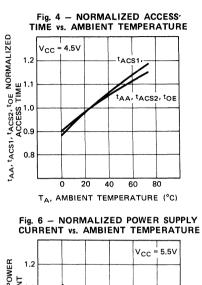

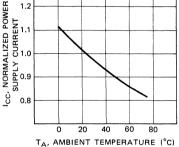

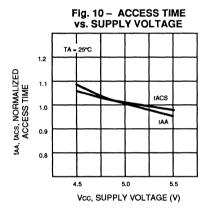

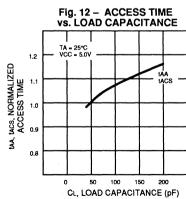

### TYPICAL CHARACTERISTICS CURVES (Cont'd)

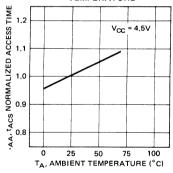

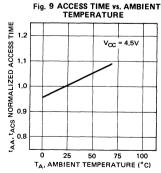

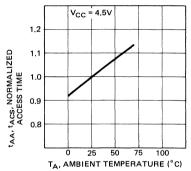

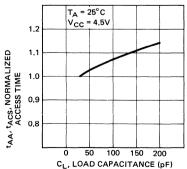

Fig. 11 – ACCESS TIME vs. AMBIENT TEMPERATURE

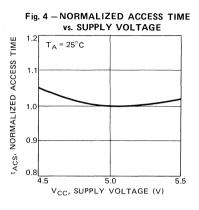

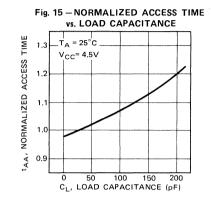

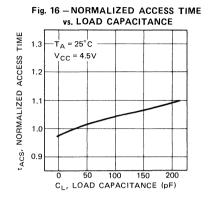

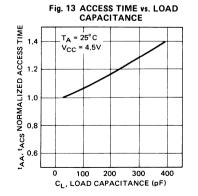

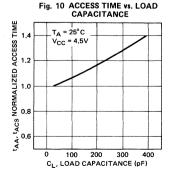

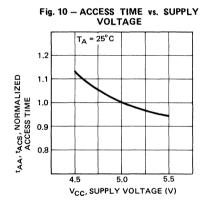

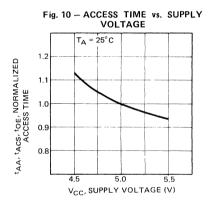

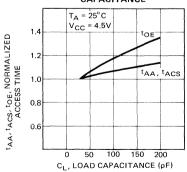

Fig. 12 – ACCESS TIME vs. LOAD CAPACITANCE  $T_A = 25^{\circ}C$   $V_{CC} = 4.5V$ 1.2 1.2 1.1 1.0 0.9 0.9 0.9 0.9 0.50 100 150 200 CL, LOAD CAPACITANCE (pF)

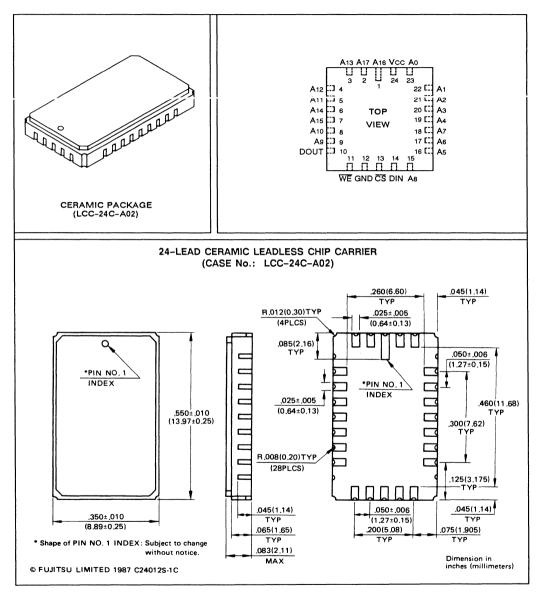

(Suffix: -P)

| MB81C71A-25<br>MB81C71A-35 | FUJITSU |

|----------------------------|---------|

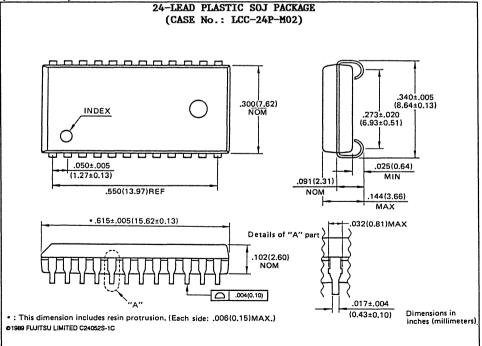

(Suffix: -PJ)

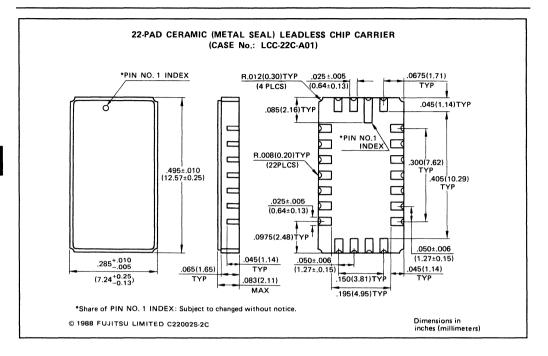

ſ

| FUJITSU | MB81C71A-25<br>MB81C71A-35 |

|---------|----------------------------|

.195(4.95)TYP

Dimensions in inches (millimeters)

.045(1.14) TYP .083(2.11) MAX .150(3.81)TYP .065(1.65) TYP 045(1.14) TYP (7.24+0.25)

\*Share of PIN NO. 1 INDEX: Subject to changed without notice.

© FUJITSU LIMITED 1987 C22002S-2C

# CMOS 65,536-BIT STATIC RANDOM ACCESS MEMORY

## MB81C74-25 MB81C74-35

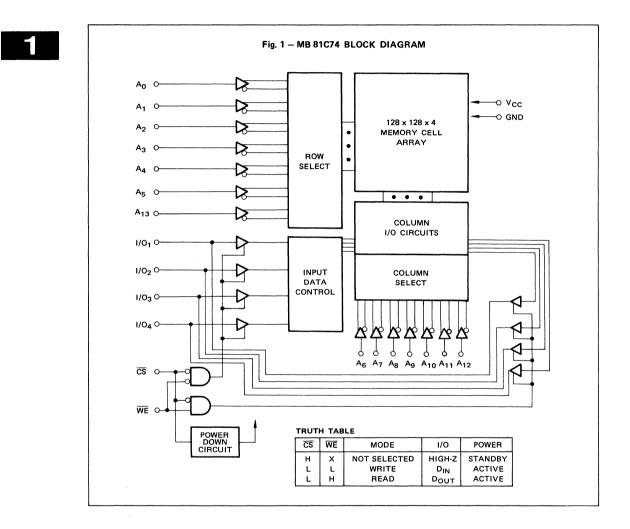

#### 16K x 4 BIT (65,536-BIT) HIGH SPEED STATIC RANDOM ACCESS MEMORY WITH AUTOMATIC POWER DOWN

The Fujitsu MB 81C74 is a 16,384-words by 4-bits static random access memory fabricated with a CMOS silicongate process. The memory utilizes asynchronous circuitry and may be maintained in any state for an indefinite period of time. All pins are TTL compatible, and a single 5 volts power supply is required.

The MB 81C74 is ideally suited for use in microprocessor systems and other applications where fast access time and ease of use are required. All devices offer the advantages of low power dissipation, low cost and high performance.

- Organization: 16,384 words x 4 bits

- Fast access time:  $t_{AA} = t_{ACS} = 25$  ns max. (MB 81C74-25)  $t_{AA} = t_{ACS} = 35$  ns max. (MB 81C74-35)

- Completely static operation: No clock required

- TTL compatible inputs/outputs

- Three-state output

- Common data input/output

- Single +5V power supply ±10% tolerance

- Low power standby: 440 mW max. (Active) 55 mW max. (Standby, CMOS level) 110 mW max. (Standby, TTL level)

- Standard 22-pin DIP (300 mil): Suffix: P

- Standard 22-pad LCC : Suffix: CV

#### ABSOLUTE MAXIMUM RATINGS (see NOTE)

| Rating              |                           | Symbol            | Value             | Unit |              |    |

|---------------------|---------------------------|-------------------|-------------------|------|--------------|----|

| Supply Voltage      |                           | V <sub>cc</sub>   | -0.5 to +7.0      | V    |              |    |

| Input Voltage       |                           | V <sub>IN</sub>   | -3.5 to +7.0      | v    |              |    |

| Output Voltage      | Output Voltage            |                   | Output Voltage    |      | -0.5 to +7.0 | v  |

| Output Current      | Output Current            |                   | Output Current    |      | ±20          | mA |

| Power Dissipation   | Power Dissipation         |                   | Power Dissipation |      | 1.0          | w  |

| Temperature Under B | ias                       | T <sub>BIAS</sub> | -10 to +85        | °C   |              |    |

| Storage             | Ceramic                   | Т <sub>stg</sub>  | 65 to +150        | °c   |              |    |

| Temperature Range   | Temperature Range Plastic |                   | -45 to +125       | U    |              |    |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

| FUJITSU | MB81C74-25<br>MB81C74-35 |

|---------|--------------------------|

### **CAPACITANCE** (T<sub>A</sub> = 25°C, f = 1 MHz)

| Parameter                                | Symbol           | Min | Тур | Max | Unit |

|------------------------------------------|------------------|-----|-----|-----|------|

| I/O Capacitance (V <sub>I/O</sub> = 0V)  | C <sub>I/O</sub> |     |     | 7   | pF   |

| Input Capacitance (V <sub>IN</sub> = 0V) | C <sub>IN</sub>  |     |     | 7   | pF   |

## **RECOMMENDED OPERATING CONDITIONS**

(Referenced to GND)

| Parameter           | Symbol          | Min                | Тур | Max | Unit |

|---------------------|-----------------|--------------------|-----|-----|------|

| Supply Voltage      | V <sub>cc</sub> | 4.5                | 5.0 | 5.5 | V    |

| Input Low Voltage   | VIL             | -2.0 <sup>*1</sup> |     | 0.8 | V    |

| Input High Voltage  | V <sub>IH</sub> | 2.2                |     | 6.0 | V    |

| Ambient Temperature | T <sub>A</sub>  | 0                  |     | 70  | °C   |

\*1 -2.0 V Min. for pulse width less than 20 ns. (V<sub>1L</sub> min. = -0.5 V at DC level)

### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                | Symbol            | Min | Max | Unit | Test Conditions                                                                                                                                                                          |

|--------------------------|-------------------|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standby Supply Current   | I <sub>SB1</sub>  |     | 10  | mA   | $ \begin{split} & \overline{CS} \geqq V_{CC}  0.2 \text{V}, \text{V}_{\text{IN}} \leqq 0.2 \text{V} \\ & \text{or } \text{V}_{\text{IN}} \geqq \text{V}_{CC}  0.2 \text{V} \end{split} $ |