# 8 / 16-Bit Microprocessors Microcomputers Peripherals

1987 Data Book

**Fujitsu Limited**

Fujitsu Microelectronics, Inc.

Fujitsu Mikroelektronik GmbH

Fujitsu Microelectronics Pacific Asia Ltd.

Worldwide Suppliers of Communications and Electronics Equipment

$\label{eq:copyright} \textbf{Copyright}^{\textcircled{0}} \textbf{1986 by Fujitsu Limited and Fujitsu Microelectronics, Inc.} \\ \textbf{All Rights Reserved.}$

Copyright<sup>®</sup> 1986 Fujitsu Limited, Tokyo, Japan, and Fujitsu Microelectronics, Inc.

All Rights Reserved.

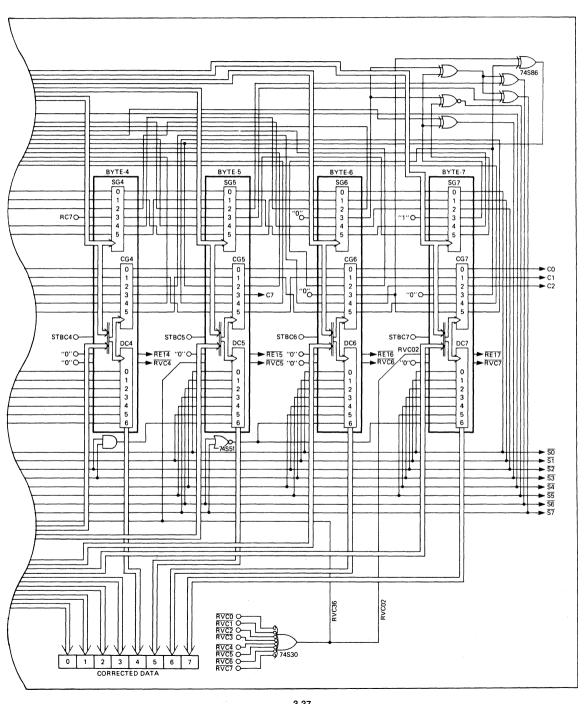

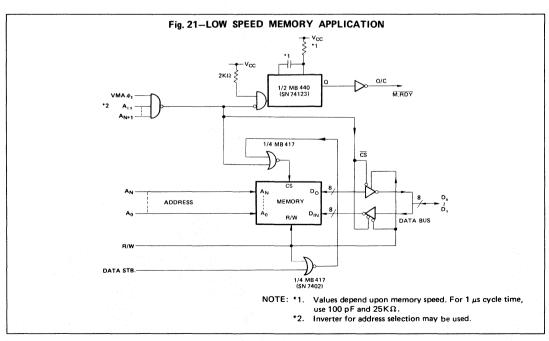

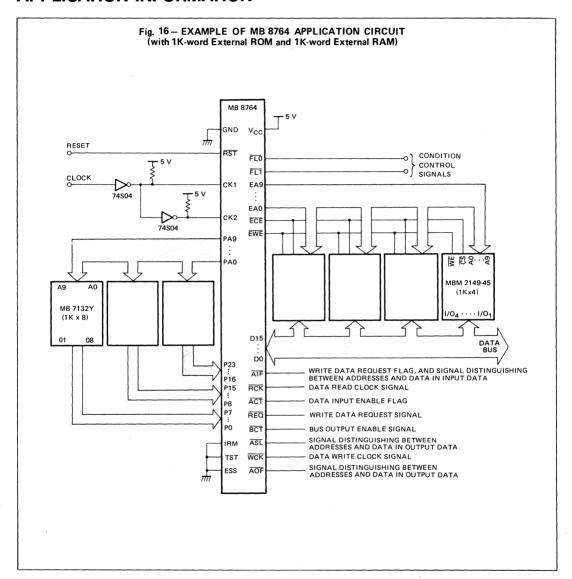

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Consequently, complete information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be entirely reliable. However, Fujitsu Limited and its subsidiaries assume no responsibility for inaccuracies.

The information conveyed in this document does not convey any license under the copyrights, patent rights or trade marks claimed and owned by Fujitsu Limited or its subsidiaries.

Fujitsu Limited and its subsidiaries reserve the right to change products or specifications without notice.

This document is published by the Technical Publications Department, Fujitsu Microelectronics, Inc., 3320 Scott Blvd., Santa Clara, California, U.S.A. 95054-3197.

Printed in the U.S.A.

Edition 1.0

#### **Fujitsu Limited**

Fujitsu Limited, headquartered near Tokyo, Japan, is Japan's largest supplier of computers and ranks in the top ten companies operating in Japan. Fujitsu is also one of the world's largest suppliers of telecommunications equipment and semiconductor devices.

Established in 1935 as the Communications Division spinoff of Fuji Electric Company Limited, Fujitsu Limited, in 1985, celebrated 50 years of service to the world through the development and manufacture of state-of-the-art products in data processing, telecommunications and semiconductors. Fujitsu operates subsidiaries worldwide in two dozen countries and employs over 80,000 people to generate annual sales in excess of nine billion US dollars. (Year ended March 31, 1986 consolidated base.)

Fujitsu has five plants in key industrial regions in Japan covering all steps of semiconductor production. Five wholly owned Japanese subsidiaries provide additional capacity for production of advanced semiconductor devices. Two additional facilities operate in the U.S. and Europe to help meet the growing worldwide demand for Fujitsu semiconductor products. In all, Fujitsu operations occupy over 1.6 million square meters of manufacturing space worldwide.

#### Semiconductor Products

In 1975, Fujitsu developed 8-bit microcomputers. In 1977, Fujitsu introduced proprietary 4-bit microcomputers. Today, their 4-bit microcomputer family is the largest 4-bit product line in the world. With the development of the high performance 16-bit micropcocessors, Fujitsu offers a full line of microprocessors, microcomputers, and peripherals to provide designers with a total of 150 products, including 90 products in CMOS families, 50 products in NMOS families and 10 products in bipolar peripherals.

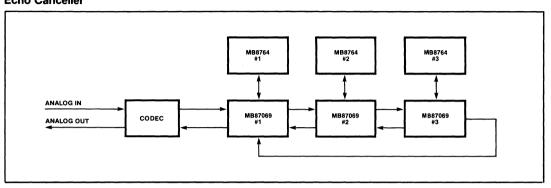

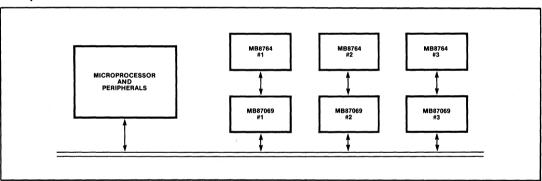

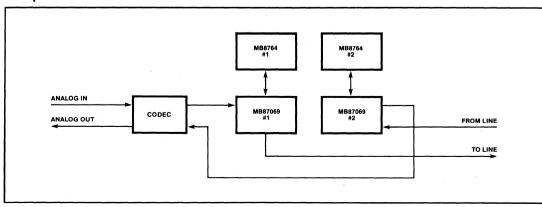

In 1983, Fujitsu introduced the world's first CMOS single-chip Digital Signal Processor, the MB8764. Fujitsu's DSP provides telecommunication designers with high-speed signal processing capabilities and at a cost-effective solution.

Other Fujitsu industry standard products include GaAs FETs, GaAs FET amplifiers, Si microwave transistors and light wave semiconductors. Discrete products include power-switching transistors and Darlington Array transistors.

Fujitsu's custom product lines include application-specific gate arrays and standard-cell arrays using high-speed Bipolar and ECL technologies and advanced CMOS technologies. Gate arrays ranging in size from 350 to 20,000 gates are available in up to 8,000 gate equivalents and include on-chip memory and program logic array.

Virtually every major type of electronics equipment on the globe utilizes Fujitsu technology in integrated circuits. Fujitsu's leadership position in worldwide integrated circuit development and manufacturing assures equipment manufacturers that they will always be able to design with the latest in technology utilizing the highest standards of quality and reliability.

#### Fujitsu Microelectronics, Inc.

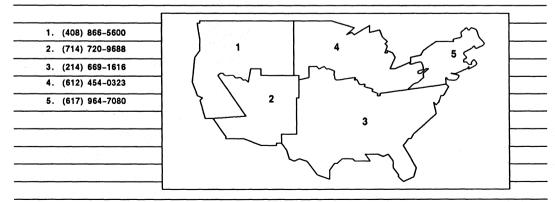

Established in 1979, Fujitsu Microelectronics, Inc., headquartered in Santa Clara, California, markets Fujitsu semiconductors through representatives located throughout the U.S. and North America.

The Component Division, Fujitsu Component of America, Inc., markets bubble memories, keyboards, plasma displays, relay switches and hybrid ICs.

FMI's San Diego manufacturing facility provides capacity for manufacturing of many high-technology devices for the U.S. and North American market.

Customer support for custom designs is available through Fujtsu's design centers in Santa Clara, Dallas and Boston. Technology Centers offering on-site customer training, CAE design facilities and design assistance are planned.

#### Fujitsu Mikroelektronik GmbH (European Sales Center)

Fujitsu Mikroelektronick GmbH (FMG) was established in June, 1980, in Frankfurt, West Germany, and is a totally owned subsidiary of Fujitsu Limited, Tokyo. FMG is the sole representative of the Fujitsu Electronic Device Group in Western Europe. The wide range of IC products, LSI memories and, in particular, gate arrays are noted throughout Western Europe for design excellence and unmatched reliability. Five branch offices to support Fujitsu's semiconductor operations are located in Munich, London, Paris, Stockholm, and Milan.

#### Fujitsu Microelectronics Ireland, Ltd (European Production Center)

Fujitsu Microelectronics Ireland, Ltd. (FME) was established in 1980 in the suburbs of Dublin as Fujitsu's European Production Center for integrated circuits. FME supplies 64K/256K DRAMS, 64K CMOS/NMOS EPROMs, 256K EPROMs, and other LSI memory products.

#### Fujitsu Microelectronics, Ltd (European Design Center)

Fujitsu Microelectronics, Ltd., Fujitsu's European VLSI Design Center, opened in October of 1983 in Manchester, England. The Design Center is equipped with a highly-sophisticated CAD system to ensure fast and reliable processing of input data. An experienced staff of engineers is available to assist in all phases of the design process.

#### Fujitsu Microelectronics Pacific Asia Ltd. (Asian/Oceanian Sales Centre)

Fujitsu Microelectronics Pacific Asia Ltd. (FMP) opened in August 1986 in Hong Kong as a wholly-owned Fujitsu subsidiary for sales of electronic devices to Asian and Southwest Pacific markets.

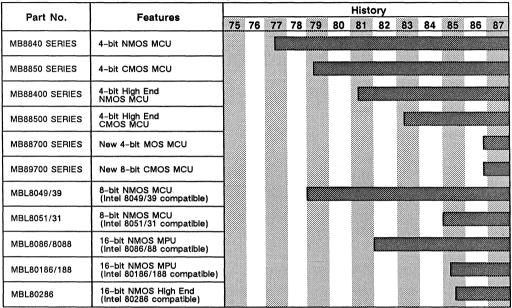

Fujitsu MCU/MPU Development History

August 1986

Production

# **Quick Reference**

| Microprocessors and Peripherals   |

|-----------------------------------|

| Microcomputers and Peripherals    |

| Memory Controllers                |

| Peripheral Support Devices        |

| Local Area Network (LAN) Products |

| Signal Processors and Peripherals |

| ROM Code Development Procedure    |

| Quality Assurance and Reliability |

| Ordering Information              |

## **Table of Contents**

## Section 1 Microprocessors and Peripherals

### MBL80286 Microprocessor Family

| 1-2  | MBL80286-8 | NMOS High-Performance 16-Bit Microprocessor with Memory Management and Protection |

|------|------------|-----------------------------------------------------------------------------------|

| 1-2  | MBL80286-6 | NMOS High-Performance 16-Bit Microprocessor with Memory Management and Protection |

| 1-59 | MBL82284-8 | Bipolar Block Generator and Ready Interface for MBL80286 Processors               |

| 1-59 | MBL82284-6 | Bipolar Block Generator and Ready Interface for<br>MBL80286 Processors            |

| 1-70 | MBL82288-8 | NMOS Bus Controller for MBL80286 Processors                                       |

| 1-70 | MBL82288-6 | NMOS Bus Controller for MBL80286 Processors                                       |

#### MBL8086/8088/80186/80188 Microprocessor Family and Peripherals

|       |            | •                                           |

|-------|------------|---------------------------------------------|

| 1-90  | MBL80186   | NMOS High-Integration 16-Bit Microprocessor |

| 1-90  | MBL80186-6 | NMOS High-Integration 16-Bit Microprocessor |

| 1-144 | MBL8086    | NMOS 16-bit Microprocessor                  |

| 1-144 | MBL8086-2  | NMOS 16-bit Microprocessor                  |

| 1-144 | MBL8086-1  | NMOS 16-bit Microprocessor                  |

| 1-172 | MBL80188   | NMOS High-Integration 8-Bit Microprocessor  |

| 1-172 | MBL80188-6 | NMOS High-Integration 8-Bit Microprocessor  |

| 1-226 | MBL8088    | NMOS 8-Bit Microprocessor                   |

| 1-226 | MBL8088-2  | NMOS 8-Bit Microprocessor                   |

| 1-226 | MBL8088-1  | NMOS 8-Bit Microprocessor                   |

| 1-256 | MBL8089    | NMOS 8 & 16-Bit I/O Processor               |

| 1-256 | MBL8089-2  | NMOS 8 & 16-Bit I/O Processor               |

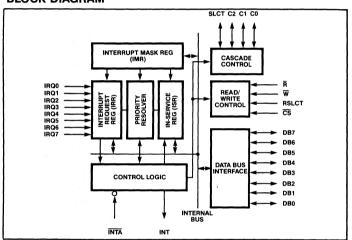

| 1-272 | MBL8259A   | NMOS Programmable Interrupt Controller      |

| 1-272 | MBL8259A-2 | NMOS Programmable Interrupt Controller      |

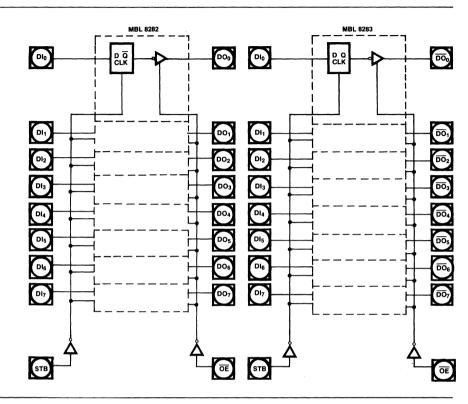

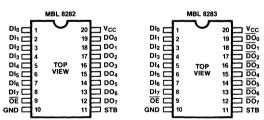

| 1-294 | MBL8282    | Bipolar Octal Latch                         |

| 1-294 | MBL8283    | Bipolar Octal Latch                         |

| 1-300 | MBL8284A   | Bipolar Clock Generator/Driver for MBL8086/ |

|       |            | MBL8088/MBL8089                             |

| 1-300 | MBL8284A-1 | Bipolar Clock Generator/Driver for MBL8086/ |

|       |            | MBL8088/MBL8089                             |

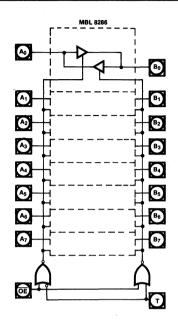

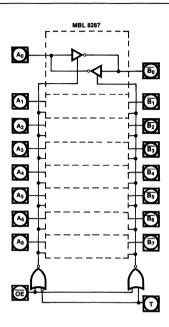

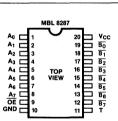

| 1-311 | MBL8286    | Bipolar Octal Bus Transceiver               |

| 1-311 | MBL8287    | Bipolar Octal Bus Transceiver               |

| 1-317 | MBL8288    | Bus Controller for MBL8086/MBL8088/MBL8089  |

|       |            | Processors                                  |

| 1-326 | MBL8289    | Bus Arbiter                                 |

## Section 2 Microcomputers and Peripherals

#### 8-Bit Microcomputers and Peripherals

| 2-2   | MBL8048N/E/H | NMOS Single-Chip 8-Bit Microcomputer |

|-------|--------------|--------------------------------------|

| 2-2   | MBL8035N/E/H | NMOS Single-Chip 8-Bit Microcomputer |

| 2-22  | MBL8049N/E/H | NMOS Single-Chip 8-Bit Microcomputer |

| 2-22  | MBL8039N/E/H | NMOS Single-Chip 8-Bit Microcomputer |

| 2-42  | MBL8749H/N   | NMOS Single-Chip 8-Bit Microcomputer |

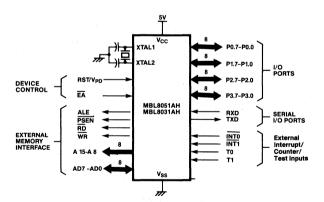

| 2-67  | MBL8051AH    | NMOS Single-Chip 8-Bit Microcomputer |

| 2-67  | MBL8031AH    | NMOS Single-Chip 8-Bit Microcomputer |

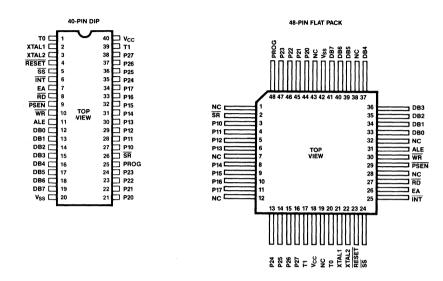

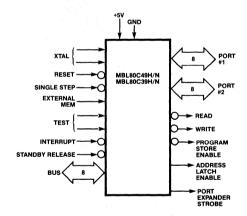

| 2-86  | MBL80C49H/N  | CMOS Single-Chip 8-Bit Microcomputer |

| 2-86  | MBL80C39H/N  | CMOS Single-Chip 8-Bit Microcomputer |

| 2-114 | MBL8243      | NMOS Input/Output Expander           |

| 2-124 | MBL82C43     | CMOS Input/Output Expander           |

#### Section 2 Microcomputers and Peripherals (Continued)

#### 4-Bit Microcomputers and Peripherals

| 2-136 | Selector Guide 1 | for 4-Bit Microcomputers   |

|-------|------------------|----------------------------|

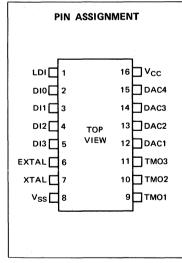

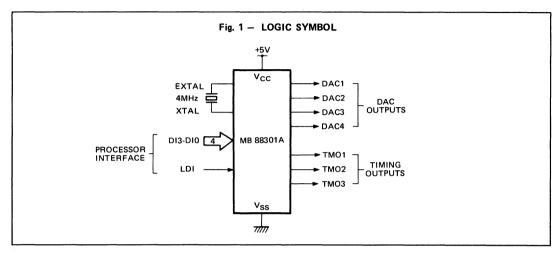

| 2-160 | MB88301A         | NMOS D/A Converter         |

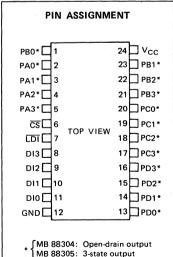

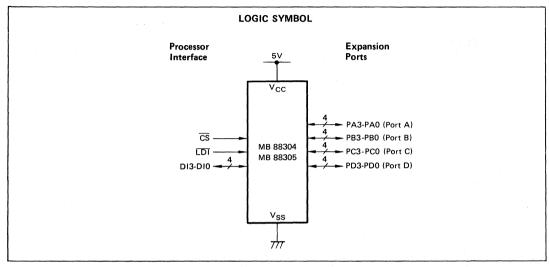

| 2-171 | MB88304          | NMOS Input/Outut Expander  |

| 2-171 | MB88305          | NMOS Input/Outut Expander  |

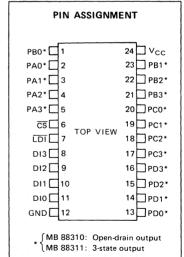

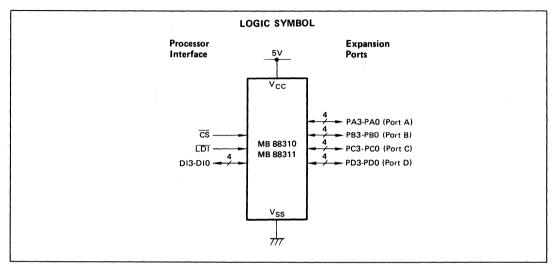

| 2-181 | MB88310          | CMOS Input/Output Expander |

| 2-181 | MB88311          | CMOS Input/Output Expander |

| 2-192 | MB88306          | CMOS Output Expander       |

| 2-192 | MB88307          | CMOS Output Expander       |

| 2-192 | MB88308          | CMOS Output Expander       |

| 2-192 | MB88309          | CMOS Output Expander       |

#### Section 3 **Memory Controllers**

| 3-2  | MB1422A | Dynamic RAM Controller LSI                   |

|------|---------|----------------------------------------------|

| 3-22 | MB1430  | 1M Dynamic RAM Controller                    |

| 3-23 | MB1412A | LS-TTL Error Checking and Correction Circuit |

| 3-39 | MB1426  | 16-Bit Error Checking and Correction         |

#### Section 4 **Peripheral Support Devices**

#### **CRT Controllers**

| 4-2  | MB89321A | CMOS Programmable CRT Controller |

|------|----------|----------------------------------|

| 4-2  | MB89322A | CMOS Programmable CRT Controller |

| 4-25 | MB89321B | CMOS Programmable CRT Controller |

| 4-25 | MB89322B | CMOS Programmable CRT Controller |

4-26

| 4-25   | MB89321B       | CMOS Programmable CRT Controller |

|--------|----------------|----------------------------------|

| 4-25   | MB89322B       | CMOS Programmable CRT Controller |

| Hard D | isk Controller |                                  |

Hard Disk Controller

#### Floppy Disk Controllers

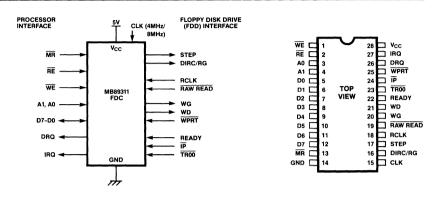

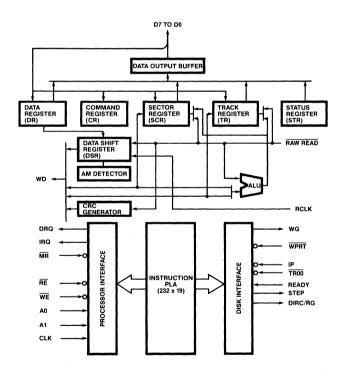

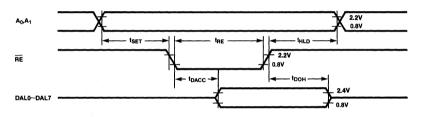

MB89341

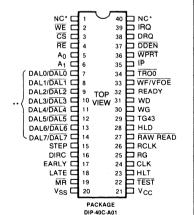

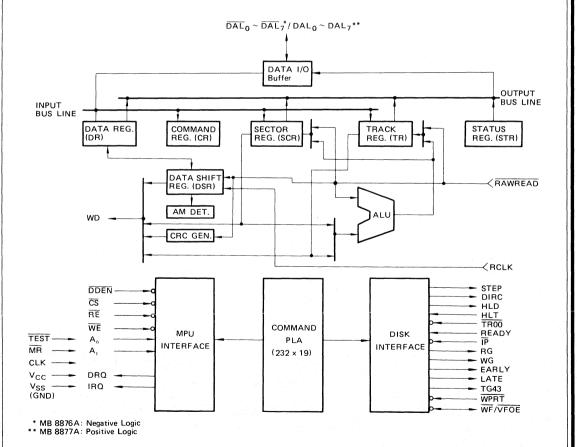

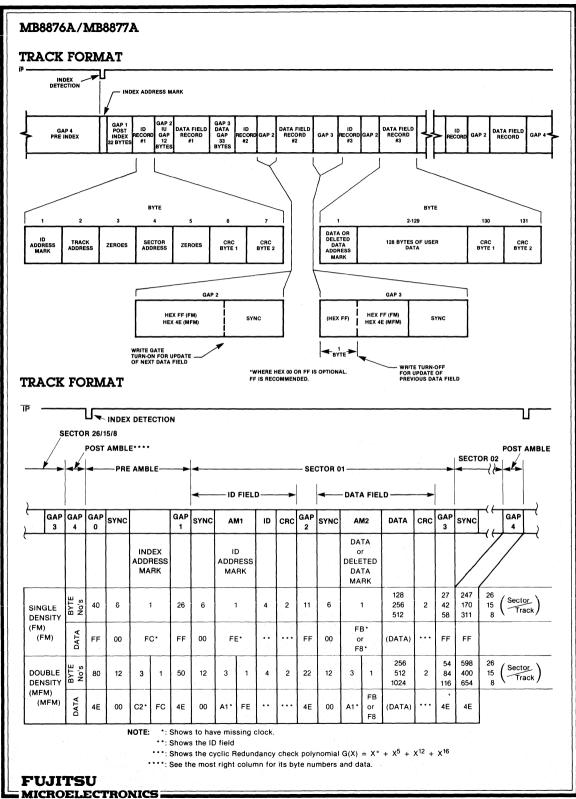

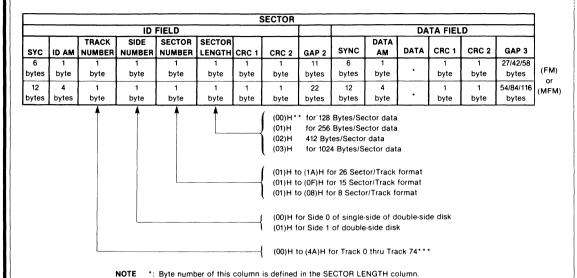

| 4-27 | MB8876A | Floppy Disk Formatter/Controller        |

|------|---------|-----------------------------------------|

| 4-27 | MB8877A | Floppy Disk Formatter/Controller        |

| 4-44 | MB89311 | CMOS Floppy Disk Controller/Formatter   |

| 4-57 | MB4107  | Floppy Disk VFO                         |

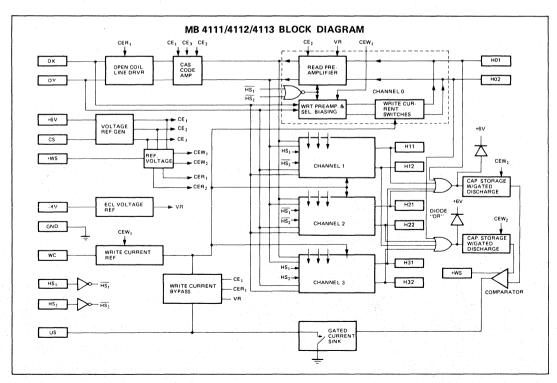

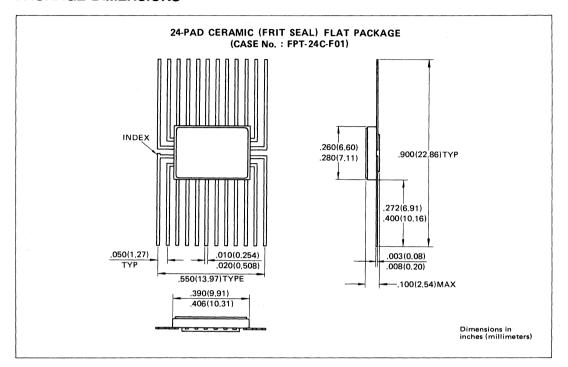

| 4-65 | MB4111  | Magnetic Disk Head Amplifier            |

| 4-65 | MB4112  | Magnetic Disk Head Amplifier            |

| 4-65 | MB4113  | Magnetic Disk Head Amplifier            |

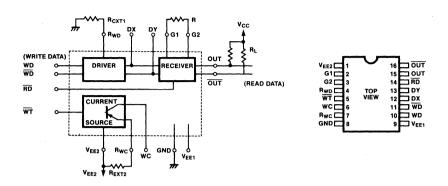

| 4-76 | MB4316  | Driver/Receiver for Disk Head Amplifier |

#### **Television Display Controllers**

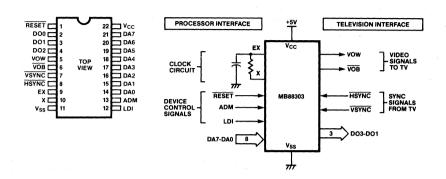

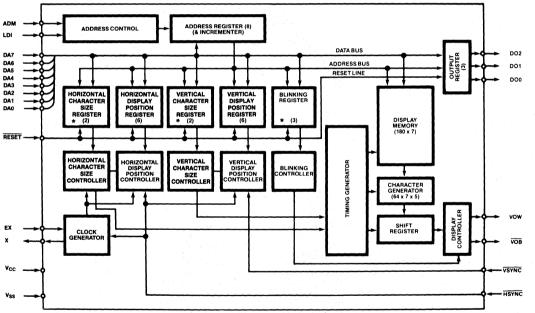

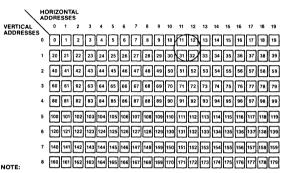

| 4-81 | MB88303 | NMOS Television Display Controller (TVDC) |

|------|---------|-------------------------------------------|

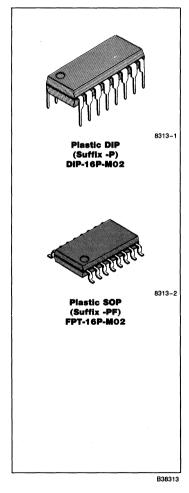

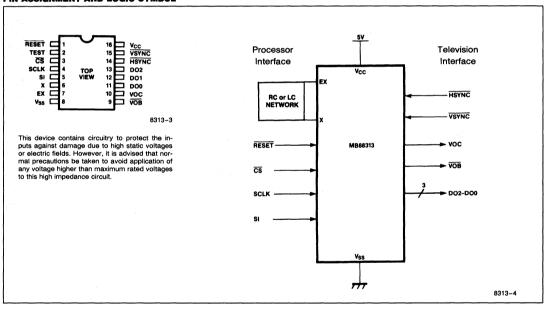

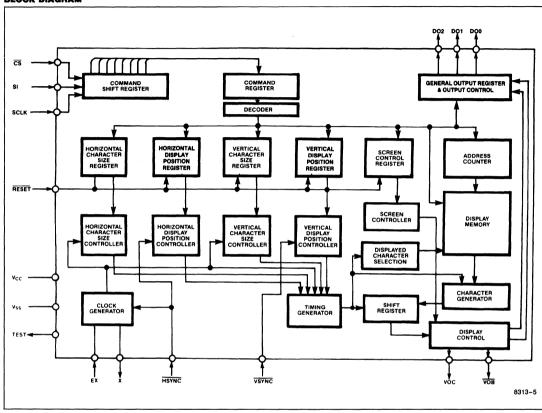

| 4-98 | MB88313 | CMOS Television Display Controller (TVDC) |

#### **Protocol Controller**

4-122 MB87030 **SCSI Protocol Controller**

#### Universal Peripheral Interface Peripherals

| 4-130 | MBL8041AH/E/N | NMOS Universal Peripheral Interface 8-Bit                             |

|-------|---------------|-----------------------------------------------------------------------|

| 4-147 | MBL8042H/N    | Microcomputer NMOS Universal Peripheral Interface 8-Bit Microcomputer |

| Section 4           | Peripho                                                              | eral Support D                                                                                       | evices (Continued)                                                                                                                                                                                |

|---------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -,                  | 4-164                                                                | MBL8742H/N                                                                                           | NMOS Universal Peripheral Interface 8-Bit                                                                                                                                                         |

|                     | 4-183                                                                | MB8868A                                                                                              | Microcomputer MOS Universal Asynchronous Receiver Transmitter (UART)                                                                                                                              |

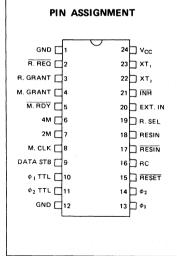

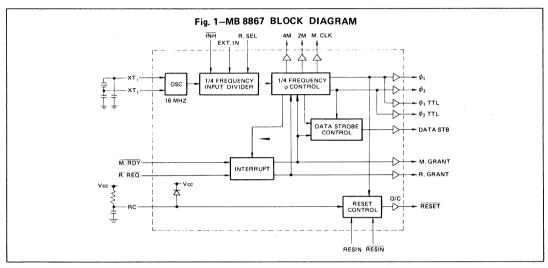

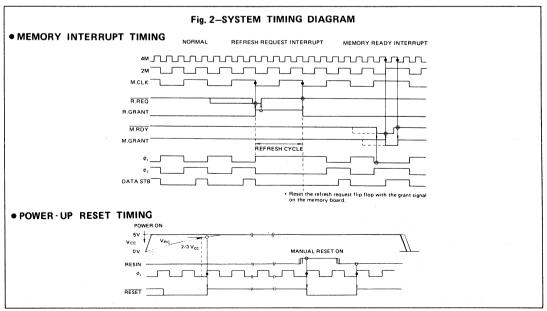

|                     | 4-194                                                                | MB8867                                                                                               | TTL Two-Phase Clock Generator and Driver                                                                                                                                                          |

|                     | 4-194                                                                | MB8867E                                                                                              | TTL Two-Phase Clock Generator and Driver                                                                                                                                                          |

|                     | Selecto                                                              | r Guide for A-to-                                                                                    | -D/D-to-A Interface Peripherals                                                                                                                                                                   |

|                     | 4-205                                                                | A-to-D Converte                                                                                      | • =                                                                                                                                                                                               |

|                     | 4-205                                                                | D-to-A Converte                                                                                      | rs                                                                                                                                                                                                |

|                     | CMOS F                                                               | Peripherals                                                                                          |                                                                                                                                                                                                   |

|                     | 4-207                                                                | MB89237A                                                                                             | DMA Controller                                                                                                                                                                                    |

|                     | 4-208                                                                | MB89251A                                                                                             | Serial Data Transmitter/Receiver                                                                                                                                                                  |

|                     | 4-209<br>4-210                                                       | MB89254<br>MB89255A                                                                                  | Programmable Timer Parallel Data I/O Interface                                                                                                                                                    |

|                     | 4-210                                                                | MB89259A                                                                                             | Programmable Interrupt Controller                                                                                                                                                                 |

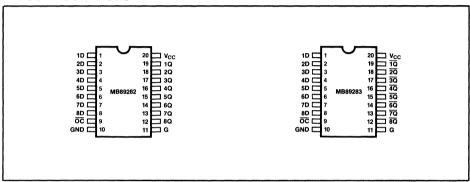

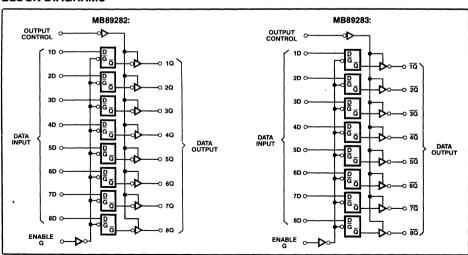

|                     | 4-212                                                                | MB89282                                                                                              | Address Latch                                                                                                                                                                                     |

|                     | 4-212                                                                | MB89283                                                                                              | Address Latch                                                                                                                                                                                     |

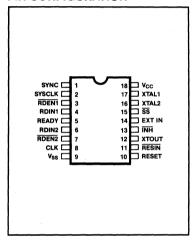

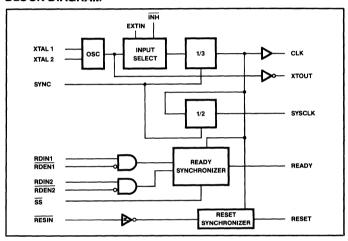

|                     | 4-213                                                                | MB89284A                                                                                             | Clock Generator                                                                                                                                                                                   |

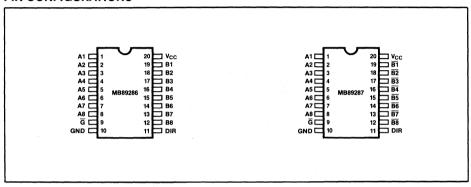

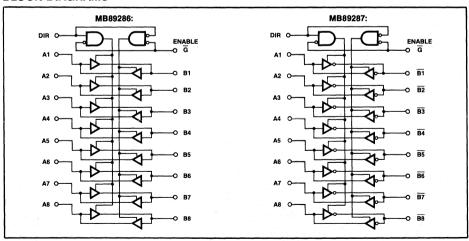

|                     | 4-214                                                                | MB89286                                                                                              | Data Bus Transceiver                                                                                                                                                                              |

|                     | 4-214                                                                | MB89287                                                                                              | Data Bus Transcelver                                                                                                                                                                              |

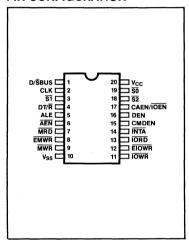

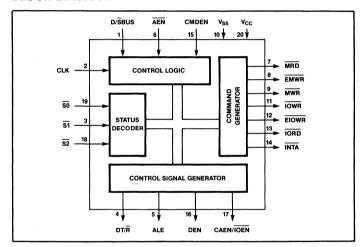

|                     | 4-215<br>4-216                                                       | MB89288<br>MB89289                                                                                   | Bus Controller Bus Arbiter                                                                                                                                                                        |

|                     |                                                                      | ,                                                                                                    |                                                                                                                                                                                                   |

| Section 5           | Local                                                                | Aroa Notwork                                                                                         | (LAN) Products                                                                                                                                                                                    |

| Section 5           |                                                                      |                                                                                                      | · ·                                                                                                                                                                                               |

|                     | 5-2<br>5-22                                                          | MB502A<br>MB8795B                                                                                    | Ethernet Encoder/Decoder Ethernet Data Link Controller                                                                                                                                            |

|                     |                                                                      | MOOFFE                                                                                               | Ethernet Data Link Controller                                                                                                                                                                     |

|                     | J-22                                                                 |                                                                                                      |                                                                                                                                                                                                   |

| Section 6           |                                                                      | Procesors as                                                                                         | ad Parinharals                                                                                                                                                                                    |

| Section 6           | Signal                                                               | Processors an                                                                                        | •                                                                                                                                                                                                 |

| Section 6           | Signal                                                               | MB8764                                                                                               | General Purpose Digital Signal Processor                                                                                                                                                          |

| Section 6           | <b>Signal</b><br>6-2<br>6-21                                         | MB8764<br>MB87064                                                                                    | General Purpose Digital Signal Processor<br>Low Cost General Purpose Digital Signal Processor                                                                                                     |

| Section 6           | Signal                                                               | MB8764                                                                                               | General Purpose Digital Signal Processor                                                                                                                                                          |

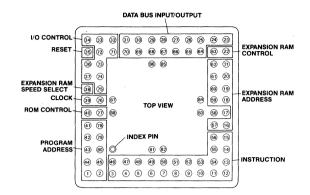

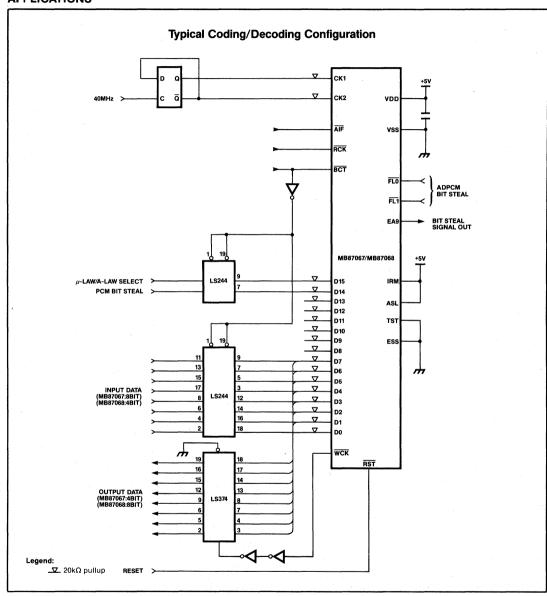

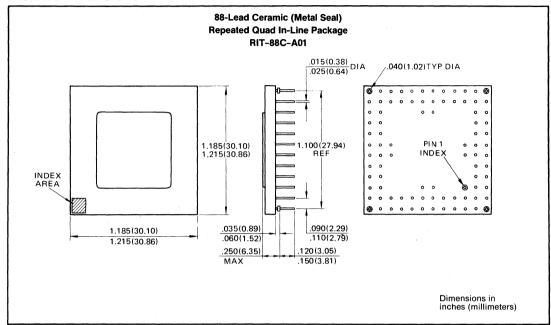

| Section 6           | Signal<br>6-2<br>6-21<br>6-33                                        | MB8764<br>MB87064<br>MB87067                                                                         | General Purpose Digital Signal Processor<br>Low Cost General Purpose Digital Signal Processor<br>ADPCM Digital Signal Processor                                                                   |

|                     | Signal<br>6-2<br>6-21<br>6-33<br>6-33<br>6-38                        | MB8764<br>MB87064<br>MB87067<br>MB87068<br>MB87069                                                   | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter                 |

|                     | Signal<br>6-2<br>6-21<br>6-33<br>6-33<br>6-38                        | MB8764<br>MB87064<br>MB87067<br>MB87068<br>MB87069                                                   | General Purpose Digital Signal Processor<br>Low Cost General Purpose Digital Signal Processor<br>ADPCM Digital Signal Processor<br>ADPCM Digital Signal Processor                                 |

|                     | Signal<br>6-2<br>6-21<br>6-33<br>6-33<br>6-38                        | MB8764<br>MB87064<br>MB87067<br>MB87068<br>MB87069<br>Code Developm                                  | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter                 |

|                     | Signal<br>6-2<br>6-21<br>6-33<br>6-33<br>6-38                        | MB8764<br>MB87064<br>MB87067<br>MB87068<br>MB87069                                                   | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter                 |

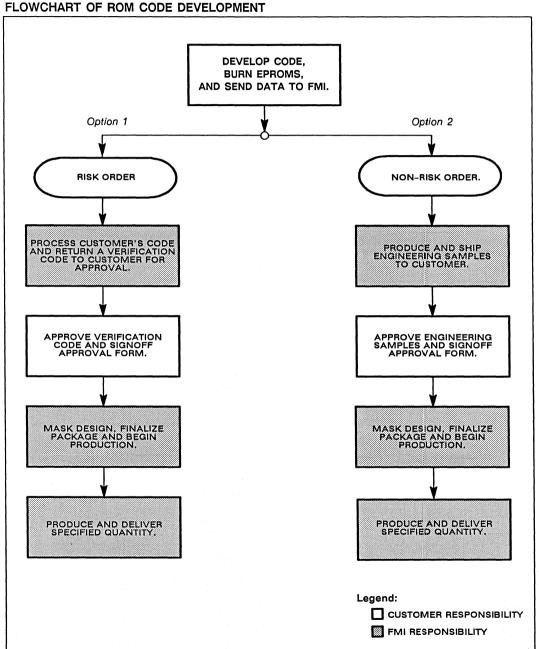

| Section 7           | Signal<br>6-2<br>6-21<br>6-33<br>6-33<br>6-38<br>ROM C<br>7-2<br>7-3 | MB8764 MB87064 MB87067 MB87068 MB87069  Code Developm Procedure Flowchart                            | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter                 |

|                     | Signal<br>6-2<br>6-21<br>6-33<br>6-33<br>6-38<br>ROM C<br>7-2<br>7-3 | MB8764<br>MB87064<br>MB87067<br>MB87068<br>MB87069<br>Code Developm                                  | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter                 |

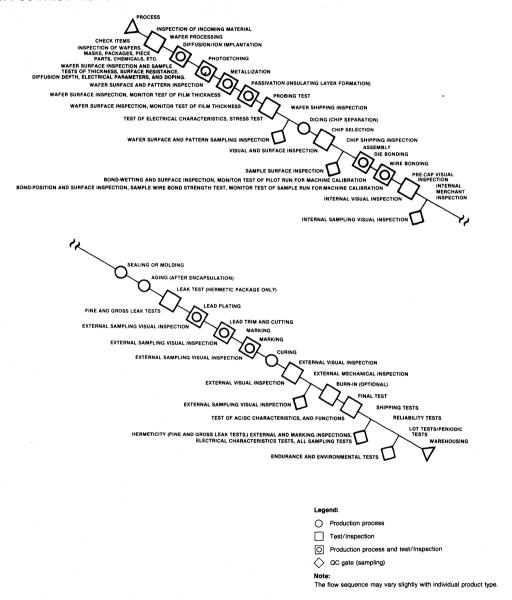

| Section 7 Section 8 | Signal<br>6-2<br>6-21<br>6-33<br>6-38<br>ROM C<br>7-2<br>7-3         | MB8764 MB87064 MB87067 MB87068 MB87069  Code Developm Procedure Flowchart  / Assurance all Flowchart | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter  nent Procedure |

| Section 7           | Signal 6-2 6-21 6-33 6-38 6-38  ROM C 7-2 7-3  Quality 8-2           | MB8764 MB87064 MB87067 MB87068 MB87069  Code Developm Procedure Flowchart  / Assurance all Flowchart | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter  nent Procedure |

| Section 7 Section 8 | Signal<br>6-2<br>6-21<br>6-33<br>6-38<br>ROM C<br>7-2<br>7-3         | MB8764 MB87064 MB87067 MB87068 MB87069  Code Developm Procedure Flowchart  / Assurance all Flowchart | General Purpose Digital Signal Processor Low Cost General Purpose Digital Signal Processor ADPCM Digital Signal Processor ADPCM Digital Signal Processor Serial Interface Adapter  nent Procedure |

# Alphanumeric Index

|             | <b>D</b> | Book Newsbar  | Dono  | Part Number | Page  |

|-------------|----------|---------------|-------|-------------|-------|

| Part Number | Page     | Part Number   | Page  | Part Number | rage  |

| MB Prefix   |          | MB88313       | 4-98  | MBL8086-1   | 1-144 |

|             |          | MB89237A      | 4-207 | MBL8086-2   | 1-144 |

| MB502A      | 5-2      | MB89251A      | 4-208 | MBL8088     | 1-226 |

|             |          | MB89254       | 4-209 | MBL8088-1   | 1-226 |

| MB1412A     | 3-23     |               |       | MBL8088-2   | 1-226 |

| MB1422A     | 3-2      | MB89255A      | 4-210 |             |       |

| MB1426      | 3-39     | MB89259A      | 4-211 | MBL8089     | 1-256 |

| MB1430      | 3-22     |               |       | MBL8089-2   | 1-256 |

|             |          | MB89282       | 4-212 |             |       |

| MB4107      | 4-57     | MB89283       | 4-212 | MBL8243     | 2-114 |

| MB4111      | 4-65     | MB89284A      | 4-213 | MBL82C43    | 2-124 |

| MB4112      | 4-65     | MB89286       | 4-214 |             |       |

| MB4113      | 4-65     | MB89287       | 4-214 | MBL8259A    | 1-272 |

| MB4316      | 4-76     | MB89288       | 4-215 | MBL8259A-2  | 1-272 |

|             |          | MB89289       | 4-216 |             |       |

| MB8764      | 6-2      |               |       | MBL8282     | 1-294 |

| MB8795B     | 5-22     | MB89311       | 4-44  | MBL8283     | 1-294 |

|             |          | MB89321A      | 4-2   |             |       |

| MB8867      | 4-194    | MB89321B      | 4-25  | MBL8284A    | 1-300 |

| MB8867E     | 4-194    | MB89322A      | 4-2   | MBL8284A-1  | 1-300 |

| MB8868A     | 4-183    | MB89322B      | 4-25  | MBL8286     | 1-311 |

| MB8876A     | 4-27     | MB89341       | 4-26  | MBL8287     | 1-311 |

| MB8877A     | 4-27     |               |       | MBL8288     | 1-317 |

|             |          | MBL Prefix    |       | MBL8289     | 1-326 |

| MB87030     | 4-122    |               |       |             |       |

| MB87064     | 6-21     | MBL8031AH     | 2-67  | MBL8742H/N  | 4-164 |

| MB87067     | 6-33     | MBL8035N/E/H  | 2-2   | MBL8749H/N  | 2-42  |

| MB87068     | 6-33     | MBL8039N/E/H  | 2-22  |             |       |

| MB87069     | 6-38     | MBL80C39H/N   | 2-86  | MBL80186    | 1-90  |

|             |          |               |       | MBL80186-6  | 1-90  |

| MB88301A    | 2-160    | MBL8041AH/E/N | 4-130 | MBL80188    | 1-172 |

| MB88303     | 4-81     | MBL8042H/N    | 4-147 | MBL80188-6  | 1-172 |

| MB88304     | 2-171    | MBL8048N/E/H  | 2-2   |             |       |

| MB88305     | 2-171    | MBL8049N/E/H  | 2-22  | MBL80286-6  | 1-2   |

| MB88306     | 2-192    |               |       | MBL80286-8x | 1-2   |

| MB88307     | 2-192    | MBL80C49H/N   | 2-86  |             |       |

| MB88308     | 2-192    |               |       | MBL82284-6  | 1-59  |

| MB88309     | 2-192    | MBL8051AH     | 2-67  | MBL82284-8  | 1-59  |

| MB88310     | 2-181    |               |       | MBL82288-6  | 1-70  |

| MB88311     | 2-181    | MBL8086       | 1-144 | MBL82288-8  | 1-70  |

|             |          |               |       |             |       |

# Section 1

# Microprocessors and Peripherals

| MB L8028 | 36 Microprocessor  | Family                                                                            |

|----------|--------------------|-----------------------------------------------------------------------------------|

| 1-2      | MBL80286-8         | NMOS High-Performance 16-Bit Microprocessor with Memory Management and Protection |

| 1-2      | MBL80286-6         | NMOS High-Performance 16-Bit Microprocessor                                       |

|          |                    | with Memory Management and Protection                                             |

| 1-59     | MBL82284-8         | Bipolar Block Generator and Ready Interface for<br>MBL80286 Processors            |

| 1-59     | MBL82284-6         | Bipolar Block Generator and Ready Interface for MBL80286 Processors               |

| 1-70     | MBL82288-8         | NMOS Bus Controller for MBL80286 Processors                                       |

| 1-70     | MBL82288-6         | NMOS Bus Controller for MBL80286 Processors                                       |

| MBL808   | 5/8088/80186/80188 | Microprocessor Family and Peripherals                                             |

| 1-90     | MBL80186           | NMOS High-Integration 16-Bit Microprocessor                                       |

| 1-90     | MBL80186-6         | NMOS High-Integration 16-Bit Microprocessor                                       |

| 1-144    | MBL8086            | NMOS 16-bit Microprocessor                                                        |

| 1-144    | MBL8086-2          | NMOS 16-bit Microprocessor                                                        |

| 1-144    | MBL8086-1          | NMOS 16-bit Microprocessor                                                        |

| 1-172    | MBL80188           | NMOS High-Integration 8-Bit Microprocessor                                        |

| 1-172    | MBL80188-6         | NMOS High-Integration 8-Bit Microprocessor                                        |

| 1-226    | MBL8088            | NMOS 8-Bit Microprocessor                                                         |

| 1-226    | MBL8088-2          | NMOS 8-Bit Microprocessor                                                         |

| 1-226    | MBL8088-1          | NMOS 8-Bit Microprocessor                                                         |

| 1-256    | MBL8089            | NMOS 8 & 16-Bit I/O Processor                                                     |

| 1-256    | MBL8089-2          | NMOS 8 & 16-Bit I/O Processor                                                     |

| 1-272    | MBL8259A           | NMOS Programmable Interrupt Controller                                            |

| 1-272    | MBL8259A-2         | NMOS Programmable Interrupt Controller                                            |

| 1-294    | MBL8282            | Bipolar Octal Latch                                                               |

| 1-294    | MBL8283            | Bipolar Octal Latch                                                               |

| 1-300    | MBL8284A           | Bipolar Clock Generator/Driver for MBL8086/<br>MBL8088/MBL8089                    |

| 1-300    | MBL8284A-1         | Bipolar Clock Generator/Driver for MBL8086/<br>MBL8088/MBL8089                    |

| 1-311    | MBL8286            | Bipolar Octal Bus Transceiver                                                     |

| 1-311    | MBL8287            | Bipolar Octal Bus Transceiver                                                     |

| 1-317    | MBL8288            | Bus Controller for MBL8086/MBL8088/MBL8089 Processors                             |

| 1-326    | MBL8289            | Bus Arbiter                                                                       |

## NMOS HIGH-PERFORMANCE 16-BIT MICROPROCESSOR WITH MEMORY MANAGEMENT AND PROTECTION

MBL 80286-8 MBL 80286-6

> January 1986 Edition 1.0

# NMOS HIGH PERFORMANCE 16-BIT MICROPROCESSOR WITH MEMORY MANAGEMENT AND PROTECTION

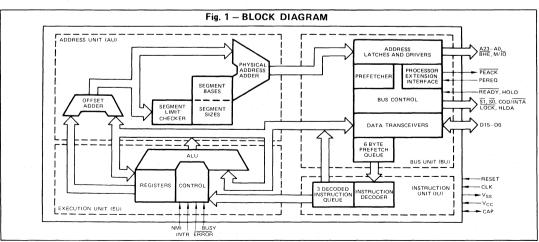

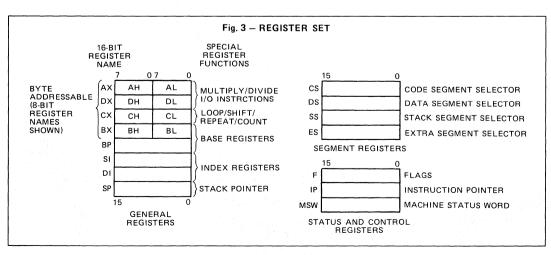

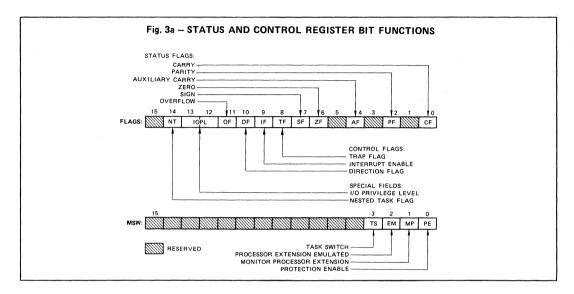

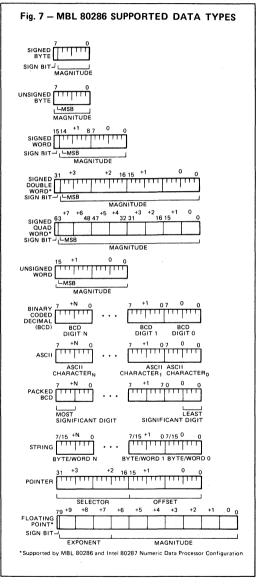

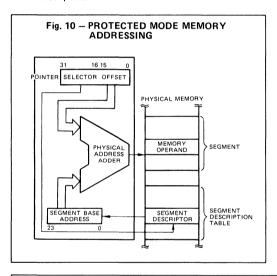

The Fujitsu MBL 80286 is an advanced, high-performance 16-bit microprocessor with specially optimized capabilities for multiple user and multi-tasking systems. The MBL 80286 has built-in memory protection that supports operating system and task isolation as well as program and data privacy within tasks. An 8 MHz MBL 80286 provides up to six times greater throughout than the standard 5 MHz MBL 8086. The MBL 80286 includes memory management capabilities that map up to 2<sup>30</sup> (one gigabyte) of virtual address space per task into 2<sup>24</sup> bytes (16 megabytes) of physical memory.

The MBL 80286 is upward compatible with MBL 8086 and 88 software. Using MBL 8086 real address mode, the MBL 80286 is object code compatible with existing MBL 8086, 88 software. In protected virtual address mode, the MBL 80286 is source code compatible with MBL 8086, 88 software and may require upgrading to use virtual addresses supported by the MBL 80286's integrated memory management and protection mechanism. Both modes operate at full MBL 80286 performance and execute a superset of the MBL 8086 and 88's instructions.

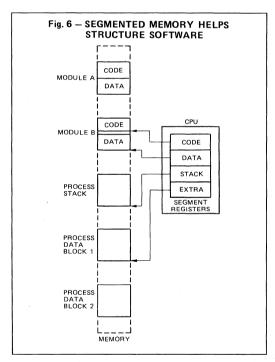

The MBL 80286 provides special operations to support the efficient implementation and execution of operating systems. For example, one instruction can end execution of one task, save its state, switch to a new task, load its state, and start execution of the new task. The MBL 80286 also supports virtual memory systems by providing a segment-not-present exception and restartable instructions.

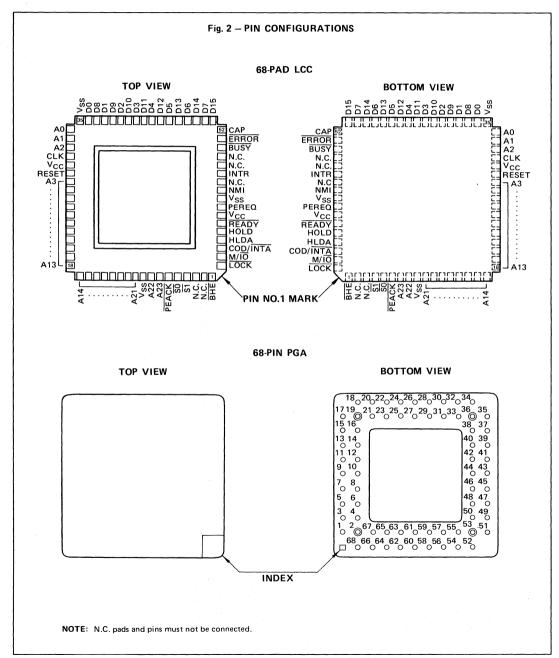

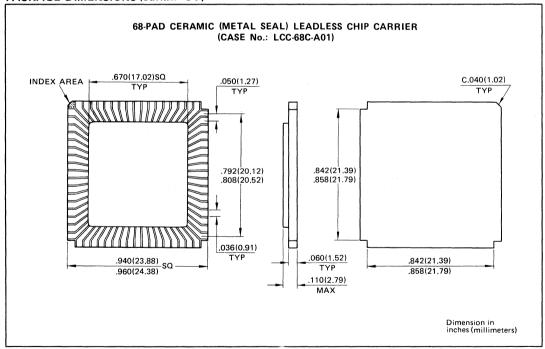

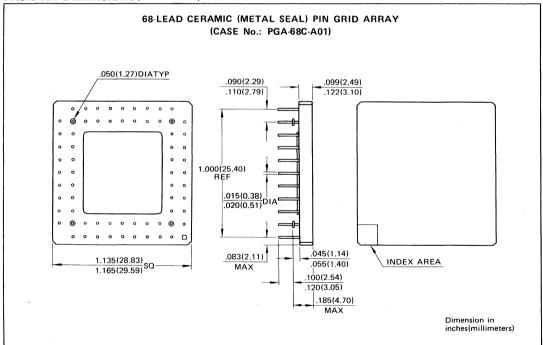

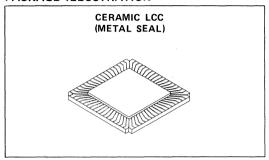

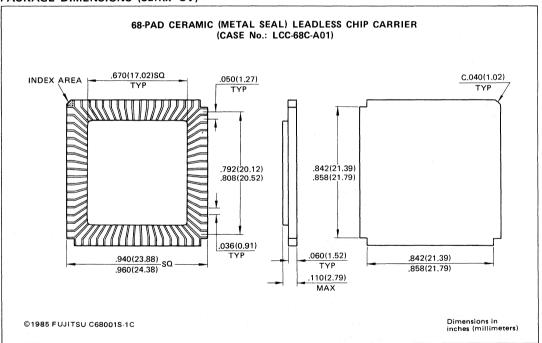

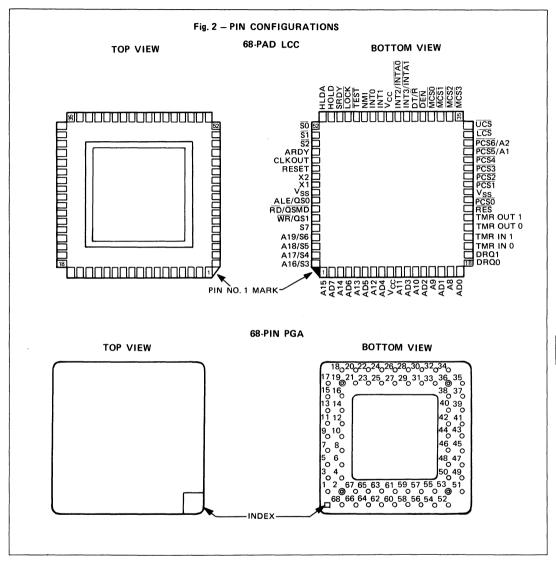

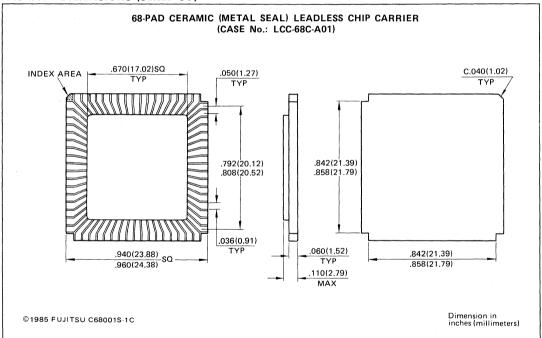

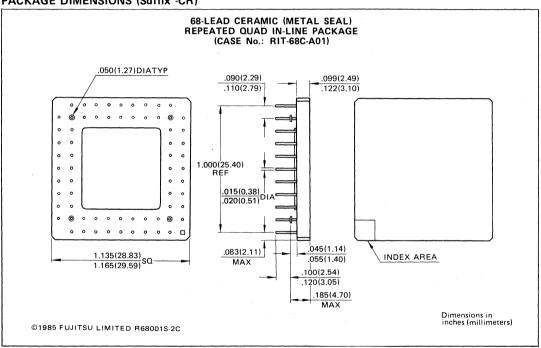

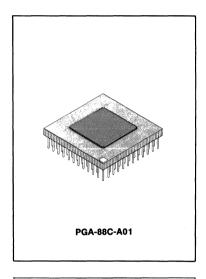

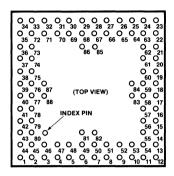

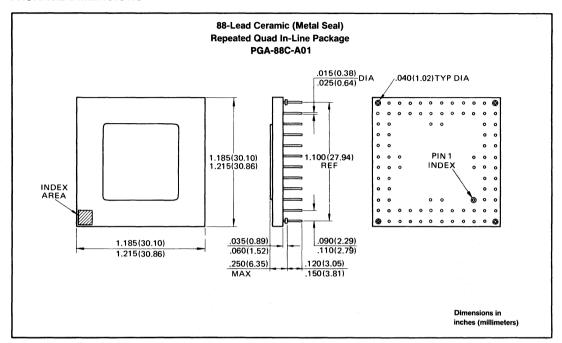

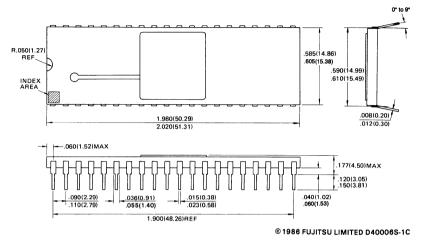

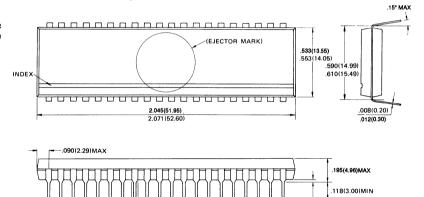

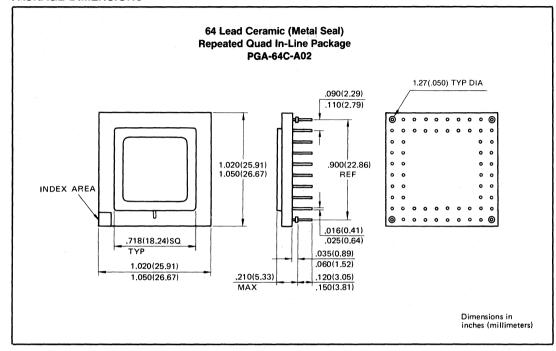

The MBL 80286 is housed in a 68-pad ceramic LCC (Leadless Chip Carrier: JEDEC Type A) or a 68-pin ceramic PGA (Pin Grid Array) package.

- High Performance Processor (Up to six times MBL 8086)

- Large Address Space:

- 16 Megabytes Physical

- 1 Gigabyte Virtual per Task

- Integrated Memory Management, Four-Level Memory Protection and Support for Virtual Memory and Operating Systems

- Two MBL 8086 Upward Compatible Operating Modes:

- MBL 8086 Real Address Mode

- Protected Virtual Address Mode

- Two Ranges of Clock Rates:

- 8 MHz for MBL 80286-8

- 6 MHz for MBL 80286-6

Optional Processor Extension:

- MBL 80286 and Intel 80287 High Performance 80-bit Numeric Data Processor

- High Bandwidth Bus Interface (8 Megabyte/Sec)

- Two Package Options:

- 68-Pad Ceramic LCC (Suffix CV)

- (JEDEC Type A)

- 68-Pin Ceramic PGA (Suffix CR)

Portions Reprinted by Permission of Intel Corporation

© Intel Corporation, 1985

#### PIN DESCRIPTION

The following pin function descriptions are for the MBL 80286 microprocessor:

Table 1 - PIN DESCRIPTION

| Symbol         | Type | Name and Function                                                                                                                                                                                                                                                                      |                                                                                      |                                                                                         |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                           |        |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

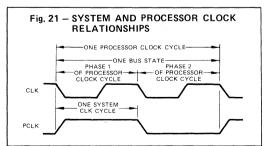

| CLK            | -    | System Clock provides the fundamental timing for MBL 80286 systems. It is divided by two inside the MBL 80286 to generate the processor clock. The internal divide-by-two circuitry can be synchronized to an external clock generator by a LOW to HIGH transition on the RESET input. |                                                                                      |                                                                                         |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                           |        |

| D15-D0         | I/O  | Data Bus inputs data during memory, I/O, and interrupt acknowledge read cycles; outputs data during memory and I/O write cycles. The data bus is active HIGH and floats to 3-state OFF during bus hold acknowledge.                                                                    |                                                                                      |                                                                                         |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                           |        |

| A23-A0         | 0    | Address Bus outputs physical memory and I/O port addresses. A0 is LOW when data is to be transferred on pins D7–D0. A23–A16 are LOW during I/O transfers. The address bus is active HIGH and floats to 3-state OFF during bus hold acknowledge.                                        |                                                                                      |                                                                                         |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                           |        |

| BHE            | 0    | bit o                                                                                                                                                                                                                                                                                  | oriented devic                                                                       | es assigne                                                                              | d to the                                                                                                                                                                    | upper byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e upper byte of the data bus, D15—D8<br>of the data bus would normally use Ē<br>DW and floats to 3-state OFF during b                                                                                                                                                                                                                                     | 3HE to |

|                |      |                                                                                                                                                                                                                                                                                        |                                                                                      | BHE an                                                                                  | d A0 Enco                                                                                                                                                                   | dings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                           |        |

|                |      |                                                                                                                                                                                                                                                                                        | BHE Value                                                                            | A0                                                                                      | Value                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                                                                                                                                  |        |

|                |      |                                                                                                                                                                                                                                                                                        |                                                                                      | sfer<br>fer on upper half of data bus (D15—D8)<br>fer on lower half of data bus (D7—D0) |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                           |        |

|                |      |                                                                                                                                                                                                                                                                                        | 1                                                                                    | -                                                                                       | 1                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · ·                                                                                                                                                                                                                                                                                                                                                       |        |

| \$1,\$0        | 0    | defii                                                                                                                                                                                                                                                                                  | Cycle Status<br>neds the type                                                        | of bus cy                                                                               | initiation                                                                                                                                                                  | Reserved<br>of a bus of<br>bus is in a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cycle and, along with M/IO and COD<br>TS state whenever one or both are Li<br>during bus hold acknowledge.                                                                                                                                                                                                                                                |        |

| <u>\$1,\$0</u> | 0    | defii                                                                                                                                                                                                                                                                                  | Cycle Status<br>neds the type                                                        | of bus cy                                                                               | initiation<br>ycle. The<br>float to 3                                                                                                                                       | Reserved  of a bus of bus is in a state OFF of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TS state whenever one or both are L                                                                                                                                                                                                                                                                                                                       |        |