#### 82C301, 82C302, 82A303, 82A304, 82A305, 82A306 CS8230: AT/386 CHIPSet™

- 100% IBM<sup>™</sup> PC AT compatible

- Flexible architecture allows usage in any iAPX 386<sup>™</sup> design

- Operates in Page mode with Interleave memory subsystem

- 16 MHz zero wait operation

The CS8230 AT/386 CHIPSet<sup>™</sup> is a seven chip VLSI implementation of most of the system logic to control an iAPX 386 based system. The CHIPSet is designed to offer a 100% PC AT compatible integrated solution. The flexible architecture of the CHIPSet allows it to be used in any iAPX386 based system design, such as CAD/CAE workstations, office systems, industrial and financial transaction systems.

CS8230 CHIPSet combined with CHIP's 82C206, Integrated Peripherals Controller, provides a complete PC AT compatible system using only 40 components plus memory devices.

- Independent clock to support correct AT bus timing

- 1MB to 16MB of DRAM memory support

- A complete PC AT requires only 40 IC's plus memory

The CS8230 CHIPSet<sup>™</sup> consists of one 82C301 Bus Controller, one 82C302 Page/ Interleave MemoryController, one each of 82A303 and 82A304 Address Bus Interfaces, two 82A305 Data Bus Interfaces, and a 82A306 Control Signal Buffer.

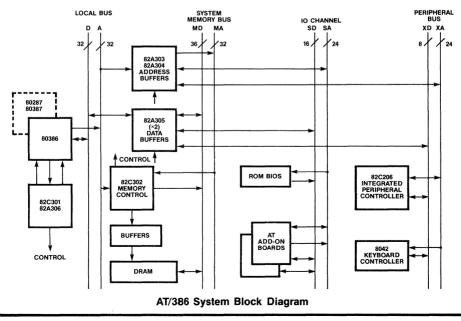

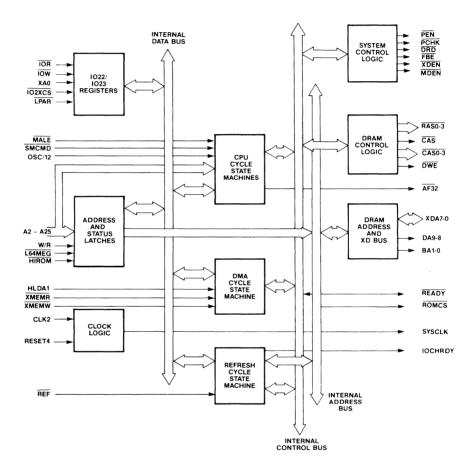

The CHIPSet supports a local CPU bus, a 32bit system memory bus, and AT buses as shown in the system diagram below. The 82C301 and 82A306 provide the generation and synchronization of control signals for all buses. The 82C301 also supports an independent AT bus clock, and allows for dynamic selection of the processor clock between the 16 MHz clock and the AT bus clock. The

## CHIP5

82A306 provides buffers for bus control signals in addition to other miscellaneous logic functions.

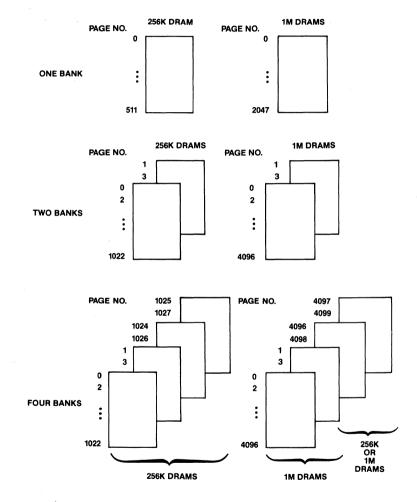

The 82C302 Page/Interleave Memory Controller provides an interleaved memory subsystem design with page mode operation. It supports 1 MB to 16 MB of DRAMs with combinations of 256Kbit and 1Mbit DRAMs. The processor can operate at 16 MHz with zero wait state memory accesses by using 100 nsec DRAMs.

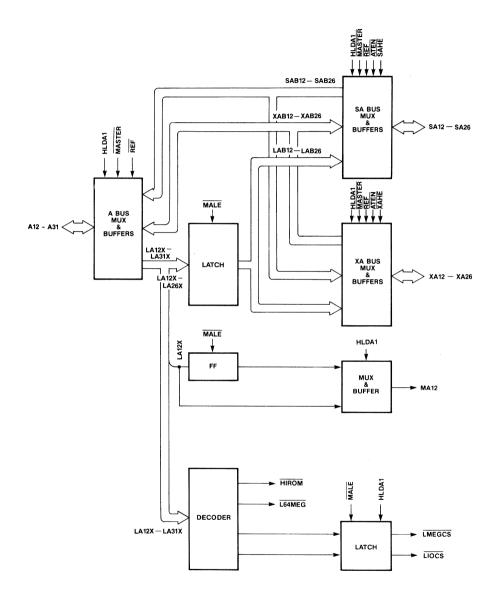

The 82A303 and 82A304 interface between all address buses, generate RAS/CAS addresses for the system memory and the addresses needed for proper data path conversion. Two 82A305 are used to interface between the local, system memory, and AT data buses. In addition to having high current drive, they also perform the conversion necessary between the different sized data paths.

#### **System Overview**

The CS 8230 is designed for use in 80386based systems and provides complete support for the IBM PC AT bus. There are four buses supported by the CS 8230 as shown in the AT/386 system block diagram: CPU local bus (A and D), system memory bus (MA and MD), IO Channel bus (SA and SD), and X bus (XA and XD). The system memory bus is used to interface to DRAM's controlled by the 82C302. The IO channel bus refers to the bus supporting the AT bus adapters which could be either a 8 bit devices or 16 bit devices. The X bus refers to the peripheral bus to which the DMA controllers and timers are attached in an IBM PC AT. The X bus has only an 8-bit data path. The term "AT bus" is used to refer to the IO channel bus and X bus. Provisions are also made for user extension of the IO channel to 32 bit bus.

#### Notation and Glossary

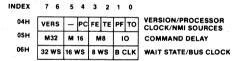

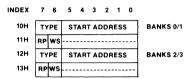

The following notations are used to refer to the configuration and diagnostic registers internal to the 82C301 and 82C302.

**REGnH** denotes the internal register with the index n in hexadecimal notation.

**REGnH** $\langle$ **x**:**y** $\rangle$  denotes the bit field from bits y to x of the internal register with the index n in hexadecimal notation.

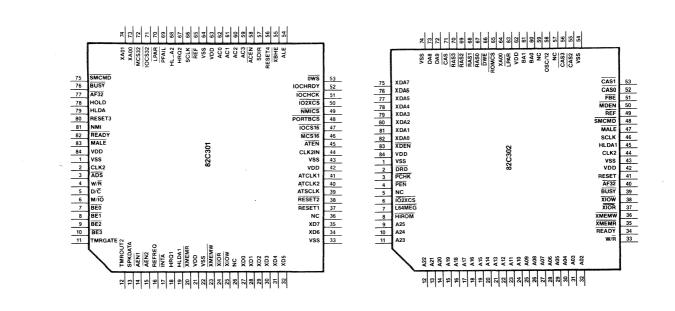

## 82C301 Pin Description

| Pin No. | Symbol | Pin<br>Type | Description                                                                                                                                                                                                                                                                     |

|---------|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks  |        |             |                                                                                                                                                                                                                                                                                 |

| 44      | CLK2IN | I           | CLOCK 2 INPUT from a packaged TTL crystal oscilla-<br>tor having twice the rated frequency of the processor.                                                                                                                                                                    |

| 2       | CLK2   | 0           | CLK2 output to the Clock 2 input of 80386 and the<br>memory controller. This clock output is derived from<br>CLK2IN and has a 50% duty cycle. The clock can also<br>be programmed to be the same as the BCLK.                                                                   |

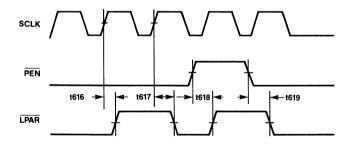

| 66      | SCLK   | 0           | SCLK is CLK2 divided by two and is an output gener-<br>ated as a reference to verify the phase relationship of<br>the internal clock and CLK2.                                                                                                                                  |

| 41      | ATCLK1 | I           | BUS CLOCK INPUT source from Crystal or Oscillator.<br>This clock input is used for the AT Bus operation and<br>is required only if the AT bus state machine clock<br>(BCLK) will not be derived from the CLK2 input. This<br>signal should be tied LO if not used.              |

| 40      | ATCLK2 | 0           | BUS CLOCK CRYSTAL OUTPUT is connected to the<br>crystal oscillator circuit if a packaged oscillator is not<br>used. A series resistor should be used to reduce the<br>amplitude of the resonant circuit. It should be left<br>unconnected if a packaged TTL oscillator is used. |

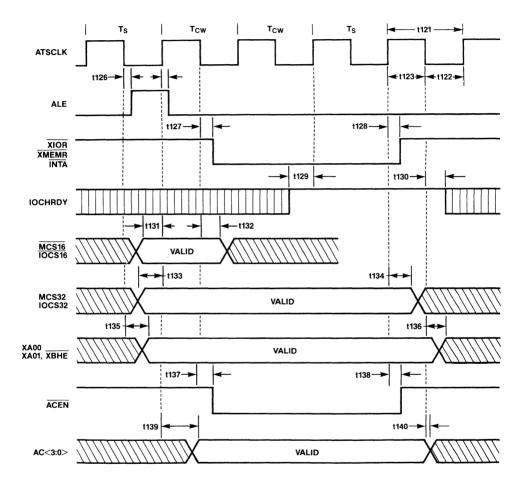

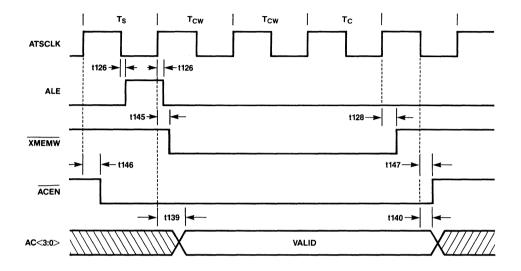

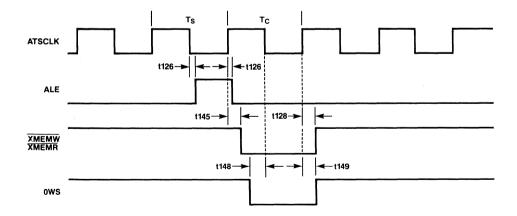

| 39      | ATSCLK | 0           | AT SYSTEM CLOCK is buffered to drive the clock<br>signal SYSCLK on the AT bus I/O channel. It is half<br>the frequency of BCLK and should have a nominal<br>value in the range of 6 to 8 MHz for maintaining<br>correct AT I/O bus timing with IBM PC AT.                       |

| Control |        |             |                                                                                                                                                                                                                                                                                 |

| 37      | RESET1 | I           | Active LO. RESET1 is connected to the power good signal generated by the PWRGOOD from the power supply. When LOW it will activate RESET3 and RESET4 for resetting the system.                                                                                                   |

| 38      | RESET2 | I           | Active LO. RESET2 (8042RC) is an active LOW signal generated from the keyboard controller 8042 for a "warm reset" not requiring the system power to be shut off. It forces a CPU reset by activating RESET3 signal.                                                             |

| 56      | RESET4 | 0           | Active HI. RESET4 is the System Reset used to reset<br>the AT Bus, 82C206 IPC, 8042 keyboard controller<br>82C302 or 82C312 memory controller. RESET4 is<br>synchronized with the processor clock.                                                                              |

| Pin No.   | Symbol  | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                 |

|-----------|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Inter | face    |             | · ·                                                                                                                                                                                                                                                                                                                                                         |

| 80        | RESET3  | Ο           | Active HI. RESET3 is the reset to the 80386 when RESET1 or RESET2 is active. This is also activated when shutdown condition in the CPU is detected.                                                                                                                                                                                                         |

| 82        | READY   | I/O         | Active LO. READY is driven LO during AT bus cycles<br>indicating that the current CPU bus cycle is to be<br>completed. It is also asserted if 'Time Out' condition is<br>detected. During all other cycles it is an input to<br>82C301. Ready is an open collector output requiring<br>an external pull up resistor. It connects to the 80386<br>READY pin. |

| 3         | ADS     | I           | Active LO. ADDRESS STATUS input connected to the 80386 ADS pin.                                                                                                                                                                                                                                                                                             |

| 4         | W/R     | I/O         | READ/WRITE STATUS input from the 80386 W/ $\overline{R}$ signal. It indicates a write bus cycle if it is HI and a read cycle if it is LO.                                                                                                                                                                                                                   |

| 5         | D/C     | I           | DATA/CONTROL STATUS input from the 80386 D/ $\overline{C}$ signal.                                                                                                                                                                                                                                                                                          |

| 6         | M/ĪŌ    | I           | MEMORY/IO STATUS input from the 80386 $M/\overline{IO}$ signal.                                                                                                                                                                                                                                                                                             |

| 78        | HOLD    | 0           | Active HI. HOLD REQUEST output to the 80386 HOLD<br>input pin. This signal is used to request the CPU to<br>relinquish the bus cycles to another requesting master<br>such as HRQ1, HRQ2 and REFREQ.                                                                                                                                                        |

| 79        | HLDA    | I           | Active HI. HOLD ACKNOWLEDGE input connected<br>to processor HLDA signal. When the signal is HIGH it<br>indicates that the processor has relinquished the<br>system bus in response to the HOLD request.                                                                                                                                                     |

| 10-7      | BE<3:0> | В           | Active LO. BYTE ENABLE signals input from the 80386 BE $\langle 3:0 \rangle$ during a CPU cycle. BE3 controls the most significant while BE0 controls the least significant byte. BE $\langle 3:0 \rangle$ are generated by 82C301 during DMA cycles based on the status signals XA0, XA1 and XBHE.                                                         |

| 81        | NMI     | 0           | Active HI. NON-MASKABLE INTERRUPT connects to the 80386 NMI pin and is generated by 82C301 to cause an NMI.                                                                                                                                                                                                                                                 |

\_\_\_\_\_

| Pin No.   | Symbol       | Pin<br>Type | Description                                                                                                                                                                                                                                                   |

|-----------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decodes   |              | -           |                                                                                                                                                                                                                                                               |

| 48        | PORTBCS      | I           | Active LO. PORT B CHIP SELECT is the address decode input from the 82A304 as enable for the Port B register at address 061H.                                                                                                                                  |

| 49        | NMICS        | I           | Active LO. NMI CHIP SELECT is the address decode<br>input from the 82A304 as enable for the NMI enable<br>bit at address 070H.                                                                                                                                |

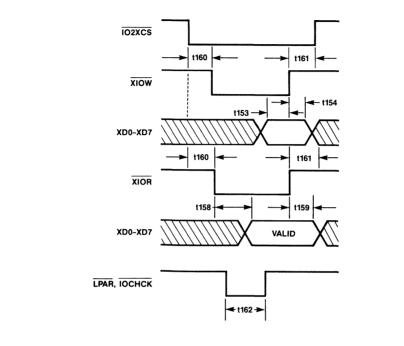

| 50        | IO2XCS       | I           | Active LO. IO2X CHIP SELECT is the address decode<br>input from the 82A304 as chip select for the IO regis-<br>ters at 022H and 023H used to access the 82C301<br>internal configuration registers.                                                           |

| 53        | OWS          | I           | Active LO. ZERO WAIT STATE acknowledge input<br>from the IO channel. When active it causes immediate<br>termination of the current AT bus memory or IO cycle.                                                                                                 |

| IO Channe | el Interface |             |                                                                                                                                                                                                                                                               |

| 52        | IOCHRDY      | ł           | Active HI. IO CHANNEL READY input from the AT<br>bus. When LOW it indicates a 'not ready' condition<br>and forces the insertion of wait states in I/O or<br>memory accesses. When HIGH it will allow the com-<br>pletion of the current memory or I/O access. |

| 51        | IOCHCK       | I           | Active LO. IO CHANNEL CHECK input from the AT<br>bus which causes an NMI to be generated if enabled.<br>It is used to signal an Error condition from a device<br>residing on the AT bus.                                                                      |

| 70        | LPAR         | 1           | Active LO. PARITY ERROR input from local memory system which causes an NMI to be geneated if enabled.                                                                                                                                                         |

| 69        | PFAIL        | 1           | Active LO. POWER FAIL WARNING signal input from the power supply.                                                                                                                                                                                             |

| 54        | ALE          | 0           | Active HI. ADDRESS LATCH ENABLE to AT bus. This<br>signal controls the address latches used to hold the<br>address during a bus cycle. The signal should be<br>buffered to drive the AT bus.                                                                  |

| DMA Inter | face         |             |                                                                                                                                                                                                                                                               |

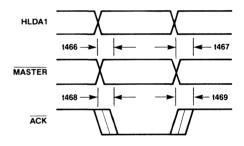

| 19        | HLDA1        | Ο           | Active HI. HOLD ACKNOWLEDGE 1 is active when a<br>bus cycle is granted in response to HRQ1.                                                                                                                                                                   |

| 68        | HLDA2        | 0           | Active HI. HOLD ACKNOWLEDGE 2 is active when a bus cycle is granted in response to HRQ2.                                                                                                                                                                      |

| Pin No.    | Symbol | Pin<br>Type | Description                                                                                                                                                                                               |

|------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18         | HRQ1   | I           | Active HI. HOLD REQUEST 1 is active when a DMA/<br>Master is requesting a bus cycle. For an AT compatible<br>architecture it should be connected to the HOLD<br>REQUEST signal from DMA1 and DMA2.        |

| 67         | HRQ2   | I           | Active HI. HOLD REQUEST 2 is active when a DMA/<br>Master is requesting a bus cycle. This should be<br>grounded if not used.                                                                              |

| 14         | AEN1   | I           | Active LO. ADDRESS ENABLE for 8 bit DMA transfers.                                                                                                                                                        |

| 15         | AEN2   | I           | Active LO. ADDRESS ENABLE for 16 bit DMA transfers.                                                                                                                                                       |

| Control S  | trobes |             |                                                                                                                                                                                                           |

| 46         | MCS16  | I           | Active LO. MCS16 When active causes 16 bit memory accesses on IO channel.                                                                                                                                 |

| 72         | MCS32  | I           | Active LO. MCS32 when active causes 32 bit memory accesses on IO channel.                                                                                                                                 |

| 47         | IOCS16 | I           | Active LO. IOCS16 when active causes 16 bit IO accesses on IO channel.                                                                                                                                    |

| 71         | IOCS32 | I           | Active LO. IOCS32 when active causes 32 bit IO accesses on IO channel.                                                                                                                                    |

| 75         | SMCMD  | 0           | Active LO. SYSTEM MEMORY COMMAND when active indicates the current access cycle is a memory cycle.                                                                                                        |

| Refresh    | 22     |             |                                                                                                                                                                                                           |

| 16         | REFREQ | I           | Active HI. REFresh REQuest when active initiates a DRAM refresh sequence be initiated. This signal is obtained from the timer controller, 8254, in a PC AT implementation.                                |

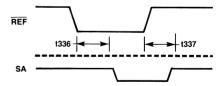

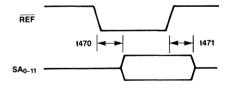

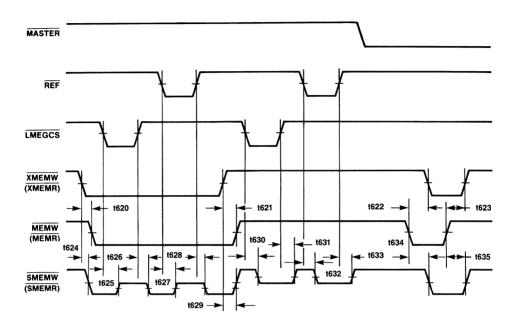

| 65         | REF    | I/O         | Active LO. REFresh is an open drain signal. It initiates<br>a refresh cycle for the DRAMs. As an input it can be<br>used to force a refresh cycle from an I/O device. An<br>external pull up is required. |

| X Bus Inte | erface |             |                                                                                                                                                                                                           |

| 20         | XMEMR  | I/O         | Active LO. X BUS MEMORY READ is a control strobe<br>directing memory to place data on the data bus. It is<br>sourced either from the 82C301 when the 80386 is the<br>master or from the DMA.              |

| Pin No.  | Symbol  | Pin<br>Type | Description                                                                                                                                                                                      |

|----------|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23       | XMEMW   | I/O         | Active LO. X BUS MEMORY WRITE is a control strobe<br>directing memory to accept data from the data bus. It<br>is sourced either from the 82C301 when the 80386 is<br>the master or from the DMA. |

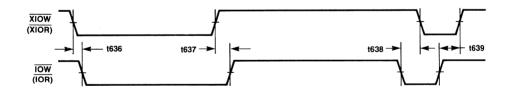

| 24       | XIOR    | I/O         | Active LO. X BUS IO READ is a control strobe direct-<br>ing an IO port to place data on the data bus. It is<br>sourced either from the 82C301 when the 80386 is the<br>master or from the DMA.   |

| 25       | XIOW    | 1/0         | Active LO. X BUS IO WRITE is a control strobe<br>directing an IO port to accept data from the data bus.<br>It is sourced either from the 82C305 when the 80386 is<br>the master or from the DMA. |

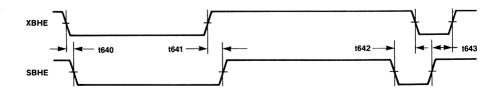

| 55       | XBHE    | I/O         | Active LO. X BUS BYTE HIGH ENABLE indicates that<br>the high byte (bits <15:08>) on the bus has valid data.<br>It is sourced from the 82C301 when 80386 or DMA2<br>(16 bit) is the master.       |

| 35-34    | XD<7:6> | I/O         | X DATA BUS bits <7:6>                                                                                                                                                                            |

| 32-27    | XD<5:0> | I/O         | X DATA BUS bits <5:0>                                                                                                                                                                            |

| 57       | SDIR    | 0           | SYSTEM BUS DIRECTION controls the direction of data transfer between the IO channel and the local bus. When LO the it enables data transfer from the IO channel to local bus.                    |

| 58       | ACEN    | 0           | Active LO. ACTION CODE ENABLE when active vali-<br>dates the action code signals AC<3:0>.                                                                                                        |

| 59-62    | AC<3:0> | 0           | ACTION CODE is a four-bits encoded command for<br>bus size control and byte assembly operations per-<br>formed by the 82A305s.                                                                   |

| Memory C | Control |             |                                                                                                                                                                                                  |

| 77       | AF32    | I           | Active LO. AF32 when active indicates that a bus cycle<br>is a local bus access without any data size conversion<br>or AT cycle simulation treated as a 32-bit access.                           |

| 76       | BUSY    | i           | Active LO. BUSY from memory controller.                                                                                                                                                          |

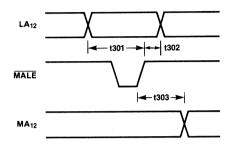

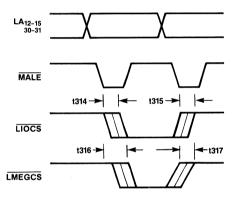

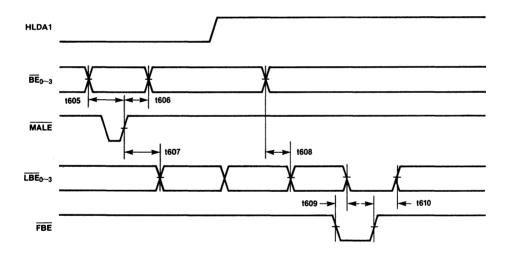

| 83       | MALE    | 0           | Active LO. Address Latch Enable for accesses to on board memory/IO. It also indicates start of a new CPU cycle.                                                                                  |

| 11       | TMRGATE | 0           | Active HI. TIMER GATE signal enables the timer on 8254 Timer to generate the tone signal for the speaker.                                                                                        |

| 12       | TMROUT2 | I           | Active HI. TIMER OUT 2 is the output from the timer 8254. It can be read from port B.                                                                                                            |

| Pin No.             | Symbol            | Pin<br>Type | Description                                                                              |

|---------------------|-------------------|-------------|------------------------------------------------------------------------------------------|

| 13                  | SPKDATA           | 0           | Active HI. SPEAKER DATA is used to gate the 8254 tone signal to the speaker.             |

| 17                  | INTA              | 0           | Active LO. Interrupt acknowledge output to the inter-<br>rupt controller.                |

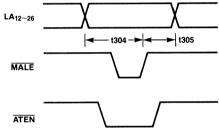

| 45                  | ATEN              | 0           | Active LO. AT ENABLE when active indicates the current CPU access is an AT bus cycle.    |

| 73                  | XA00              | I/O         | Address bit 0. It is sourced from the 82C301 when 80386 or DMA (16 bit) is a bus master. |

| 74                  | XA01              | 1/0         | Address but 1. It is sourced from the 82C301 when 80386 is a bus master.                 |

| 26,36               | NC                |             | Reserved                                                                                 |

| 21,42<br>63,84      | VDD<br>VDD        |             | Power                                                                                    |

| 1<br>22,33<br>43,64 | VSS<br>VSS<br>VSS |             | Ground                                                                                   |

### 82C302 Pin Description

| Pin No.   | Symbol    | Pin<br>Type | Description                                                                                                                                                                                                                            |

|-----------|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks an | d Control |             |                                                                                                                                                                                                                                        |

| 44        | CLK2      | I           | Processor Clock                                                                                                                                                                                                                        |

| 46        | SCLK      | 0           | Generated CLK2/2 for reference.                                                                                                                                                                                                        |

| 41        | RESET     | I           | Active HI. When active resets 82C302                                                                                                                                                                                                   |

| 49        | REF       | I           | Active LO. DRAM refresh control signal.                                                                                                                                                                                                |

| 47        | MALE      | I           | Active LO. Address Latch Enable                                                                                                                                                                                                        |

| 33        | W/R       | I           | System WRITE/READ status input                                                                                                                                                                                                         |

| 48        | SMCMD     | I           | Active LO. System Memory Command. Indicates that the current command is for memory.                                                                                                                                                    |

| 37        | XIOR      | I           | Active LO. I/O READ command used to qualify IO2XCS.                                                                                                                                                                                    |

| 38        | XIOW      | İ           | Active LO. I/O WRITE command used to qualify IO2XCS.                                                                                                                                                                                   |

| 35        | XMEMR     | I           | Active LO. X Bus memory READ command.                                                                                                                                                                                                  |

| 36        | XMEMW     | I ,         | Active LO. X Bus memory WRITE command.                                                                                                                                                                                                 |

| 45 ·      | HLDA1     | I           | Active HI. HOLD ACKNOWLEDGE 1 input from 82C301.                                                                                                                                                                                       |

| 63        | LPAR      | I           | Active LO. Parity error indication during a DRAM read. The failing address will be latched inside the chip for diagnostic purposes.                                                                                                    |

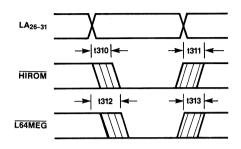

| 8         | HIROM     | l           | Active LO. High ROM address chip select asserted<br>when the highest 16 MBytes of memory is addressed<br>(A<31:A24>=FFH). Unlatched. This is used in conjunc-<br>tion with the remaining address bits to generate the<br>ROMCS signal. |

| 7         | L64MEG    | I           | Active LO. Low 64M address that is asserted when A<31:26>=00H. Unlatched.                                                                                                                                                              |

| 65        | ROMCS     | 0           | Active LO. Chip select for the BIOS EPROMs that is qualified with $W/\overline{R}$ and SMCMD.                                                                                                                                          |

| 6         | IO2XCS    | I           | Active LO. IO address 22 and 23 chip selects. I/O port 22 is the index register for the configuration register set and and I/O 23 is accessed as the 8 bit configuration register selected by the index written to I/O port 22.        |

| 09-32     | A<25:02>  | I           | Address from the CPU local bus.                                                                                                                                                                                                        |

| 64        | XA00      | I           | Address from the X Bus                                                                                                                                                                                                                 |

| 82C302 | Pin | Description | (Continued) |  |

|--------|-----|-------------|-------------|--|

|--------|-----|-------------|-------------|--|

| Pin No.        | Symbol               | Pin<br>Type | Description                                                                                                                                                                                                                                               |

|----------------|----------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34             | READY                | I/O         | Active LO. System ready indicating the end of current 386 bus cycle. It goes inactive when the requested memory transfer has been completed. It becomes an input when the current bus cycle is for the AT IO expansion channel ( $\overline{AF32} = 0$ ). |

| 39             | BUSY                 | 0           | Active LO. Indicates that the memory controller is still<br>servicing a previous request. This should be connected<br>to IOCHRDY through an open collector buffer. This<br>signal should not be confused with the BUSY of<br>80386.                       |

| 40             | AF32                 | Ο           | Active LO, open drain. If asserted indicates that the<br>current address is for local memory on the system<br>board (DRAM or possibly EPROM). Otherwise the<br>current address is assumed to be on the AT IO<br>channel.                                  |

| Memory E       | xpansion             |             |                                                                                                                                                                                                                                                           |

| 61-60          | BA<1:0>              | 0           | Addresses that may be externally decoded to gate<br>RAS to the correct block of 4 banks of DRAMs. These<br>will always be zero.                                                                                                                           |

| 2              | DRD                  | 0           | Active LO. DRAM Read controls the direction of data<br>transfer between the DRAM and local bus. When LO it<br>controls the transfer from the memory data bus toward<br>CPU and from the CPU to memory otherwise.                                          |

| DRAM Int       | erface               |             |                                                                                                                                                                                                                                                           |

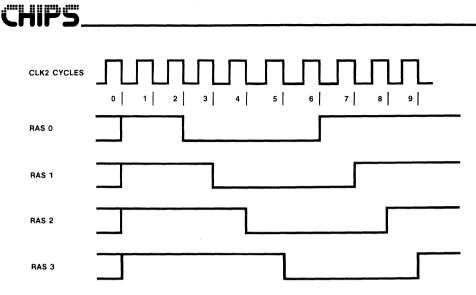

| 70-67          | RAS<3:0>             | 0           | Active LO. Row Address Strobe. There is one for each bank.                                                                                                                                                                                                |

| 71             | CAS                  | 0           | Active LO. Column Address Strobe. Used to latch data in the 82A305 data buffer.                                                                                                                                                                           |

| 56-55<br>53-52 | CAS<3:2><br>CAS<1:0> | 0           | Active LO. Column Address Strobe. A strobe per bank<br>that must be externally gated with byte enables for<br>each byte of DRAM chips.                                                                                                                    |

| 58             | OSC/12               | I           | 1.19MHz Clock input used for RAS pulse width time-<br>out. Replaces CA3 on Cache controller.                                                                                                                                                              |

| 66             | DWE                  | 0           | Active LO. DRAM Write Enable.                                                                                                                                                                                                                             |

| 51             | FBE                  | 0           | Active LO. Force Byte Enable. Will always be inactive.                                                                                                                                                                                                    |

| 72-73          | DA<9:8>              | 0           | Remaining DRAM address bits.                                                                                                                                                                                                                              |

| Pin No.       | Symbol     | Pin<br>Type | Description                                                                                                                                                                                                                                       |

|---------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75-82         | XDA<7:0>   | Ι/Ο         | Multiplexed bidirectional data pins for $XD < 7:0>$ . DA $< 7:0>$ are the lower address bits for the DRAM array.                                                                                                                                  |

| 83            | XDEN       | 0           | Active LO. XD bus buffer Enable. XDEN is asserted<br>during IO access cycles to 022H and 023H if 022H<br>access is for an internal register of 82C302. XDEN is<br>used to control the chip enable for the buffer between<br>the XD and XDA buses. |

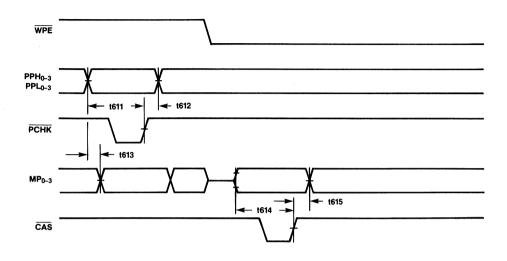

| 3             | РСНК       | 0           | Active LO. Parity Check Strobe.                                                                                                                                                                                                                   |

| 4             | PEN        | 0           | Active LO. Overall Parity Enable.                                                                                                                                                                                                                 |

| 50            | MDEN       | 0           | Active LO. MEMORY DATA BUFFER ENABLE. This signal is by default always LO and is connected to MDEN of 82A305.                                                                                                                                     |

| Miscellane    | eous       |             |                                                                                                                                                                                                                                                   |

| 5,57,59       | NC         |             | Reserved                                                                                                                                                                                                                                          |

| 42,62,84      | VDD        |             | Power                                                                                                                                                                                                                                             |

| 1,43<br>54,74 | VSS<br>VSS |             | Ground                                                                                                                                                                                                                                            |

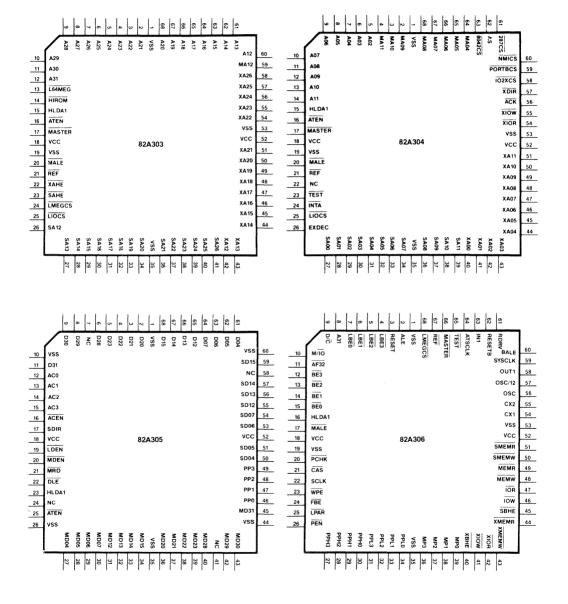

#### 82A303 Pin Description

| Pin No.   | Symbol         | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control   |                |             |                                                                                                                                                                                                                                                                                                                                                                                       |

| 17        | MASTER         | I           | Active LO. Bus MASTER is generated by a device that<br>is active on the expansion bus. After MASTER is force<br>LO by an I/O device, the I/O CPU must wait for one<br>system clock period before forcing the address and<br>data lines. MASTER must not be held LO for more than<br>15 microseconds, or else data in the system memory<br>may be lost due to lack of a refresh cycle. |

| 15        | HLDA1          | I           | Active HI. HOLD ACKNOWLEDGE from 82C301.                                                                                                                                                                                                                                                                                                                                              |

| 20        | MALE           | I           | Active LO. MEMORY ADDRESS LATCH ENABLE clocks addresses into the address registers on the rising edge.                                                                                                                                                                                                                                                                                |

| 21        | REF            | I           | Active LO. REFRESH. Schmitt Trigger.                                                                                                                                                                                                                                                                                                                                                  |

| 16        | ATEN           | I           | Active LO. AT BUS ENABLE is active when the CPU makes an AT bus access.                                                                                                                                                                                                                                                                                                               |

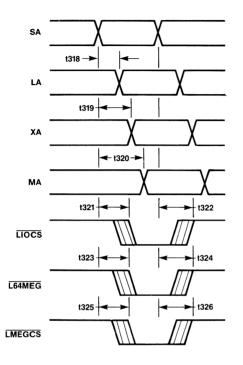

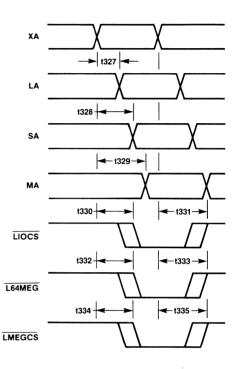

| 25        | LIOCS          | 0           | Active LO. LOW IO ADDRESS CHIP SELECT is as-<br>serted when A<15:12>=0.                                                                                                                                                                                                                                                                                                               |

| 24        | LMEGCS         | 0           | Active LO. LOW 1 MB SELECT is active when the access address decodes to the low 1MB address space: $A < 31:20 > = 0$ .                                                                                                                                                                                                                                                                |

| 13        | L64MEG         | 0           | Active LO. LOW 64 MB SELECT is active when the access address decodes to the low 64MB address space: A<31:26> = 0.                                                                                                                                                                                                                                                                    |

| 14        | HIROM          | 0           | Active LO. HI ROM SELECT is active when A<31:26> = 3FH.                                                                                                                                                                                                                                                                                                                               |

| Processor | /Bus Interface |             |                                                                                                                                                                                                                                                                                                                                                                                       |

| 12-2      | A<31:21>       | I/O         | Local Address Bus                                                                                                                                                                                                                                                                                                                                                                     |

| 68-60     | A<20:12>       | I/O         | LUCAI AUGIESS DUS                                                                                                                                                                                                                                                                                                                                                                     |

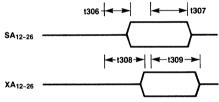

| 58-54     | XA<26:22>      | 1/0         | X Address Bus                                                                                                                                                                                                                                                                                                                                                                         |

| 51-42     | XA<21:12>      | I/O         |                                                                                                                                                                                                                                                                                                                                                                                       |

| 22        | XAHE           | I           | Active LO. Enable bits 26:24 from the XA bus. A pullup is provided so that the input can be left open if only 24 bits are sourced externally.                                                                                                                                                                                                                                         |

| 41-36     | SA<26:21>      | 1/0         | 24mA. System Address Bus                                                                                                                                                                                                                                                                                                                                                              |

| 34-26     | SA<20:12>      | I/O         | 24117. System Audress bus                                                                                                                                                                                                                                                                                                                                                             |

| Pin No.       | Symbol     | Pin<br>Type | Description                                                                                                                                   |

|---------------|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 23            | SAHE       | I           | Active LO. Enable bits 26:24 from the SA bus. A pullup is provided so that the input can be left open if only 24 bits are sourced externally. |

| 59            | MA12       | 0           | Memory Address Bus Latched on the trailing edge of MALE.                                                                                      |

| Miscellane    | eous       |             |                                                                                                                                               |

| 18,52         | VCC        |             | Power                                                                                                                                         |

| 1,19<br>35,53 | VSS<br>VSS |             | Ground                                                                                                                                        |

.

## 82A304 Pin Description

| Pin No. | Symbol        | Pin<br>Type | Description                                                                                                                                                                                                         |

|---------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control |               |             |                                                                                                                                                                                                                     |

| 17      | MASTER        | I           | Active LO. BUS MASTER is generated by a device active on the expansion bus.                                                                                                                                         |

| 15      | HLDA1         | 1           | Active HI. HOLD ACKNOWLEDGE 1 from 82C301.                                                                                                                                                                          |

| 20      |               |             | Active LO. MEMORY ADDRESS LATCH ENABLE clocks addresses into the address registers on the rising (trailing) edge.                                                                                                   |

| 21      | REF           | I           | Active LO. REFRESH Schmitt trigger.                                                                                                                                                                                 |

| 16      | ATEN          | I           | Active LO. AT BUS ENABLE is active when the CPU makes an AT bus access.                                                                                                                                             |

| 25      | LIOCS         | I           | Active LO. LOW IO ADDRESS CHIP SELECT.                                                                                                                                                                              |

| 54      | XIOR          | l           | Active LO. X BUS IO Read.                                                                                                                                                                                           |

| 55      | XIOW          | I           | Active LO. X BUS IO Write                                                                                                                                                                                           |

| 57      | XDIR          | 0           | X BUS DIRECTION is used to control the drivers<br>between the X bus and S bus. The drivers should be<br>used such that S bus signals are driven toward X bus<br>when XDIR is LO and in the other direction when HI. |

| 26      | EXDEC         | <b>I</b> .  | Active HI. EXTENDED IO DECODE. A strapping option that when LO ignores $A<11:10>$ and LIOCS (which is decoded based on $A<15:12>$ ) for decoding the system board IO ports. An internal pullup is provided.         |

| 58      | <b>IO2XCS</b> | 0           | Active LO. IO 2x SELECT is decode of IO address 022H or 023H.                                                                                                                                                       |

| 63      | 8042CS        | 0           | Active LO. 8042 SELECT is decode of 8042 address at 060H or 064H.                                                                                                                                                   |

| 59      | PORTBCS       | 0           | Active LO. PORTB SELECT is decode of Port B address at 061H                                                                                                                                                         |

| 60      | NMICS         | 0           | Active LO. NMI SELECT is decode of NMI address at 070H.                                                                                                                                                             |

| 61      | 287CS         | 0           | Active LO. 80287 SELECT is decode of 287 address at 0E0-0FFH.                                                                                                                                                       |

| 56      | ACK           | 0           | Active LO. ACKNOWLEDGE indicates that AEN1 OR<br>AEN2 has been asserted. This signal is used to gener-<br>ate AEN signal on the AT I/O channel.                                                                     |

| 62      | AS            | 0           | Active HI. Address Strobe for the RTC. IO address 7xH is conditioned with XIOW.                                                                                                                                     |

| Pin No.       | Symbol         | Pin<br>Type | Description                                                                           |  |  |  |

|---------------|----------------|-------------|---------------------------------------------------------------------------------------|--|--|--|

| 24 INTA I     |                |             | Active LO. INTERRUPT ACKNOWLEDGE bus cycle<br>indication.                             |  |  |  |

| Processor     | /Bus Interface |             |                                                                                       |  |  |  |

| 14-5          | A<11:02>       | I/O         | Local address                                                                         |  |  |  |

| 51-40         | XA<11:00>      | I/O         | X bus address                                                                         |  |  |  |

| 39-36         | SA<11:08>      | 1/0         | 24mA. System address                                                                  |  |  |  |

| 34-27         | SA<07:00>      | I/O         | 24IIA. System address                                                                 |  |  |  |

| 4-2           | MA<11:09>      | 0           | Memory address                                                                        |  |  |  |

| 68-64         | MA<08:04>      | 0           | Memory address                                                                        |  |  |  |

| 23            | TEST           | I           | Active LO. TEST when active resets the refresh counter to zero. A pullup is provided. |  |  |  |

| 22            | NC             |             | Reserved                                                                              |  |  |  |

| Miscellane    | eous           |             |                                                                                       |  |  |  |

| 18,52         | VCC            |             | Power                                                                                 |  |  |  |

| 1,19<br>35,53 | VSS<br>VSS     |             | Ground                                                                                |  |  |  |

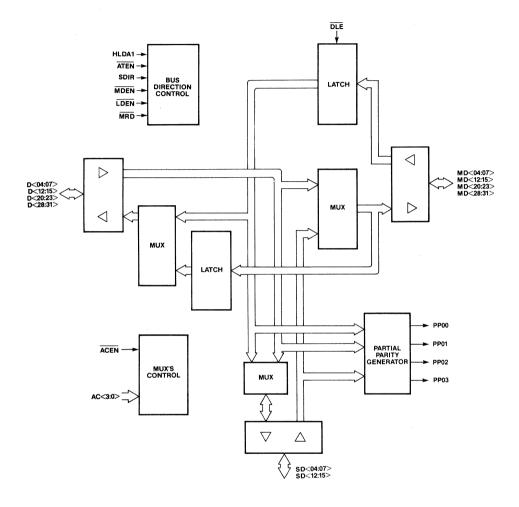

## 82A305 Pin Description

| Pin No. | Symbol  | Pin<br>Type | Description                                                                                                                                                                                                                       |

|---------|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control |         |             |                                                                                                                                                                                                                                   |

| 15-12   | AC<3:0> | I           | Action Code (bus size/assembly command)                                                                                                                                                                                           |

| 16      | ACEN    | I           | Active LO. Action Code Enable when active validates the action codes.                                                                                                                                                             |

| 17      | SDIR    | I           | System bus DIRection. When LO enables data transfers from the System to Local busn and in the other direction otherwise.                                                                                                          |

| 25      | ATEN    | I           | Active LO. AT bus ENable                                                                                                                                                                                                          |

| 23      | HLDA1   | I           | Active HI. HoLD Acknowledge.                                                                                                                                                                                                      |

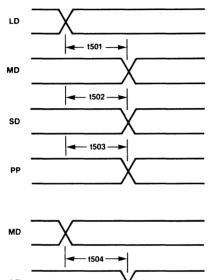

| 20      | MDEN    | 1           | Active LO. MEMORY DATA BUFFER ENABLE. When<br>LO enables the memory data buffers for transfer<br>between the processor and memory subsystem. When<br>HI disables these bus buffers. Should be connected to<br>MDEN on the 82C302. |

| 19      | LDEN    | I           | Active LO. Selects LD as a source for the SD bus<br>during MASTER or DMA reads. When HI selects MD.<br>Asserting MRD overrides LDEN and gates MD to the<br>SD bus. A pullup is provided.                                          |

| 21      | MRD     | I           | Active LO. Memory Bus DIRection. When LO enables data movement for a processor read from the memory to local bus. MRD when HI enables drivers from local to memory bus.                                                           |

| 22      | DLE     | I           | Active LO. Data Latch Enable.                                                                                                                                                                                                     |

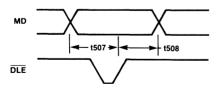

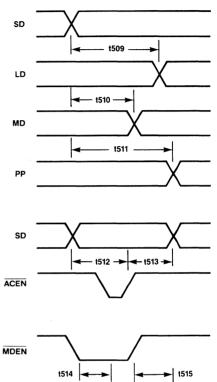

**Data Paths** (Bit numbers are for the upper 4 bits slice of each byte and should be 4 less for the lower nibble slice).

| 11, 9<br>8, 6<br>5-2<br>68-65<br>64-61    | D<31:30><br>D<29:28><br>D<23:20><br>D<15:12><br>D<07:04>      | I/O<br>I/O<br>I/O<br>I/O        | Local Data Bus        |

|-------------------------------------------|---------------------------------------------------------------|---------------------------------|-----------------------|

| 45,43<br>42,40<br>39-36<br>34-31<br>30-27 | MD<31:30><br>MD<29:28><br>MD<23:20><br>MD<15:12><br>MD<07:04> | I/O<br>I/O<br>I/O<br>I/O<br>I/O | Memory Data Bus       |

| 49-46                                     | PP<03:00>                                                     | 0                               | Memory Partial Parity |

| Pin No.                          | Symbol                                           | Pin<br>Type              | Description         |

|----------------------------------|--------------------------------------------------|--------------------------|---------------------|

| 59,57<br>56,55<br>54-53<br>51-50 | SD<15:14><br>SD<13:12><br>SD<07:06><br>SD<05:04> | 1/0<br>1/0<br>1/0<br>1/0 | IO Channel Data Bus |

| 7,24<br>41,58                    | NC<br>NC                                         |                          | Reserved.           |

| Power Sup                        | oplies                                           |                          |                     |

| 18,52                            | VCC                                              |                          | Power               |

| 1,10<br>26,35<br>44,60           | VSS<br>VSS<br>VSS                                |                          | Ground              |

#### 82A306 Pin Description

| Pin No. | Symbol   | Pin<br>Type | Description                                                                                                                                                                       |  |

|---------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 64      | ATSCLK   | 1           | AT IO channel SYSCLK input.                                                                                                                                                       |  |

| 59      | SYSCLK   | 0           | 24mA. Buffered SYSCLK to AT IO channel. Nominally<br>one half of the bus state machine clock frequency.                                                                           |  |

| Control |          |             |                                                                                                                                                                                   |  |

| 54      | CX1      | I           | 14.318MHz oscillator input from crystal.                                                                                                                                          |  |

| 55      | CX2      | 0           | 14.318MHz oscillator output to crystal.                                                                                                                                           |  |

| 56      | OSC      | 0           | 24mA. System 14.318MHz output.                                                                                                                                                    |  |

| 57      | OSC/12   | 0           | 24mA. 14.318MHz/12 = 1.19MHz output.                                                                                                                                              |  |

| 17      | MALE     | l           | Active LO. Address Latch Enable for on board access.                                                                                                                              |  |

| 12-15   | BE<3:0>  | ł           | Active LO. BYTE ENABLE.                                                                                                                                                           |  |

| 4-7     | LBE<3:0> | 0           | Active LO. LATCHED BYTE ENABLE on the trailin<br>edge of MALE.                                                                                                                    |  |

| 24      | FBE      | I           | Active LO. FORCE BYTE ENABLE Forces all byte<br>enables LBE active independent of MALE and the<br>BE<3:0> inputs.                                                                 |  |

| 67      | REF      | I           | Active LO. REFRESH.                                                                                                                                                               |  |

| 8       | A<31>    | I           | Local Address Bus bit 31.                                                                                                                                                         |  |

| 10      | M/IO     | I           | 80386 Status used to generate $\overline{\text{AF32}}$ for the 80387 and other 32 bit IO devices.                                                                                 |  |

| 9       | D/C      | I           | 80386 Status used to generate AF32 for the 80387 and other 32 bit IO devices.                                                                                                     |  |

| 68      | LMEGCS   | 1           | Active LO. LOW MEGABYTE CHIP SELECT.                                                                                                                                              |  |

| 11      | AF32     | 0           | Active LO, Tri-state output. $\overline{AF32}$ when active indicates<br>a local bus memory access cycle on the system board.<br>It is generated from M/IO, D/C, A<31>, and HLDA1. |  |

| 66      | MASTER   | I           | Active LO. Bus MASTER input from the AT IO channel.                                                                                                                               |  |

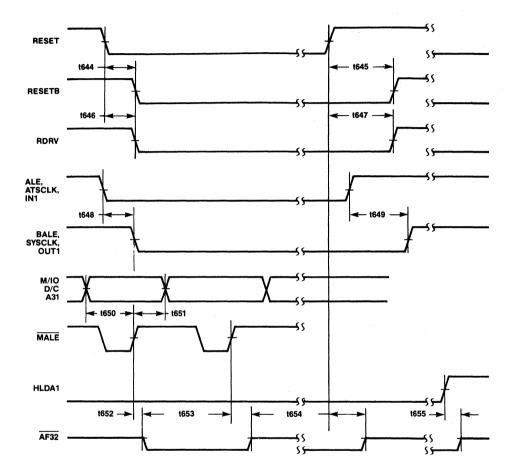

| 3       | RESET    | 1           | Active HI. RESET input. Should be connected to RESET4 of 82C301.                                                                                                                  |  |

| 62      | RESETB   | 0           | Active HI. Buffered RESET to X bus.                                                                                                                                               |  |

| 61      | RDRV     | 0           | Active HI. 24mA. RESET to AT bus.                                                                                                                                                 |  |

| 2       | ALE      | I           | Active HI. ALE for AT bus.                                                                                                                                                        |  |

| 40      | XBHE     | I/O         | Active LO. X Bus BHE.                                                                                                                                                             |  |

| 44      | XMEMR    | I/O         | Active LO. X Bus Memory Read.                                                                                                                                                     |  |

| 43      | XMEMW    | I/O         | Active LO. X Bus Memory Write.                                                                                                                                                    |  |

| Pin No.       | Symbol     | Pin<br>Type | Description                                                                                                       |  |

|---------------|------------|-------------|-------------------------------------------------------------------------------------------------------------------|--|

| 42            | XIOR       | I/O         | Active LO. X Bus IO Read.                                                                                         |  |

| 41            | XIOW       | I/O         | Active LO. X Bus IO Write.                                                                                        |  |

| 60            | BALE       | 0           | Active HI. 24mA. Buffered ALE to AT bus.                                                                          |  |

| 45            | SBHE       | I/O         | Active LO. 24mA. System bus BHE.                                                                                  |  |

| 51            | SMEMR      | 0           | Active LO. 24mA. System bus MEMory Read.                                                                          |  |

| 50            | SMEMW      | 0           | Active LO. 24mA. System bus MEMory Write.                                                                         |  |

| 49            | MEMR       | I/O         | Active LO. 24mA. Memory Read.                                                                                     |  |

| 48            | MEMW       | I/O         | Active LO. 24mA. Memory Write.                                                                                    |  |

| 47            | IOR        | I/O         | Active LO. 24mA. IO Read.                                                                                         |  |

| 46            | ĪOW        | I/O         | Active LO. 24mA. IO Write.                                                                                        |  |

| 16            | HLDA1      | I           | Active HI. HOLD ACKNOWLEDGE from 82C301.                                                                          |  |

| 22            | SCLK       | I           | CLK2/2 clock input. Should be connected to SCL output of 82C302.                                                  |  |

| 27-30         | PPH<3:0>   | I           | PARTIAL PARITY HIGH computed by 82A305 for the high nibble data bits.                                             |  |

| 31-34         | PPL<3:0>   | 1           | PARTIAL PARITY LOW computed by 82A305 for the<br>low nibble data bits.                                            |  |

| 36-39         | MP<3:0>    | I/O         | Data Parity bits for the DRAMs.                                                                                   |  |

| 21            | CAS        | I           | Active LO. Read Parity latch enable.                                                                              |  |

| 20            | РСНК       | I           | Active LO. PARITY CHECK STROBE for generating LPAR from the partial parity and data parity bits.                  |  |

| 26            | PEN        | l           | Active LO. Overall PARITY CHECK ENABLE.                                                                           |  |

| 23            | WPE        | Ι           | Active LO. WRITE PARITY ENABLE. Enables the<br>sourcing of write parity onto the MP bus. A pullup is<br>provided. |  |

| 25            | LPAR       | 0           | Active LO. LATCHED PARITY ERROR signal.                                                                           |  |

| 65            | TEST       | 1           | Active LO. Enables testing of the OSC/12 counter. A pullup is provided.                                           |  |

| 63            | IN1        | Ι.          | Input to an uncommitted 24mA non-inverting buffer.                                                                |  |

| 58            | OUT1       | 0           | 24mA. Output of the IN1 buffer.                                                                                   |  |

| Power Su      | oply       |             | · · · · ·                                                                                                         |  |

| 18,52         | VCC        |             | Power                                                                                                             |  |

| 1,19<br>35,53 | VSS<br>VSS |             | Ground                                                                                                            |  |

#### 82C301 BUS CONTROLLER

- Optional Independent AT Bus Clock

- Processor Clock Selection

- AT Bus Timing Configuration

- CPU Interface and Bus Control

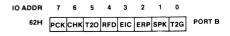

- Port B Register

#### OVERVIEW

The 82C301 provides a clock generation circuitry to solve two basic problems. One is to provide system designers the choice of a particular AT bus clock most adequate for their applications. The other is to allow the processor to run at the full speed and optionally at a speed to match timing dependent application software. Because many AT adapter boards are designed with built in timing assumptions, independent programmable controls are provided for AT bus command timing and wait state generation for IO accesses and for 8, 16, and 32 bit memory accesses.

The 82C301 interfaces directly with the 80386 and implements the state machines required for controlling all bus accesses. It also features a status register known as Port B register used in a standard IBM PC AT.

#### FUNCTIONAL DESCRIPTION

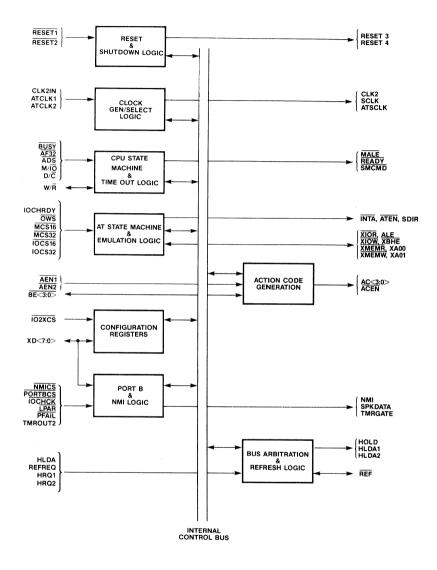

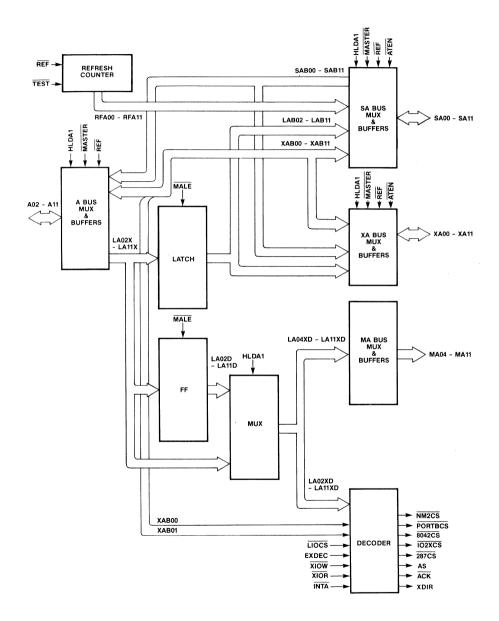

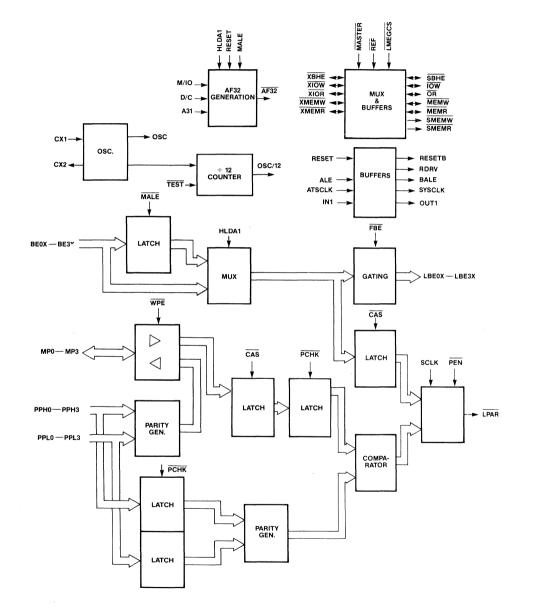

The 82C301 has the following function blocks as illustrated in figure 1-1:

- Clock generation and reset control

- CPU bus access state machine

- AT bus access state machine

- Port B register and NMI logics

- Bus Arbitration and refresh logic

#### **Clock Generation and Reset Control**

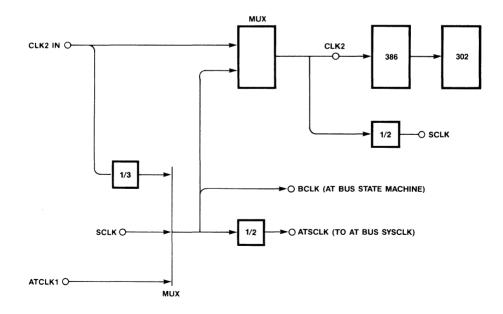

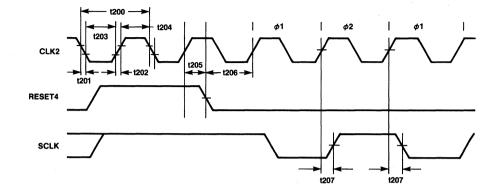

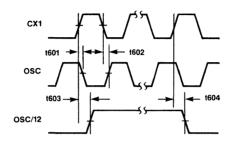

The 82C301 provides three major system clocks: the processor clock CLK2, the BCLK clock for AT bus state machine of 82C301, and the AT bus clock SYSCLK. The BCLK

(SYSCLK  $\times$  2) is a clock internal to the 82C301 and is used in this document to describe the system operation.

The clock generation circuitry shown in figure 1-2 contains two external clocks CLK2IN and ATCLK1 used as selectable clock sources. CLK2IN is assumed to be greater than 20MHz and should come from a packaged crystal oscillator while an oscillator circuit is provided for the ATCLK1 signal so that it can be connected to either a packaged oscillator or a crystal. This ATCLK1 input is required only if BCLK need be derived from an independent clock source other than CLK2IN. When required ATCLK1 frequency should be between 10 and 20 MHz for a typical PC AT. Notice that by design SYSCLK is always the BCLK divided by two.

The clock switching logic is guaranteed to provide a "clean" transition with no phases shorter than the minimum values or longer than the maximum values. This allows the clock selections be done dynamically.

#### **Processor clock selection**

Referring to figure 1-2, the CLK2 and SCLK signal can be selected from two sources:

This selection is made by programming bit 4 of the configuration register 4 which defaults to CLK2IN upon reset. By design, if SCLK is selected as the source for BCLK, CLK2 must not be sourced from BCLK. In all but some special cases, CLK2IN should match the rated processor speed, and the BCLK can be either subdivisions of CLK2IN or ATCLK1.

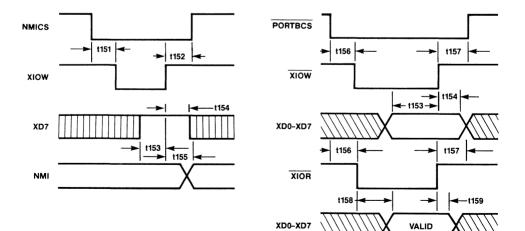

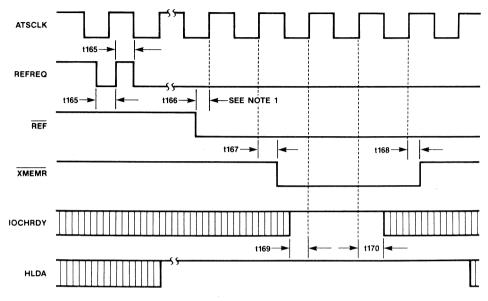

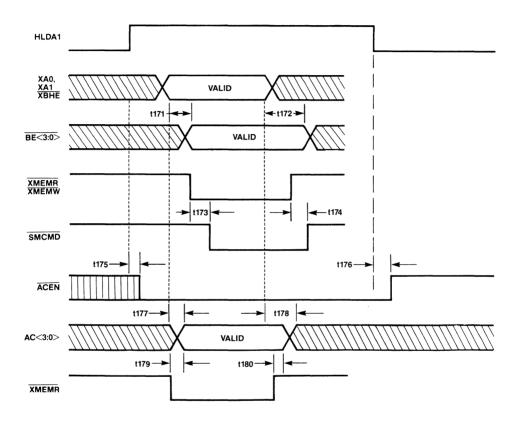

Figure 1-1. 82C301 Functional Block Diagram

## CHIPS.

#### AT bus clock selection

The 82C301 provides flexible software controlled selection of the clock used for the AT bus state machine. The clock can be synchronous (related but not necessarily equal) to the processor CLK2 or unrelated (requiring synchronization between the AT and processor bus state machines). While synchronization logic has been provided in all interface signals between the CPU and the AT state machines, it is highly recommended that the AT bus state machine clock (BCLK) be sourced from SCLK. An internal programmable divider has been provided allowing BCLK frequency of CLK2/2 or CLK2/3. This eliminates the need for an additional oscillator for some system designs. If the divide by 3 option is selected the resulting waveform will have an approximately 50% duty cycle.

The SYSCLK signal generated by the 82C301 is one half of the AT bus state machine clock BCLK. Since this clock is used to drive the AT bus, it is recommended that the the divide

ratio be set for a SYSCLK of about 6 and 8MHz. The table 1-1 shows the combination of clock frequencies obtainable from CLK2IN with this selection scheme.

| CLK2IN | SCLK | Ratio | BCLK | SYSCLK |

|--------|------|-------|------|--------|