## 82C480 8514/A-COMPATIBLE GRAPHICS CONTROLLER

- Fully Compatible with IBM® 8514/A at both register and software ('Adapter Interface' or AI) level

- Runs Windows and Presentation Manager for the 8514/A without special drivers

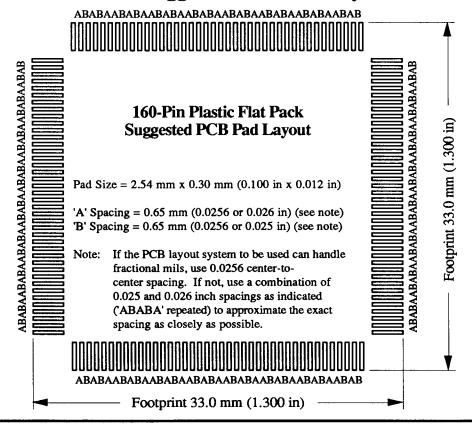

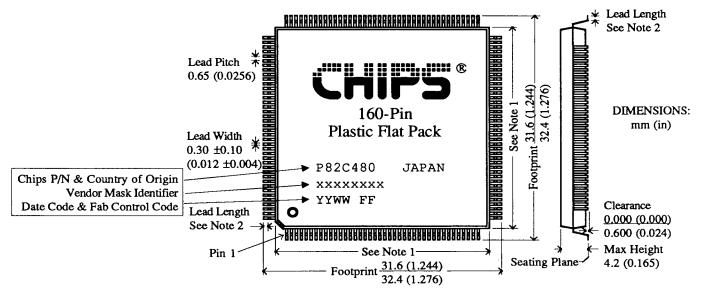

- Single Chip Solution: 160-Pin Plastic Flatpack

- Integrated Micro Channel, Industry Standard Architecture, and EISA Bus Interfaces

- Autoconfigurable for 8-bit or 16-bit System Interface

- Demultiplexed bus interface resulting in lower chip count. Total of 9 chips required for a complete 8514/A implementation including memory:

- 1 82C480 Graphics Controller

- 1 74LS245 Bus Transceiver

- 1 RAMDAC

- 1 LM339 Comparator

- 4 256Kx4 VRÂMs (+4 for 256 colors)

- 1 82B484 Support Chip

- +1 EPROM (optional)

## Supports both 256K and 1M VRAMs

|                    | 16<br>256K | 32<br>256K | 4<br>1M | 8<br>1M |

|--------------------|------------|------------|---------|---------|

| 640x480x16-color   | х          | х          | х       | х       |

| 640x480x256-color  | х          | X          | X       | X       |

| 1024x768x16-color  | X          | X          | X       | X       |

| 1024x768x256-color |            | X          |         | X       |

- Hardware Graphics Functions:

- Bit Blt Polygon Fill - Line Draw - Pattern Fill

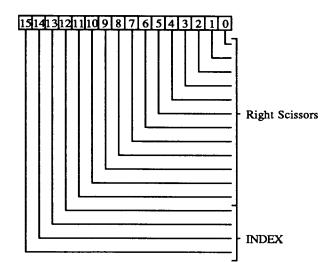

- Color Mixing Scissoring

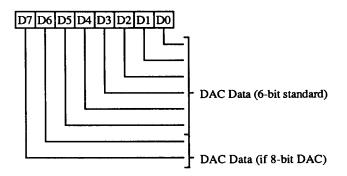

- External palette DAC support for up to 16 million colors (Autoconfigurable for 6-bit or 8-bit RAMDACs)

- Resolutions supported up to 2540x2048 (either interlaced or non-interlaced) with video rates up to 300 MHz

- Software transparent 1024x768 non-interlaced monitor support

- Low-Power CMOS process

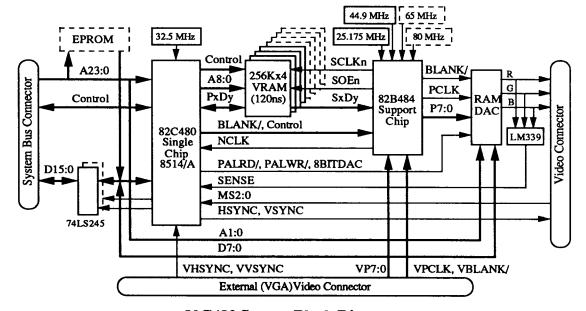

82C480 System Block Diagram

Revision 1.6 Preliminary 82C480

# **Revision History**

| Revision | <u>Date</u> | <u>By</u> | Comment                                                                                                                                           |

|----------|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3      | 5/20/90     | DR        | Document updated to reflect Rev.1 silicon (internal use only) - Register definition added - VESA register and bitfield naming scheme incorporated |

| 1.4      | 6/13/90     | ST        | Change document format to Chips Standard Data Sheet Format                                                                                        |

| 1.5      | 7/11/90     | DR        | Document updated to reflect Rev. 2 silicon                                                                                                        |

## **Table of Contents**

| Section                                 | Page Page | <u>Section</u>                            | Page     |

|-----------------------------------------|-----------|-------------------------------------------|----------|

| Introduction                            | 1         | Pixel Operations                          | 70       |

| Bus Interface                           | 5         | Mixes                                     | 70       |

| ROM Interface                           | 6         | Source Operand Selection                  | 70       |

| VRAM Interface                          | 6         |                                           |          |

|                                         | -         | Foreground and Background                 | 70       |

| Extension Registers                     | 6         | Foreground Select Mode                    | 72       |

| External Color Palette                  | 6         | Color Comparison                          | 72       |

| Performance                             | 6         | Plane Masks                               |          |

| Monitor Support                         | 6         | Across Planes vs. Through Planes          | 74       |

| Line Draw                               | 6         | Scratch Register                          | 75       |

| Text and Alphanumeric Support           | 7         | · ·                                       |          |

| Video Subsystem Total Chip Count        | 7         | Drawing Operations                        | 76       |

| Package                                 | 7         | Diamag operations                         | , 0      |

| 92C490 System Diagrams                  | 7         | Line                                      | 76       |

| 82C480 System Diagrams                  | ,         | SSV Drawing                               | 76       |

| D' .                                    | •         | Copy Rectangle                            | 78       |

| Pinouts                                 | 8         | Fast Rectangle                            | 78       |

|                                         |           | V Doctorale                               | 70       |

| Pin Diagram                             | 8         | X Rectangle                               | 78       |

|                                         | •         | Y Rectangle                               | 79       |

| Pin Descriptions - System Bus Interface | 9         | Polygon Fill                              | 79       |

| Pin Descriptions - Display Memory       | 14        | Text Modes                                | 79       |

| Pin Descriptions - Clocks               | 16        |                                           |          |

| Pin Descriptions - Test, Power & Ground | 18        | Application Schematic Examples            | 81       |

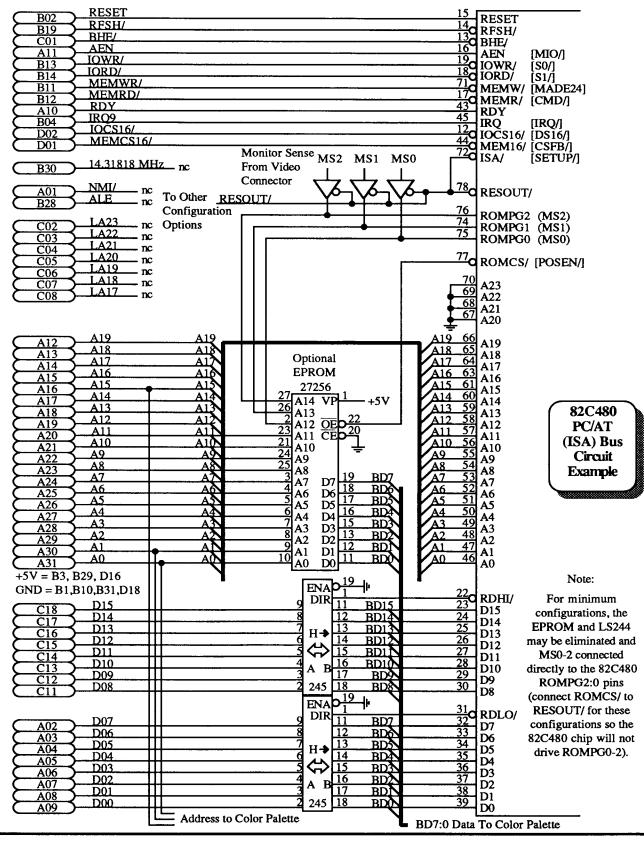

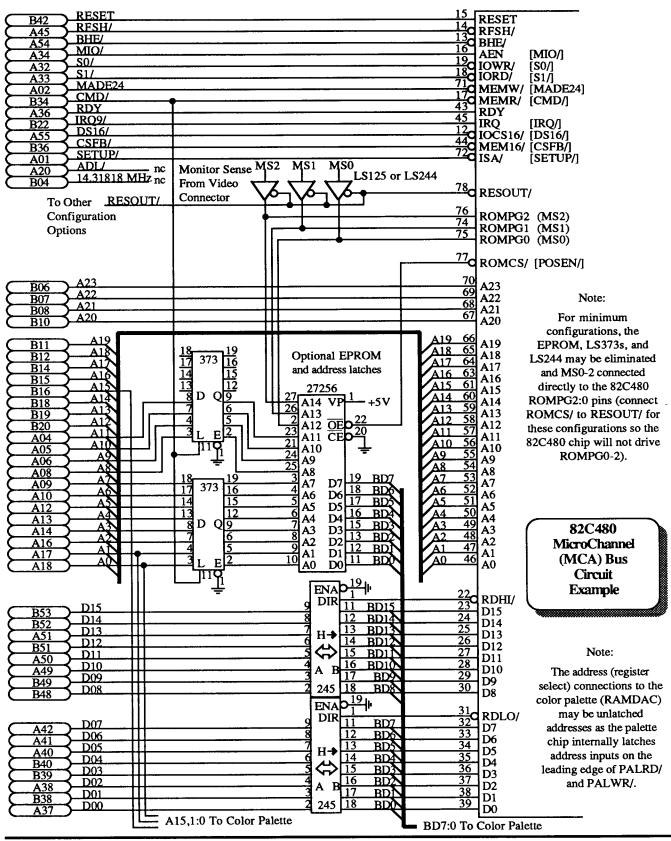

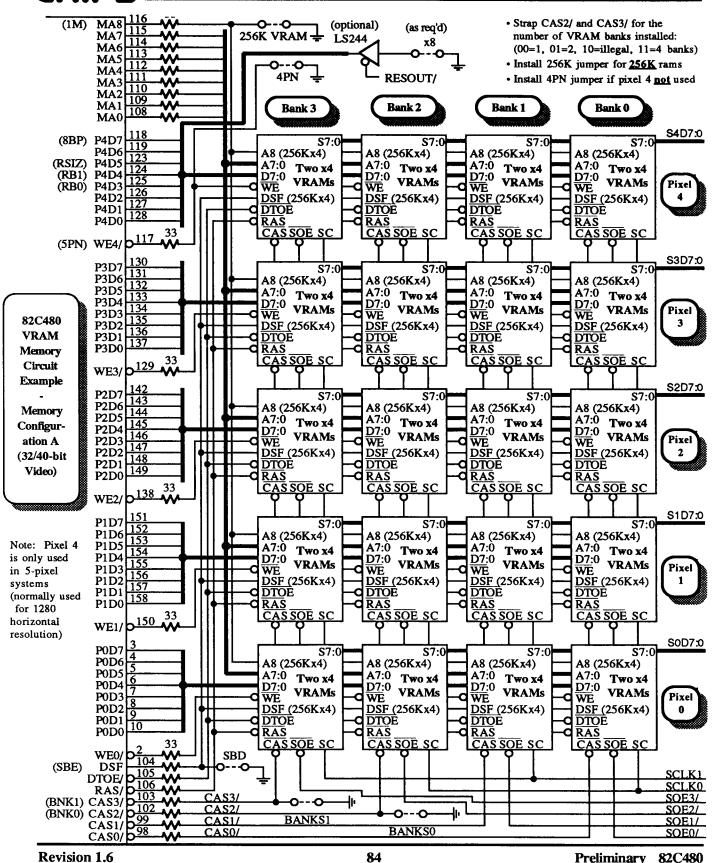

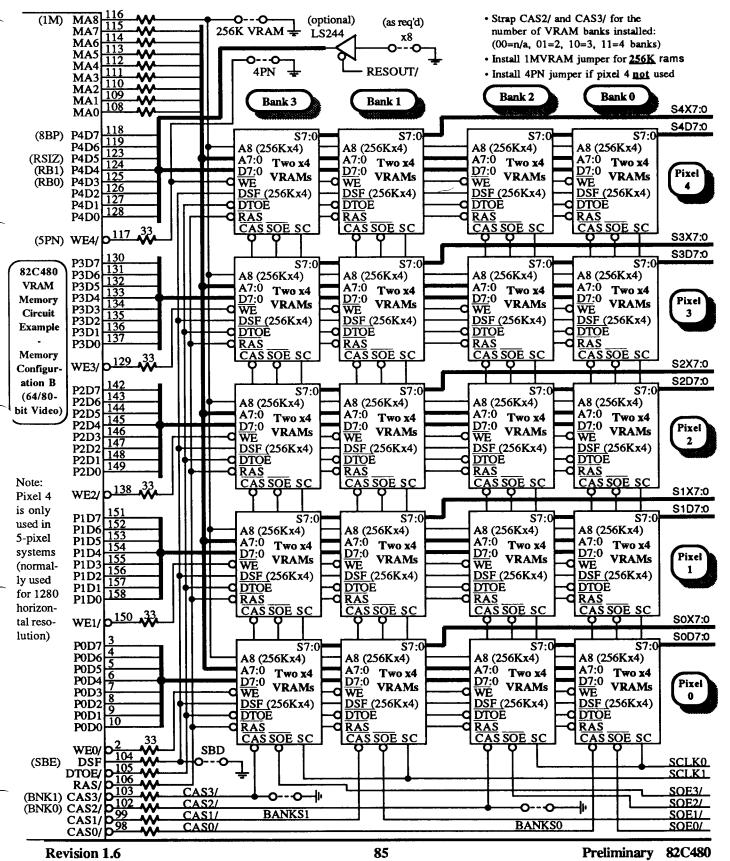

| Register and Port Address Summaries     | 19        | IntroductionISA Bus Circuit Example       | 81<br>82 |

| m . t m. a                              | ••        | Micro Channel Bus Circuit Example         | 83       |

| Register Bit Summary                    | 20        | VRAM Memory Configuration A               | 84       |

|                                         |           | VRAM Memory Configuration B               | 85       |

| Functional Description                  | 57        |                                           |          |

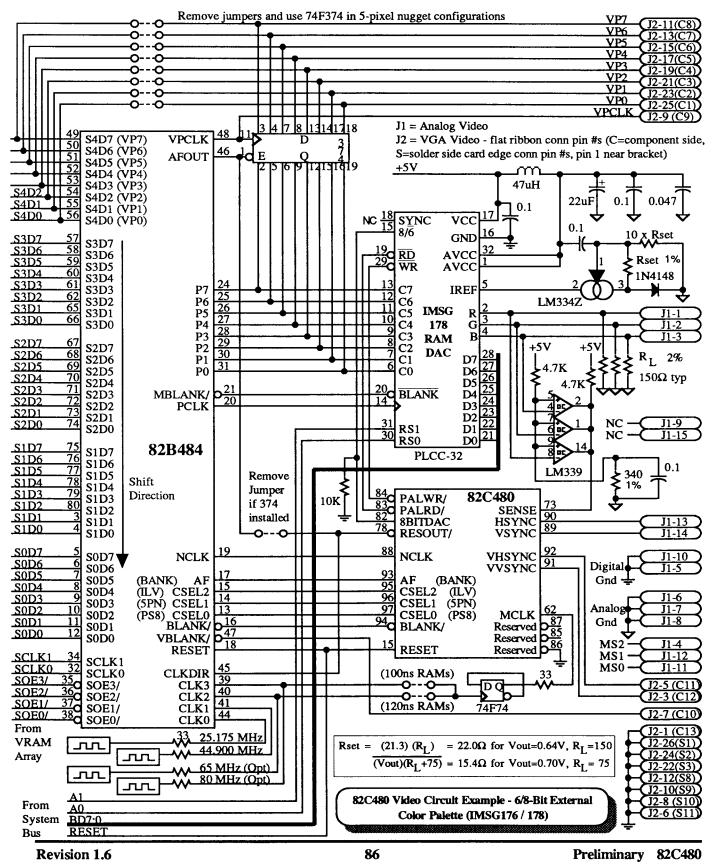

|                                         |           | Video Circuit (IMSG176/178) Color Palette | 86       |

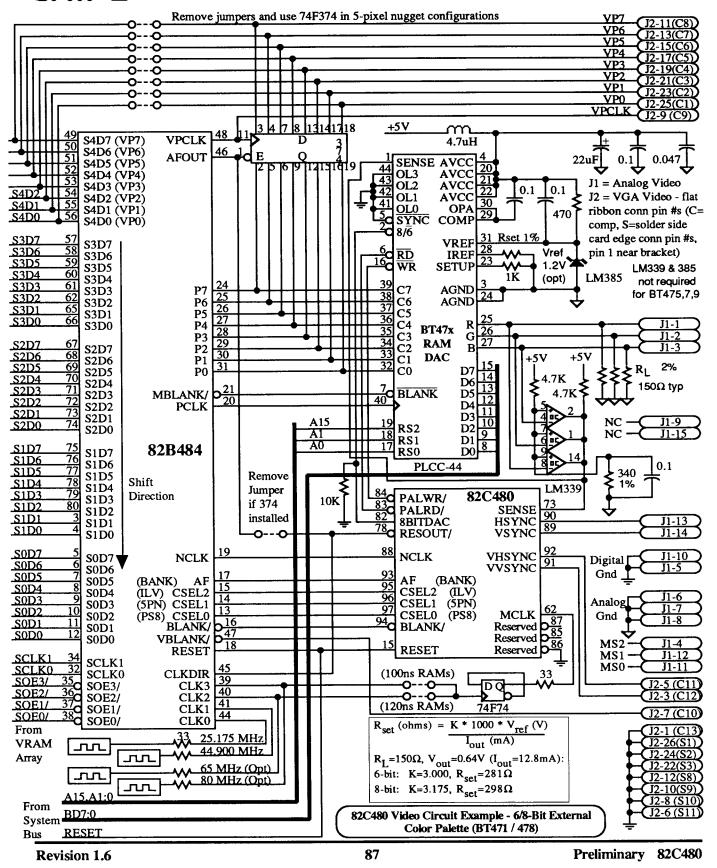

| System Interface                        |           | Video Circuit (BT471/478) Color Palette   | 87       |

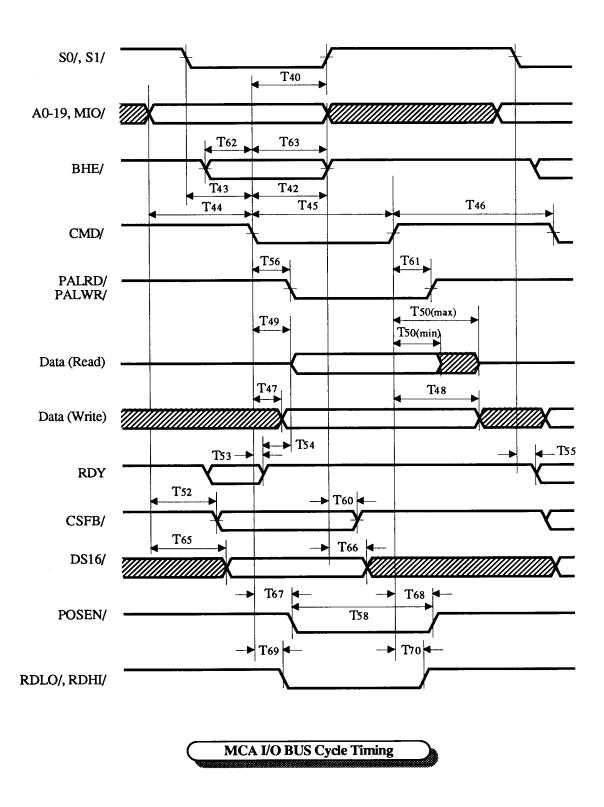

| Micro Channel Interface                 | 57        |                                           |          |

| ISA Interface                           | 57        | Electrical Specifications                 | 89       |

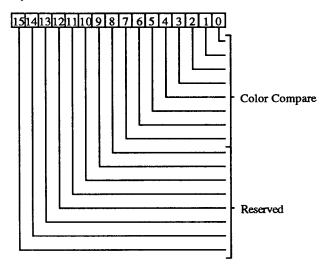

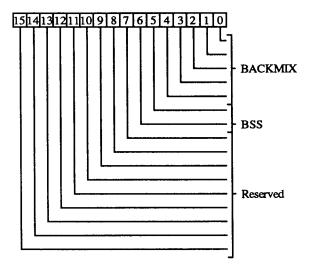

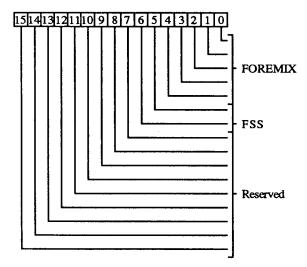

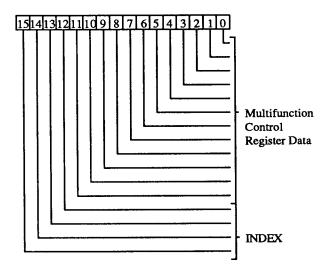

| Queue                                   | 58        |                                           |          |

| Interrupts                              | 58        | Absolute Maximum Conditions               | 89       |

| Memory Interface                        | 60        | Operating Conditions                      | 89       |

| Memory Architecture                     | 60        | DC Characteristics                        | 89       |

| Mamore Configurations                   |           | AC Characteristics                        | 90       |

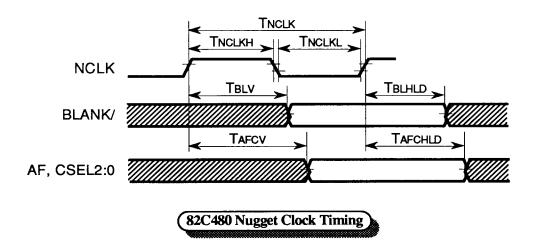

| Memory Configurations                   | 61        | Nugget Clock Timing                       |          |

| RAM Cycle Types                         | 62        | Reset Timing                              |          |

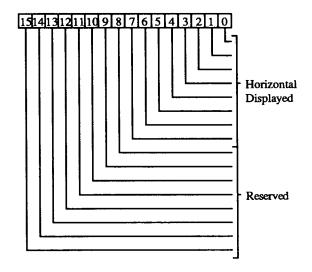

| Video Interface                         | 64        | ICA Due Timing                            | 01       |

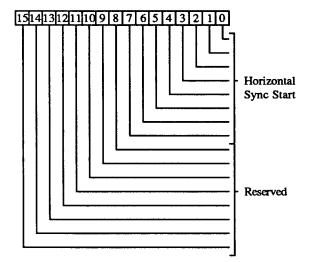

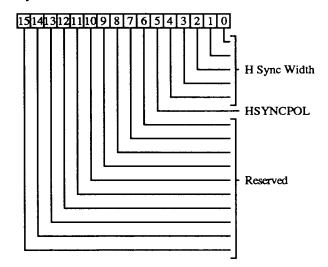

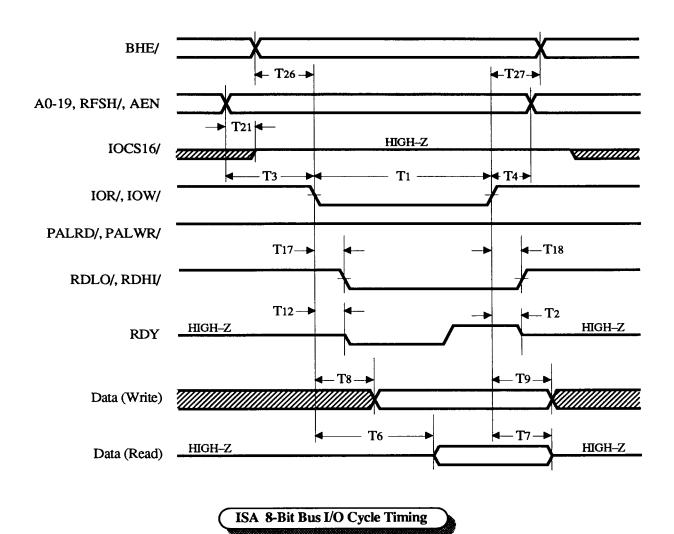

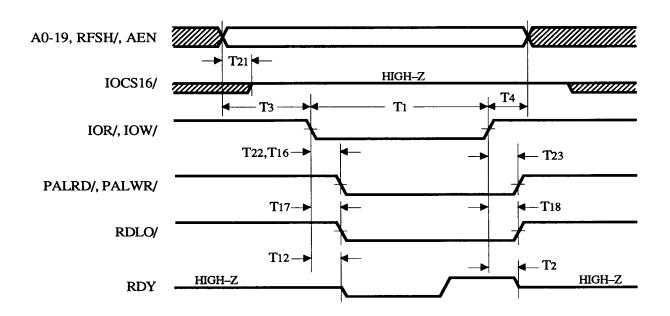

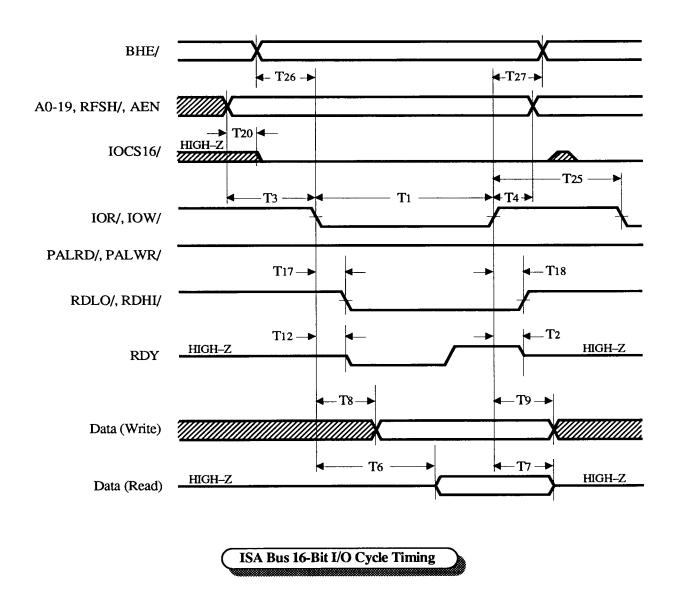

| Horizontal Timing                       | 64        | ISA Bus Timing                            | 91       |

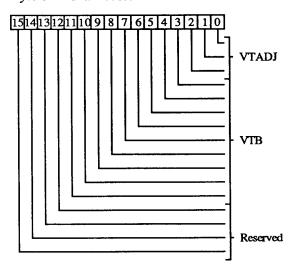

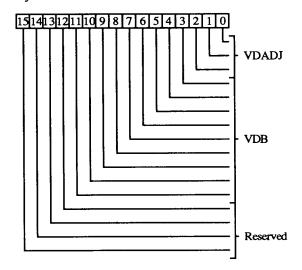

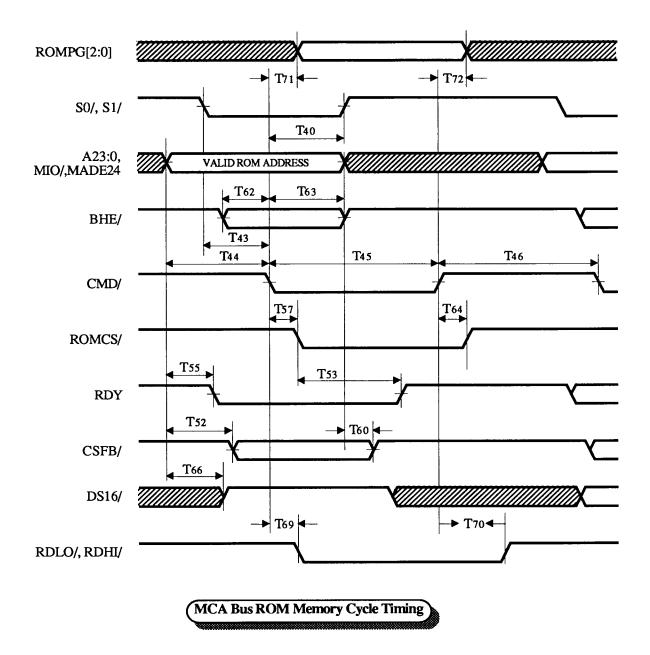

| Vertical Timing                         | 64        | MCA Bus Timing                            |          |

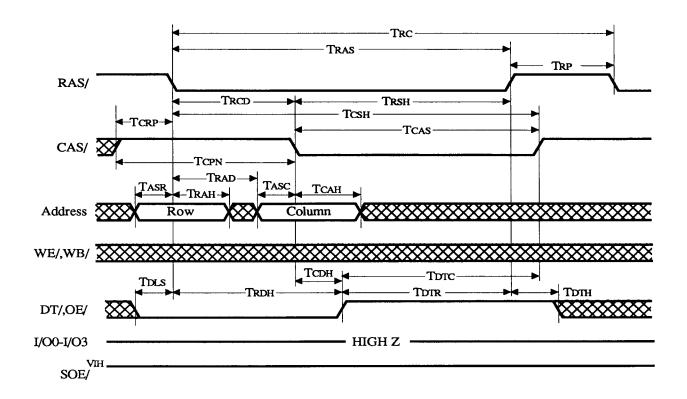

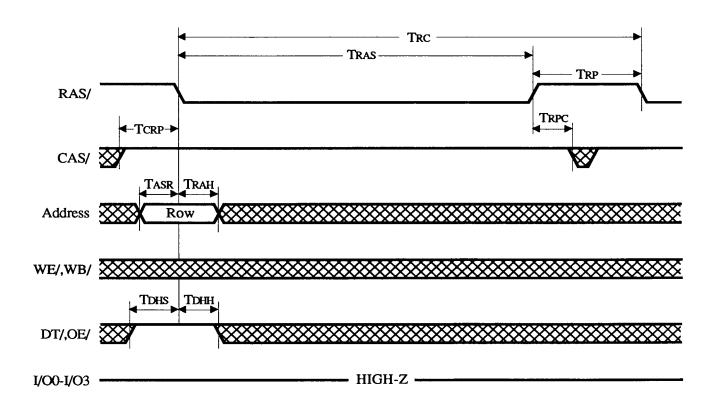

| Refresh Counter                         | 66        | VRAM Timing                               |          |

| Serial Bus                              | 66        | Switching Characteristics                 |          |

| Alternate Video Registers               |           | Timing Requirements                       | 99       |

| Initialization/Configuration            | 67        | Video Timing                              |          |

| Initialization/Configuration            | 68        |                                           |          |

| Reset                                   | 68        | Video Register Parameters                 | 107      |

| POS Operation                           | 68        | TIGO REGISCH LAMMENTS                     | 107      |

| Configuration Options                   | 68        | Machanical Spacifications                 | 100      |

## List of Figures and Tables

| Figure                           | Page                                                                                                                                   | <u>Table</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| System Diagram                   | 1                                                                                                                                      | VRAM 256K Resolution Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                             |

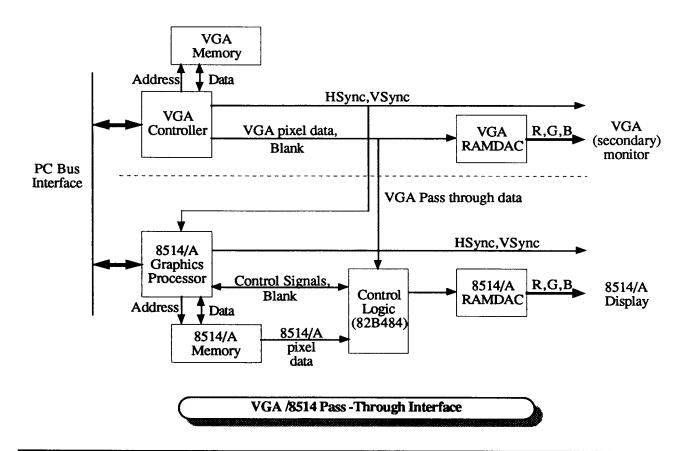

| VGA/8514 Pass-Through Interface  | 5                                                                                                                                      | Relative Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                                             |

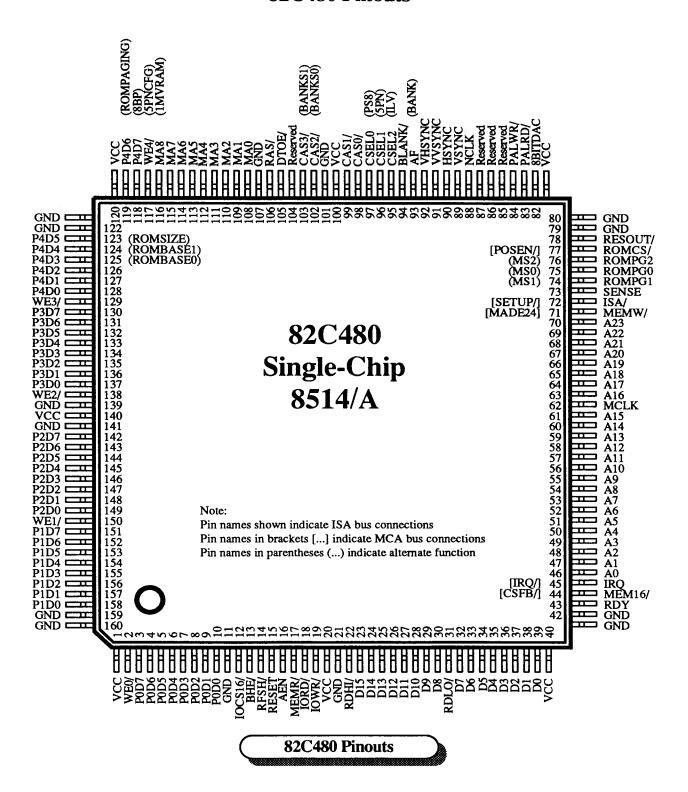

| 82C452 Pinouts                   | 8                                                                                                                                      | Minimum Video Subsystem Chip Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                                             |

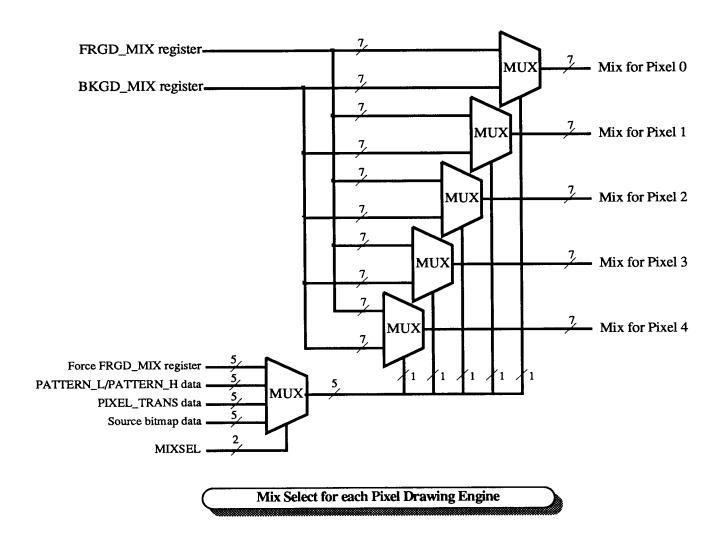

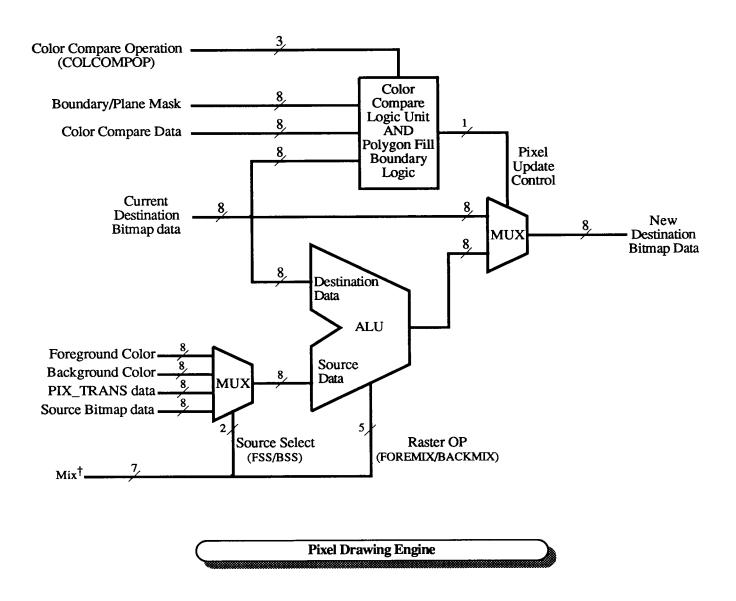

| Mix Select Pixel Drawing Engine  | 71<br>73<br>77<br>82<br>83<br>84<br>85<br>86<br>87<br>90<br>92<br>93<br>94<br>95<br>97<br>98<br>101<br>102<br>103<br>104<br>105<br>106 | Minimum Video Subsystem Chip Count  82C480 Pin Usage  16-bit Byte Steering Bus Cycle Type Monitor ID Type MCLK Frequency vs. VRAM Speed Clock Frequency Select  82C480 Registers Bit Summary Horizontal Sync Polarities Vertical Sync Polarities IBM 8514/A Standard ROM Address Map MCA IBM 8514/A vs. 480 ROM Map VGA ROM Map Mix Background Selection Foreground Mix Selection Foreground Mix Selection  Bus Signal Connections Memory Configurations & Resolutions Sync Polarities vs. Resolution Scan Modulus Alternate Register Selects Alternate Register Enable VRAM Interleave | 7<br>10<br>11<br>13<br>16<br>16<br>19<br>20<br>25<br>27<br>31<br>35<br>48<br>49<br>57<br>61<br>64<br>65<br>67 |

| 82C480 Mechanical Specifications | 109                                                                                                                                    | ROM Base Address Mix Selection Color Compare Operation Fill Boundary Mask  Absolute Maximum Conditions. Normal Operating Conditions. DC Characteristics. AC Characteristics - Nugget Clock Timing. AC Characteristics - Reset Timing. AC Characteristics - ISA Bus Timing. AC Characteristics - MCA Bus Timing. AC Characteristics - VRAM Timing. AC Characteristics - VRAM Timing. AC Characteristics - Video Timing.  Video Register Parameters                                                                                                                                       | 69<br>70<br>74<br>74<br>89<br>89<br>90<br>90<br>91<br>96<br>99                                                |

## Introduction

The 82C480 is a 100% register-level IBM 8514/A compatible controller. The 82C480 provides memory interface logic, video control logic, and interface logic to the ISA (PC/AT<sup>TM</sup>) Bus, EISA Bus, and Micro Channel (MCA).

With 512 KBytes of display memory, the 82C480 supports 16 and 256 displayable colors in 640x480 resolution and 16 with 1024x768 resolution. With 1Mbyte of display memory, it supports 256 displayable colors with 1024x768 resolution. An external RAMDAC supports 256K (6-bit DAC) or 16 million (8-bit DAC) total colors.

The 82C480 supports the following modes selectable via software:

- VGA mode (pass through video from VGA subsystem)

- Advanced Function mode (8514/A 1024x768 or 640x480)

The 82C480 defaults to VGA mode on reset. In the Advanced Function mode, the 82C480 supports 640x480 or 1024x768 resolution as well as providing more complex hardware functions such as BitBlt, line drawing, polygon fill, patterns, raster operations, and scissoring (post-clipping).

Software support for the 82C480 is provided via the Chips and Technologies Adapter Interface (AI) and drivers for major software applications. Any software which supports the IBM 8514/A will also support a compatible 82C480 implementation.

The 82C480 is supplied in a 160-pin PFP package.

#### **Bus Interface**

The 82C480 allows selection of either ISA (PC/AT) or MCA (Micro Channel) Bus Interface by detecting a strapping option during reset. All control signals

Revision 1.6 5 Preliminary 82C480

for both interface types are integrated onto the single 8514/A-compatible chip.

The 82C480 supports both 8-bit and 16-bit CPU interfaces.

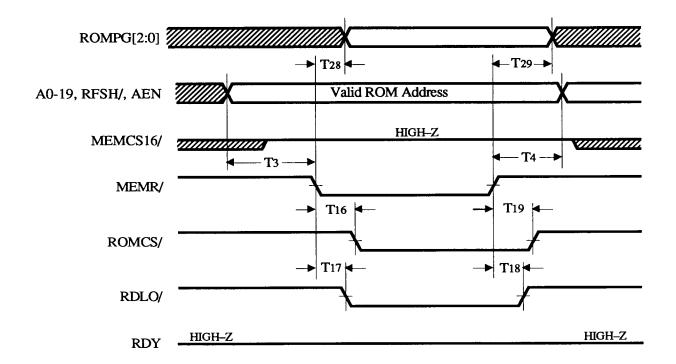

#### **ROM Interface**

The 82C480 supports an optional 8-bit ROM for Power-On-Self-Test (POST) code which may be implemented in AT-bus systems without using additional external components except the ROM chip. The ROM address is decoded and the ROMCS/ pin is asserted to enable ROM data onto the data bus. A 16-bit ROM may be implemented with two ROM chips and one additional external PAL.

Video initialization code and support functions may be included in the POST ROM, incorporated into the system BIOS, loaded from disk at system initialization as a TSR, or incorporated directly into drivers.

### **VRAM Interface**

Like the IBM 8514/A, the 82C480 supports 256K (64Kx4) VRAMs. In addition, the 82C480 also supports 1M (256Kx4) VRAMs, allowing a lower cost, lower chip-count 8514/A implementation. The 82C480 supports a faster memory clock (40 MHz) to maximize use of VRAM bandwidth.

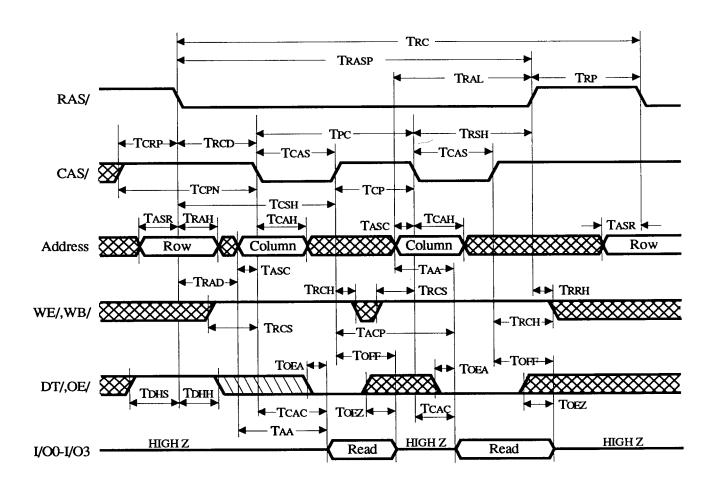

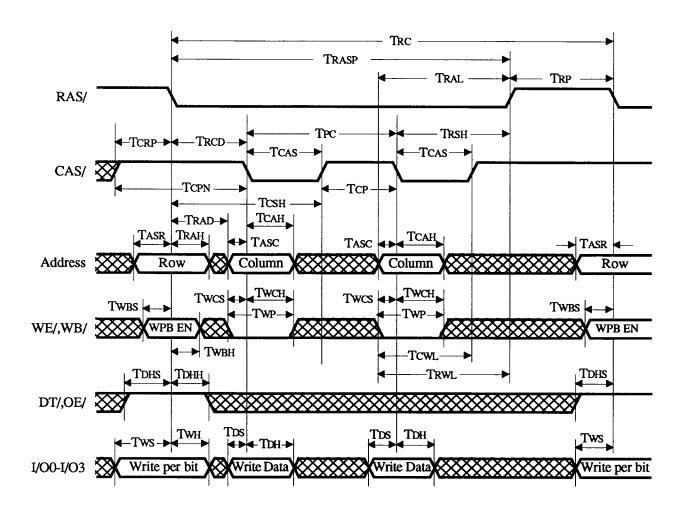

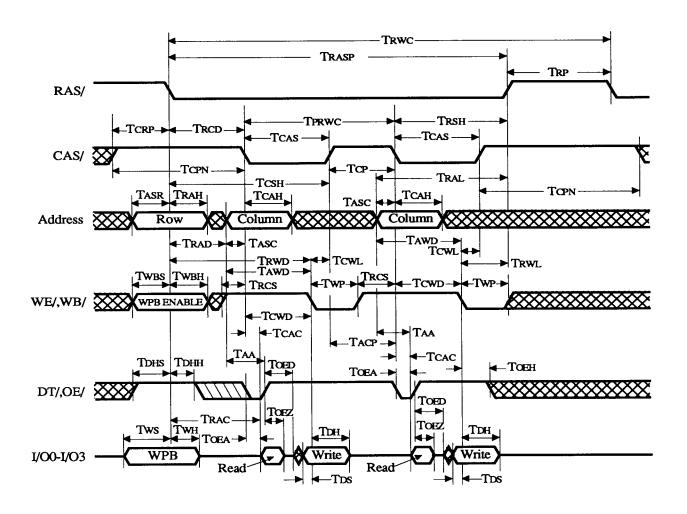

The 82C480 supports five memory cycle types:

- 1. Read (page mode)

- 2. Write (page mode)

- 3. Read-Modify-Write (page mode)

- 4. RAS-only refresh

- 5. Data Transfer Cycle

### **Extensions and Extended Registers**

The 82C480 chip provides enhanced modes of operation which are not available on the IBM 8514/A. These extended features are controlled via bits in extension registers.

The 82C480 has extended the 8514/A architecture to make virtually all of the registers readable. This improves the testability of the chip and makes state saving easy to accomplish.

#### **External Color Palette**

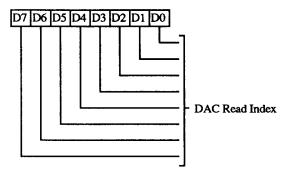

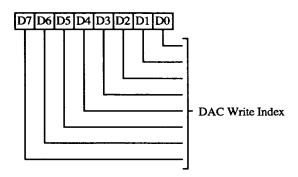

The 82C480 supports the programming of an external color palette DAC (RAMDAC) by decoding the CPU addresses and generating the read and write signals for the external palette.

Normally, each RAMDAC analog output provides 6-bit resolution (64 shades of color on each of the analog R, G, and B outputs). However, a pin is provided by the 82C480 for selecting 8-bit-per-color mode for the DAC (e.g., if using an INMOS IMSG-178 or BT478) which provides 256 shades of color on each RGB output. If this capability is not required, the 8BITDAC pin may instead be used as a general purpose output.

#### Performance

The 82C480 provides up to 2 times the performance of the IBM 8514/A hardware. Projected performance for major graphics operations are listed below (Mp/s = million pixels per second):

| Function            | 82C480    | 8514/A   | Relative<br>Performance |

|---------------------|-----------|----------|-------------------------|

| Clear<br>Horizontal | 28.6 ms   | 33.3 ms  | 1.2x                    |

| Solid Line          | 14.8 Mp/s | 7.3 Mp/s | 2.0x                    |

| Vertical Line       | 3.7 Mp/s  | 2.9 Mp/s |                         |

| BitBlt              | 14.8 Mp/s | 9.6 Mp/s | 1.5x                    |

### Bit-Block Transfer (BITBLT)

The 82C480 uses an internal 32/40 pixel register file for BitBlts (8 words x 32/40 bits). This allows reading a block of pixels in page mode, then writing them using page mode RMW cycles. The 82C480 has a 32/40-bit internal data path, and its faster clock rate results in faster BitBlt performance.

#### Monitor Support

The 82C480 supports the following analog monitors:

- IBM Monochrome Display 8503 or compatible

- IBM High Resolution Monochrome Display 8507 or compatible

- IBM Color Display 8512 or compatible

- IBM Color Display 8513 or compatible

- Interlaced monitors supporting high resolution (IBM 8514, 8515, or compatible)

- Multisync and compatible monitors

- Any interlaced or non-interlaced monitor with a resolution of up to 2560x2048 and supporting video rates of up to 300 MHz

#### Line Draw

Line draw functions (straight lines only) are handled in hardware by the 82C480 chip. Arcs, circles, and

other higher-level shapes must be decomposed to a series of short straight-line segments. The 82C480 uses the Bresenham algorithm for line drawing.

### **Text and Alphanumeric Support**

The 82C480 chip (like the 8514/A) does not support a separate text mode in hardware. Text display is supported via graphics modes, so text may be any size.

The AI supports 3 standard text modes at 1024x768 resolution:

- Mode 0: 85x38 (12x20 character cell)

- Mode 2: 128x54 (8x14 character cell)

- Mode 3: 146x51 (7x15 character cell)

The AI also supports an 80x34 text mode (mode 1) at 640x480 resolution (8x14 character cell).

### Video Subsystem Total Chip Count

Using the 82C480, a complete 8514/A-compatible 8-bit video subsystem can be built with just 9 ICs (10 ICs for a 16-bit system), including display memory, as shown in the table below:

### Qty Chip Type

- 1 82C480 Graphics Controller Chip

- 1 74LS245 Transceiver (2 for 16-bit interface)

- 1 IMSG176-65 RAMDAC

- 1 LM339 Comparator

- 4 256Kx4 VRAM (120 ns) (+4 for 8 planes)

- 1 82B484 Support Chip

- 9 Total

- +1 27256 POST ROM (optional)

Additional components required would be 25.175, 32.5, 44.900 and 65.000 MHz oscillators, 15-pin video connector, LM334 Current reference, 1N4148 diode, and various resistors and capacitors. The indicated configuration (4 256K x 4 VRAM's) supports 640x480 non-interlaced (25.175 MHz.) 16-color and 256-color modes and 1024x768 interlaced (44.900 MHz.) and non-interlaced (65.000 MHz.) 16-color mode.

Adding 256-color support for 1024x768 would require four additional 256Kx4 VRAM chips (for a total of 8 256K x 4 VRAM's).

If a 'Power-On-Self-Test' (POST) ROM is implemented in a Micro Channel bus configuration, two additional 8-bit address latches (74LS373 or equivalent) are also required.

### **Package**

The 82C480 is available in a 160-pin plastic flat pack (PFP).

Complete descriptions of all 82C480 pins are included in this document starting on the next page. The pins are separated into the following logical groups for discussion: Bus Interface, Display memory, Video, Clock, Power, and Ground.

| 82C480 Pin Usage Summary |    |  |  |  |  |

|--------------------------|----|--|--|--|--|

| Bus Interface:           | 60 |  |  |  |  |

| Display Memory:          | 61 |  |  |  |  |

| Video:                   | 9  |  |  |  |  |

| Clock:                   | 6  |  |  |  |  |

| Test:                    | 3  |  |  |  |  |

| Power:                   | 7  |  |  |  |  |

| Ground:                  | 14 |  |  |  |  |

Total: 160

### 82C480 System Diagrams

Included at the end of this document are schematic examples of the following:

- 1. 8/16-bit ISA (PC/AT) Bus Interface 16-bit Micro Channel (MCA) Bus Interface

- Memory Interfacing (40-bit Configuration A) Memory Interfacing (80-bit Configuration B)

- 3. Video/Clock Logic (82B484 IMSG176/8) Video/Clock Logic (82B484 - BT471/8)

## 82C480 Pinouts

Revision 1.6 8 Preliminary 82C480

### **System Bus Interface**

| Pin#     | Pin Name   | Ту       | ype        | Active       | Description                                                                                                                                                      |

|----------|------------|----------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23       | D15        |          | /O         | High         | System Upper Data Bus                                                                                                                                            |

| 24       | D14        | Ţ,       | <b>/O</b>  | High         | All by a secondary is down intermelled so the 92C490 may                                                                                                         |

| 25       | D13        | 1/       | /O<br>/O   | High<br>High | All byte steering is done internally, so the 82C480 may be used without data transceivers in motherboard                                                         |

| 26<br>27 | D12<br>D11 |          | /O<br>/O   | High         | applications; 74LS245 or equivalent transceivers are                                                                                                             |

| 28       | D11<br>D10 |          | /O         | High         | recommended for adapter cards to meet the 24 mA drive                                                                                                            |

| 29<br>29 | D10<br>D9  |          | ίδ         | High         | requirement.                                                                                                                                                     |

| 30       | D8         |          | VÕ         | High         |                                                                                                                                                                  |

| 32       | D7         | I,       | (/O        | High         | System Lower Data Bus                                                                                                                                            |

| 33       | D6         |          | (O)        | High         |                                                                                                                                                                  |

| 34       | D5         |          | <b>/O</b>  | High         |                                                                                                                                                                  |

| 35       | D4         |          | (O         | High         |                                                                                                                                                                  |

| 36       | D3         |          | (O)        | High         |                                                                                                                                                                  |

| 37       | D2         | I,<br>T  | (/O<br>(V) | High<br>High |                                                                                                                                                                  |

| 38<br>39 | D1<br>D0   |          | OVI        | High         |                                                                                                                                                                  |

| 70       | A23        |          | In         | High         | System Address Bus (latched internally for the MCA                                                                                                               |

| 69       | A22        |          | In         | High         | bus on the falling edge of CMD/)                                                                                                                                 |

| 68       | A21        |          | In         | High         |                                                                                                                                                                  |

| 67       | A20        |          | In         | High         | In MCA designs, connect A23:0 to A23:0. In ISA                                                                                                                   |

| 66       | A19        |          | In         | High         | (PC/AT) Bus designs, connect A19:0 to SA19:0 and                                                                                                                 |

| 65       | A18        |          | In         | High         | A23:20 to ground.                                                                                                                                                |

| 64       | A17        |          | In         | High         | In MCA designs, A14:0 must be latched externally by                                                                                                              |

| 63       | A16        |          | In<br>In   | High<br>High | ADL/ or CMD/ for the ROM. In ISA bus designs, the                                                                                                                |

| 61<br>60 | A15<br>A14 |          | In         | High         | address inputs need not be latched.                                                                                                                              |

| 59       | A13        |          | In         | High         | address inputs need not be faterious.                                                                                                                            |

| 58       | A12        |          | In         | High         |                                                                                                                                                                  |

| 57       | A11        |          | In         | High         |                                                                                                                                                                  |

| 56       | A10        | •        | In         | High         |                                                                                                                                                                  |

| 55       | A9         |          | In         | High         |                                                                                                                                                                  |

| 54       | A8         |          | In         | High         |                                                                                                                                                                  |

| 53       | A7         |          | In         | High         |                                                                                                                                                                  |

| 52       | A6         |          | In         | High         |                                                                                                                                                                  |

| 51<br>50 | A5<br>A4   |          | In<br>In   | High<br>High |                                                                                                                                                                  |

| 50<br>49 | A4<br>A3   |          | In         | High         |                                                                                                                                                                  |

| 48       | A3<br>A2   |          | In         | High         |                                                                                                                                                                  |

| 47       | A1         |          | In         | High         |                                                                                                                                                                  |

| 46       | A0         |          | In         | High         |                                                                                                                                                                  |

| 72       | ISA/       | [SETUP/] | In         | Low          | The primary function of this pin is to indicate whether the 82C480 should be configured for the MCA or ISA (PC/AT) bus interface. This pin may be tied to ground |

(PC/AT) bus interface. This pin may be tied to ground or RESOUT/ in ISA Bus configurations. The MCA interface also drives this pin to select the 82C480 during POS (if low, the POS registers at 100-102h are not accessible and all others are if the enable bit in register 102h is set).

System Bus Interface

| Pin#     | Pin Name       |                                       | Туре           | Active     | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|----------------|---------------------------------------|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15       | RESET          |                                       | In             | High       | RESET=1 resets the 82C480 and tristates all output pins except RESOUT/. Also puts internal counters in a known state for chip test.                                                                                                                                                                                                                                                                            |

| 78       | RESOUT/        |                                       | Tri-O          | Low        | RESOUT/ is an inverted and delayed RESET. It is used to enable any external tristate buffers required to drive programming options on the 82C480 pins; these options are latched on the falling edge of RESET. RESOUT/ is guaranteed to stay low long enough to meet the hold time requirement from RESET for any programming option. Some options, such as on the MA8 pin, may be driven by RESOUT/ directly. |

| 13       | ВНЕ/           |                                       | In             | Low        | Byte High Enable. Low indicates that the high order byte at the current word address is being accessed. Along with A0, indicates which bytes are transferred over the bus (all byte steering is done internally):  BHE/ A0 Effect                                                                                                                                                                              |

|          |                |                                       |                |            | 0 0 Both bytes on D15:0 (16-bit slot only) 0 1 High byte on D15:8 (16-bit slot only) 1 0 Low byte on D7:0 (8- or 16-bit slot) 1 1 High byte on D7:0 (8-bit slot only)                                                                                                                                                                                                                                          |

|          |                |                                       |                |            | The 82C480 configures itself to 8- or 16-bit slots. BHE/ is located on the 16-bit bus extension in PC/AT systems, so BHE/ has an internal pullup to hold it inactive in case the card is installed in an 8-bit slot.                                                                                                                                                                                           |

| 22<br>31 | RDHI/<br>RDLO/ | · · · · · · · · · · · · · · · · · · · | Tri-O<br>Tri-O | Low<br>Low | Direction control for high and low external data bus transceivers. These outputs are tristate when RESET is active, so have internal pullups to prevent driving the bus.                                                                                                                                                                                                                                       |

|          | -              |                                       |                |            | 0 = Read data from 82C480<br>1 = Write data into 82C480                                                                                                                                                                                                                                                                                                                                                        |

| 71       | MEMW/          | [MADE24]                              | In             | Both       | In ISA (PC/AT) bus interface, currently unused, but should be connected to SMEMW/ for compatibility with future products. In MCA interface, MADE24=1 indicates only 24 bits of address are being decoded; the 82C480 will not respond to any cycle in MCA mode unless this pin is high. MADE24 may also be used as an active-high chip select to decode 32-bit addresses.                                      |

## System Bus Interface

| Pin# | Pin Name |        | Туре  | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|----------|--------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17   | MEMR/    | [CMD/] | In    | Low    | In MCA, indicates a command cycle (valid data on the bus). Driven by CMD/ from MCA, VGACMD/ from CHIPS/250. In ISA bus, indicates a memory read cycle.                                                                                                                                                                                                                                                                                                                         |

| 19   | IOWR/    | [S0/]  | In    | Low    | In ISA (PC/AT) bus interface, indicates an I/O Write cycle. In MCA bus interfaces, indicates Status bit 0 (S0/).                                                                                                                                                                                                                                                                                                                                                               |

| 18   | IORD/    | [S1/]  | In    | Low    | In ISA (PC/AT) bus interface, indicates an I/O Read cycle. In MCA bus interfaces, indicates Status bit 1 (S1/).                                                                                                                                                                                                                                                                                                                                                                |

| 16   | AEN      | [MIO/] | In    | Both   | In ISA (PC/AT) bus interface, defines valid I/O address: 0 = valid I/O address, 1 = Invalid I/O address (DMA cycle). If single-cycle DMA is used, memory addresses will be on the bus at the same time that IORD/ or IOWR/ is active. The 82C480 will not respond to IORD/ or IOWR/ while AEN=1. In MCA bus interface, indicates memory or I/O cycle: 1 = memory cycle, 0 = I/O cycle.  MIO/ S1/ S0/ Cycle Type                                                                |

|      |          |        |       |        | 0 0 0 -reserved- 0 0 1 I/O Read 0 1 0 I/O Write 0 1 1 -reserved- 1 0 0 -reserved- 1 0 1 Memory Read 1 1 0 Memory Write (not used on 480) 1 1 1 -reserved-                                                                                                                                                                                                                                                                                                                      |

| 14   | RFSH/    |        | In    | Low    | Active low signal indicating Refresh cycle. When this pin is low, the chip is not accessible. This pin and MADE24 are effectively active-high chip selects.                                                                                                                                                                                                                                                                                                                    |

| 43   | RDY      |        | Tri-O | High   | Ready. Driven low to indicate that the current cycle should be extended with wait states. Driven high at the end of cycle to indicate 'ready', then tristated. This signal is normally tristated and is only driven low if the 82C480 cannot respond immediately to I/O requests (or when the ROM is addressed in MCA) to insert the necessary wait states. Another way to look at this pin is as an active-low wait-state request line, instead of an active-high ready line. |

## **System Bus Interface**

| Pin# | Pin Name |          | Туре  | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------|----------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44   | MEM16/   | [CSFB/]  | Tri-O | Low    | In ISA (PC/AT) bus configurations, this pin is currently unused. It is reserved to indicate 16-bit memory cycle capability. For compatibility with future products, this pin should be connected to MEMCS16/ in ISA bus configurations. In MCA bus configurations, this pin is called 'Card Select Feedback'; it indicates any valid access to the 82C480. It is an unlatched decode of A23:0, MIO/, and MADE24.                                                                   |

| 12   | IOCS16/  | [DS16/]  | Tri-O | Low    | In ISA (PC/AT) bus interface, indicates 16-bit I/O cycle. In MCA Interface, indicates 16-bit Memory or I/O cycle. Asserted by the 82C480 to indicate that the chip is capable of transferring 16 bits over the bus at the requested address. In the MCA bus, DS16/ is active for all 82C480 accesses except those to the RAMDAC, POS, and ROM.                                                                                                                                     |

| 45   | IRQ      | [IRQ/]   | Tri-O | Both   | In the ISA (PC/AT) bus, this pin is tristated when interrupts are not enabled, low when interrupts are enabled but no interrupt is pending, and high when interrupts are enabled and an interrupt is pending. In the MCA bus, this pin functions as an active-low open-collector output. The interrupt request pin is normally connected to IRQ9. IRQ9/ may be shared by multiple controllers on the MCA bus; in the ISA bus, only one controller at a time may have IRQ9 enabled. |

|      |          |          |       |        | This pin has high drive capability (IOL = -16mA). While this is still not enough to meet the MCA bus specification of 24mA, the board designer may still want to connect IRQ/ directly to the bus, eliminating the need for a 74LS125 driver.                                                                                                                                                                                                                                      |

| 77   | ROMCS/   | [POSEN/] | I/O   | Low    | In ISA (PC/AT) bus configurations, this pin indicates access to ROM space. In MCA configurations, this pin indicates access to ROM space or to the POS ID registers (I/O address 100-101h and SETUP/ active). In 82C480-based designs with ROM, the POS registers map into the ROM. In systems without ROM, the same information may be provided from external TTL drivers activated by A0 and POSEN/.                                                                             |

Note: Since ROMCS/ is in input mode during reset, an internal pullup resistor ensures the ROM is held in a quiescent state.

**System Bus Interface**

| Pin#           | Pin Name                                                                                                                                                                                         | Туре       | Active               | Descrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tion                                 |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76<br>74<br>75 | ROMPG2 (MS2)<br>ROMPG1 (MS1)<br>ROMPG0 (MS0)                                                                                                                                                     | I/O<br>I/O | High<br>High<br>High | ROM Page (ROM Address msb) outputs / Monitor II inputs. During reset, these pins are inputs sampled of the falling edge of RESET (these pins have internal 50 pullups) to latch the state of the Monitor ID input (MS2:0) from the video connector, which may then be read from the Subsystem Status register. If a ROM is connected to ROMPG2:0, MS2:0 are normally drived onto these pins with a tri-state buffer enabled by RESOUT/. However, if P4D6 is low at the falling edge of RESET, these pins remain inputs so MS2:0 may be connected to these pins directly. If P4D6 is high at the falling edge of RESET, these pins then become output driven by ROM_PAGE_SEL[2:0]. If ROM paging capability is desired, these pins connect to ROM address inputs A14:12 (32K) or A12:10 (8K). |                                      |                                      | t, these pins are inputs sampled on ESET (these pins have internal 50K he state of the Monitor ID inputs ideo connector, which may then be system Status register. If a ROM is PG2:0, MS2:0 are normally driven ith a tri-state buffer enabled by er, if P4D6 is low at the falling edge has remain inputs so MS2:0 may be bins directly. If P4D6 is high at the ET, these pins then become outputs AGE_SEL[2:0]. If ROM paging these pins connect to ROM address |

|                |                                                                                                                                                                                                  |            |                      | MS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MS1                                  | MS0                                  | Monitor Type                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Note:          | The ROMPG2:0 outputs are force high during SETUP mode, indept dent of the ROM Page register contents.  ROM_PG_SEL [2:0] register bit set to 1 on RESET, so that the page defaults to ROM page 7. | ts are     |                      | 0<br>0<br>0<br>0<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | reserved<br>8507 (Mono) (31.5/35.5 KHz)<br>8514 (Color) (31.5/35.5 KHz)<br>reserved<br>reserved<br>8503 (Mono) (31.5 KHz)<br>8512/13 (Color) (31.5 KHz)<br>reserved                                                                                                                                                                                                                                                                                               |

Note: In MCA systems, address bits A11:0 must be latched for the ROM. Addresses may be latched by 74LS373 or equivalent transparent latches on the falling edge of CMD/ or by 74LS374 or equivalent registers on the rising edge of ADL/. In ISA systems, ROM addresses A11:0 are held valid during the entire bus cycle and need not be latched.

Note: In MCA systems, A1:0 may be connected directly to the RAMDAC. IMSG176 or equivalent RAMDACs latch their register select inputs internally on the leading edge of PALRD/ or PALWR/ and the MCA bus holds addresses valid long enough to meet hold time requirements. If addresses are latched for a ROM however, use the latched address hence minimizing the bus signal fanout.

## Display Memory Interface

| Pin#    | Pin Name     |              | Туре       | Active       | Description                                                                                                 |

|---------|--------------|--------------|------------|--------------|-------------------------------------------------------------------------------------------------------------|

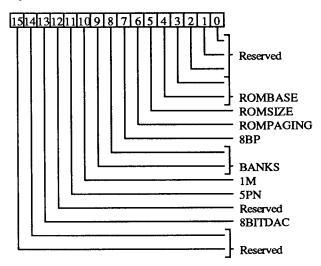

| 118     | P4D7         | (8PLANE)     | I/O        | High         | VRAM Data Bus. The first digit in the signal name in-                                                       |

| 119     | P4D6         | (ROM PAGING) | I/O        | High         | dicates the position of the pixel within the 'nugget'.                                                      |

| 123     | P4D5         | (ROMSIZE)    | ĬΟ         | High         | The second indicates the bit position ('plane') within the                                                  |

| 124     | P4D4         | (ROMBASÉ1)   | Ϊ/O        | High         | pixel                                                                                                       |

| 125     | P4D3         | (ROMBASEO)   | Í/O        | High         | •                                                                                                           |

| 126     | P4D2         | (reserved)   | Ϊ⁄Ο        | High         | For horizontal resolutions of 1024 or less, four-pixel                                                      |

| 127     | P4D1         | (reserved)   | ΪΟ         | High         | nuggets may be used and the minimum number of                                                               |

| 128     | P4D0         | (reserved)   | Ϊ⁄Ο        | High         | 256Kx4 VRAMs required is four (connected to P3:0Dn with P4Dn unconnected). For 1280 horizontal resolu-      |

| 130     | P3D7         |              | I/O        | High         | tion, the minimum number of 256Kx4 VRAMs required                                                           |

| 131     | P3D6         |              | Ĩ/Ŏ        | High         | becomes five (connected to P4:0Dn).                                                                         |

| 132     | P3D5         |              | Ĭ/O        | High         | The P4Dn pins are also used for hardware configuration                                                      |

| 133     | P3D4         |              | Ĭ/Ŏ        | High         | options. On the falling edge of RESET, the state of the                                                     |

| 134     | P3D3         |              | I/O        | High         | P4Dn pins are latched internally. These 8 bits contain                                                      |

| 135     | P3D2         |              | I/O        | High         | internal pull-ups which cause the options to default to                                                     |

| 136     | P3D2<br>P3D1 |              |            | High         | the correct values for 8514/A compatibility. An external                                                    |

| 137     | P3D0         |              | I/O<br>I/O | High<br>High | LS244 buffer (enabled by RESOUT/) may be used to drive non-default ('0') configuration values on any        |

| 1.40    | DADA         |              | 1/0        | TT: -1-      |                                                                                                             |

| 142     | P2D7         |              | ľO         | High         | subset of the P4Dn pins. The inputs of the buffer may                                                       |

| 143     | P2D6         |              | ľO         | High         | be strapped to ground or tied to jumpers for user-confi-                                                    |

| 144     | P2D5         |              | I/O        | High         | gurable options. Alternatively, P4Dn inputs may be                                                          |

| 145     | P2D4         |              | I/O        | High         | connected to 100Ω pulldown resistors in 32-bit pixel                                                        |

| 146     | P2D3         |              | I/O        | High         | data bus configurations. Software may write over any                                                        |

| 147     | P2D2         |              | I/O        | High         | configuration options latched from P4Dn which elimi-                                                        |

| 148     | P2D1         |              | ľO         | High         | nates the need for most strapping options.                                                                  |

| 149     | P2D0         |              | ľO         | High         | P4D7 is saved at reset as a read-only bit in Subsystem Status register (42E8) bit-7 (SUBSYS_STAT[7]). It is |

| 151     | P1D7         |              | I/O        | High         | also accessible (read/write) in Extended Configuration                                                      |

| 152     | P1D6         |              | ľO         | High         | register #2 (5AE8h) bit-7 (EC2[7]). It is interpreted as                                                    |

| 153     | P1D5         |              | Ϊ/O        | High         | the <b>8PLANE</b> ('8 Bit Planes') bit:                                                                     |

| 154     | P1D4         |              | Ĭ/O        | High         |                                                                                                             |

| 155     | P1D3         |              | ΪΟ         | High         | 0 = 4-Plane/16-color configuration                                                                          |

| 156     | P1D2         |              | Ϊ⁄Ŏ        | High         | 1 = 8-Plane/256-color configuration (default)                                                               |

| 157     | P1D1         |              | Ϊ⁄Ο        | High         | P4D6 is saved in EC2[6] as ROM Paging:                                                                      |

| 158     | P1D0         |              | Ĭ/Ŏ        | High         | 0 = ROMPG2:0 are input pins readable at                                                                     |

| 2       | D0D7         |              | T/O        | Uich         | SUBSYS_STAT[6:4] (Monitor Sense pins).                                                                      |

| 3       | POD7         |              | I/O        | High         | 1 = ROMPG2:0 output ROM_PAGE_SEL[2:0]                                                                       |

| 4       | P0D6         |              | I/O        | High         | (Monitor Sense bits are latched from ROMPG2:0                                                               |

| 5       | POD5         |              | I/O        | High         | on the falling edge of RESET only)                                                                          |

| 6       | POD4         |              | I/O        | High         |                                                                                                             |

| 7<br>8  | P0D3<br>P0D2 |              | I/O<br>I/O | High<br>High | P4D5 is saved in EC2[5] as ROM Size:                                                                        |

| 9<br>10 | P0D1<br>P0D0 |              | I/O<br>I/O | High<br>High | P4D5: 0=32K, 1=8K ROM space in system memory                                                                |

| 10      | 1000         |              | ų          | mgn          | P4D4:3 are saved in EC2[4:3] at reset. These are interpreted by hardware as <b>ROMBase</b> :                |

|         |              |              |            |              | P4D4:3 8K MCA 8K ISA 32K                                                                                    |

|         |              |              |            |              | 00 C8000h C6000h D0000h                                                                                     |

|         |              |              |            |              | 01 D8000h D8000h D8000h                                                                                     |

|         |              |              |            |              | 10 C0000h C0000h C0000h                                                                                     |

|         |              |              |            |              | 11 (default) C6000h C8000h C8000h                                                                           |

|         |              |              |            |              |                                                                                                             |

Revision 1.6 Preliminary 82C480

## Display Memory Interface

| Pin#                                                        | Pin Name                                                    |                      | Туре                                                               | Active                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------|-------------------------------------------------------------|----------------------|--------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 116<br>115<br>114<br>113<br>112<br>111<br>110<br>109<br>108 | MA8<br>MA7<br>MA6<br>MA5<br>MA4<br>MA3<br>MA2<br>MA1<br>MA0 | (1MVRAM)             | I/O<br>Tri-O<br>Tri-O<br>Tri-O<br>Tri-O<br>Tri-O<br>Tri-O<br>Tri-O | High<br>High<br>High<br>High<br>High<br>High<br>High<br>High | VRAM Address. On the falling edge of RESET, the state of MA8 is latched into extension register EC2[10]. If 0, 256Kb VRAMs are being used (same as the 8514/A); if 1, 1Mb VRAMs are being used, and the 82C480 reinterprets VRTCFG register bits to maintain register compatibility with the 8514/A. MA8 (only) has an internal 50K pull-up resistor, so the default is 1. To select 256K VRAMs, drive MA8 with RESOUT/.                                                                                                                                                             |

| 106                                                         | RAS/                                                        |                      | Tri-O                                                              | Low                                                          | VRAM Row Address Strobe. An internal pullup keeps the VRAMs in a quiescent state during reset. During normal operation, RAS/ will be observed active (low) except when a RAS precharge cycle is necessary.                                                                                                                                                                                                                                                                                                                                                                           |

| 103<br>102<br>99<br>98                                      | CAS3/<br>CAS2/<br>CAS1/<br>CAS0/                            | (BANKS1)<br>(BANKS0) | I/O<br>I/O<br>Tri-O<br>Tri-O                                       | Low<br>Low<br>Low<br>Low                                     | VRAM Column Address Strobes for memory <u>banks</u> 0–3. CAS3:1/ are unused in single-bank configurations (such as the basic four 1M-VRAM minimum configuration). CAS3:2/ have internal pullups and are sampled at reset and saved in EC2[9:8] as the number of VRAM banks installed: 00=1, 01=2, and 11=4 banks.                                                                                                                                                                                                                                                                    |

| 117<br>129<br>138<br>150<br>2                               | WE4/<br>WE3/<br>WE2/<br>WE1/<br>WE0/                        | (5PN)                | I/O<br>Tri-O<br>Tri-O<br>Tri-O<br>Tri-O                            | Low<br>Low<br>Low<br>Low<br>Low                              | VRAM Write Enables for <u>pixels</u> 4:0 of the nugget, respectively. WE4/ is only used in 5-pixel nugget configurations (it is unused in 4-pixel nugget configurations, such as the basic four 1M-VRAM minimum configuration). WE4/ has an internal pullup and should be connected to RESOUT/ or GND to configure the 82C480 for 4-pixel nuggets. The state of WE4/ at reset (called the 5PN or '5-Pixel Nugget' bit) is saved in Extension Register EC2[11] (read/write) and in the Memory Control register MEM_CNTL[0] as part of the horizontal configuration (HORCFG) bitfield. |

| 105                                                         | DTOE/                                                       |                      | Tri-O                                                              | Low                                                          | Data Transfer / Output Enable for all VRAM chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 104                                                         | Reserved                                                    |                      | n/c                                                                | n/a                                                          | This pin is reserved for future use and should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Clocks

| Pin# | Pin Name | Pin Name Type Active |      | Description                |                                                                                                                        |  |  |  |

|------|----------|----------------------|------|----------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 62   | MCLK     | In                   | High | CRT contro                 | ock. MCLK clocks everything except the ol logic (which uses NCLK). The MCLK is selected to match the speed of the RAMs |  |  |  |

|      |          |                      |      | MCLK                       | VRAM Speed                                                                                                             |  |  |  |

|      |          |                      |      | 25 MHz<br>32 MHz<br>40 MHz | 150 ns<br>120 ns<br>100 ns (Max MCLK frequency)                                                                        |  |  |  |

| 88   | NCLK     | In                   | High | Double Nug                 | gget Clock. Used to generate timing inside                                                                             |  |  |  |

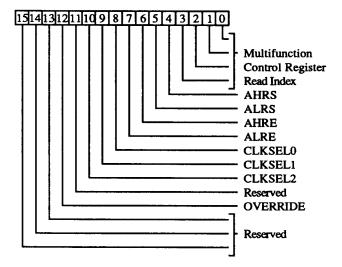

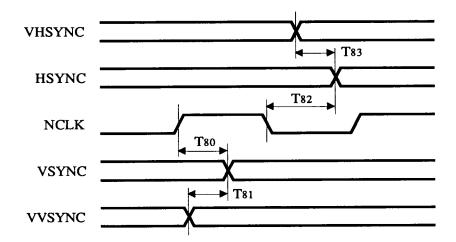

Note: The NCLK frequency is 1/8 or 1/10 of the selected video clock frequency (depending on whether the memory array is configured for 4- or 5-pixel nuggets). CLKSEL2:0 are used to select the video clock from up to eight frequencies (see the CLKSEL selection table below). The selected video frequency is used to clock the external video shift registers and RAMDAC. 82C480 internal logic is clocked on the rising edge of NCLK. HSYNC is delayed by one half NCLK cycle and is clocked on the falling edge of NCLK.

| 95 | CSEL2 | (INTERLEAVE) | Tri-O | High |

|----|-------|--------------|-------|------|

| 96 | CSEL1 | (5PN)        | Tri-O | High |

| 97 | CSEL0 | (PS8)        | Tri-O | High |

Video Clock Select. If BLANK/=0 (blank active), used to select one of up to eight frequencies using external clock selection logic (only the first two frequencies are required for IBM 8514/A compatibility).

| 2 | SE<br>1 | L<br>0 | Frequency<br>Selected | Resolution     |                |

|---|---------|--------|-----------------------|----------------|----------------|

| 0 | 0       | 0      | 25.175 MHz            | 640x480        | non-interlaced |

| 0 | 0       | 1      | 44.900MHz             | 1024x768       | interlaced     |

| 0 | 1       | 0      | 65.000MHz             | 1024x768       | non-interlaced |

| 0 | 1       | 1      | 80.000MHz             | 1280x1024      | interlaced     |

| 1 | 0       | 0      | User-specified        | User-specified |                |

| 1 | 0       | 1      | User-specified        | User-specified |                |

| 1 | 1       | 0      | User-specified        | User-specified |                |

| 1 | 1       | 1      | User-specified        | User-specified |                |

Note: The selected frequency is used to clock the external video shift registers and RAMDAC. It is divided by eight or ten (depending on whether the memory array is configured for 4-pixel or 5-pixel nuggets) for input on NCLK. CLKSEL2:0 are controlled by EC3[10:8] (CLKSEL0 is duplicated in ADVFUNC\_CNTL[2]).

If BLANK/=1 (blank inactive), these pins output INTERLEAVE, 5PN (5-pixel nugget), and PS8 (Pseudo-8-plane mode) bits. 5PN is MEM\_CNTL[0]. PS8 mode is selected by setting VRTCFG=00 (MEM\_CNTL[3:2]) (normal setting is 01).

| 93 | AF | (BANK) | Tri-O | High | If BLANK/=0, indicates Advanced Function (ADVFUNC_CNTL[0]); 1=82C480 drives the video connector, 0=external logic (usually a VGA) drives the video connector. If BLANK/=1, indicates BANK, used by external logic to select which serial output enables (SOE3:0/) to activate for a particular scan line in 4-bank configurations: BANK=0 selects SOE1:0/; BANK=1 selects SOE3:2/. In two-bank configurations, BANK=0 selects SOE0/ and BANK=1 selects SOE1/. |

|----|----|--------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----|----|--------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Revision 1.6 Preliminary 82C480

Test, Power, and Ground

| Pin#           | Pin Name                 | Туре                    | Active              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|--------------------------|-------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

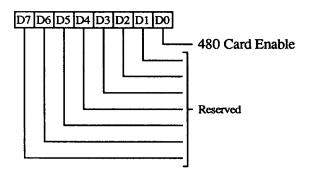

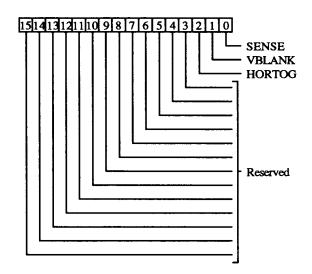

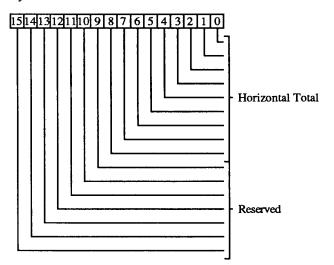

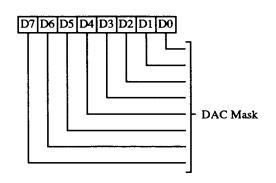

| 83             | PALRD/                   | Tri-O                   | Low                 | Connected to the Read input of the Palette DAC (IMSG176, BT471, or compatible). Asserted when the 82C480 is enabled and an I/O Read occurs from addresses 2EAh-2EDh. Tristate during reset. Internal 50K pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |