# PRELIMINARY

#### **Copyright Notice**

Copyright © 1990, 1991, Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgement**

CHIPS and NEAT are registered trademarks of Chips and Technologies, Inc. CHIPS, CHIPSet, MICROCHIPS, SCAT, NEATsx, LeAPSet, LeAPSetsx, PEAK, CHIPS/230, CHIPS/250, CHIPS/280, CHIPS/450, CHIPSPak, CHIPSPort, CHIPSlink, and SMARTMAP are trademarks of Chips and Technologies, Incorporated.

IBM AT, XT, PS/2, Micro Channel, Personal System/2, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display, and IBM Monochrome Display are trademarks of International Business Machines.

Hercules is a trademark of Hercules Computer Technology.

MS-DOS is a trademark of Microsoft, Incorporated.

MultiSync is a trademark of Nippon Electric Company (NEC).

Brooktree and RAMDAC are trademarks of Brooktree Corporation.

Inmos is a trademark of Inmos Corporation.

TRI-STATE is a registed trademark of National Semiconductor Corporation.

#### Disclaimer

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600 Telex: 272929 CHIPS UR FAX: 408-434-6452

Publication No.: DS111 Stock No.: 010111-001 Revision No.: 0.4

## 82C402 / 402A VGA Clock Synthesizer

- Supports all 82C450 and 82C452A Frequency Requirements

- Supports Feature Clock Pass-Through Logic

- 2 Independent Clock Outputs

- Frequencies Supported up to 65 MHz

- Reduced Board Space Requirements

- 3-State Output Control Disables Outputs for Test Purposes

- Replaces up to Six TTL Oscillators

- Internal Loop Filter Requires no External Components

- Frequency Selection Scheme Compatible with Chips BIOS and Extended Mode Drivers

- Two pin-compatible versions available: 82C402 and 82C402A

- 16-pin DIP or SOIC Package

- Reference Frequency uses Standard 14.31818 MHz Crystal

- Low-Power, High Speed 1.25µ CMOS Technology

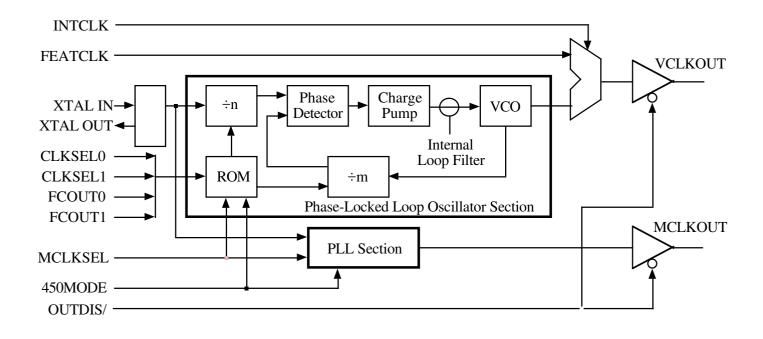

82C402 / 402A Functional Block Diagram

# **Revision History**

| Revision          | Date        | By       | Comment                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.01              | 7/23        | DR       | Draft Copy                                                                                                                                                                                                                                                                                                                                    |

| 0.1               | 7/31        | DR       | Review Copy before formatting                                                                                                                                                                                                                                                                                                                 |

| 0.2               | 8/1         | DR       | Added Table of Contents and List of Figures                                                                                                                                                                                                                                                                                                   |

| 0.3               | 1/91        | DR       | Pin Descriptions - Fixed MCLKSEL 'RAS ACCESS' time specifications                                                                                                                                                                                                                                                                             |

|                   |             |          | VCLKOUT Frequency Select - Changed 0 to 1 in FCOUT1 column                                                                                                                                                                                                                                                                                    |

|                   |             |          | 5th and 6th places and in FCOUTO column 5th and 7th places                                                                                                                                                                                                                                                                                    |

|                   |             |          | DC Characteristics - Changed 2nd and 3rd formulae in Notes column                                                                                                                                                                                                                                                                             |

| 0.4               | 4/29        | DR       | Added 402A frequency table, 40x Clock Chip Layout, and Pin List                                                                                                                                                                                                                                                                               |

| 0.1<br>0.2<br>0.3 | 8/1<br>1/91 | DR<br>DR | Review Copy before formatting<br>Added Table of Contents and List of Figures<br>Pin Descriptions - Fixed MCLKSEL 'RAS ACCESS' time specifica<br>VCLKOUT Frequency Select - Changed 0 to 1 in FCOUT1 column<br>5th and 6th places and in FCOUT0 column 5th and 7th places<br>DC Characteristics - Changed 2nd and 3rd formulae in Notes column |

# **Table of Contents**

| Section                             | Page |

|-------------------------------------|------|

| Introduction                        | 5    |

| Pinouts                             | 6    |

| Pin List                            | 6    |

| Pin Descriptions                    | 7    |

| Functional Description              | 9    |

| Clock Oscillator Selection          | 9    |

| 3-State Output Operation            | 9    |

| Optional External Crystal           | 9    |

| No External Components Required     | 10   |

| Clock Synthesizer Description       | 10   |

| Output Frequency Accuracy           | 11   |

| Minimized Parasitic Problems        | 11   |

| Stability and "Bit-Jitter"          | 1    |

| Temperature and Process Sensitivity | 11   |

| 82C40x Clock Chip Layout            | 12   |

| Section                                  | <u>Page</u> |

|------------------------------------------|-------------|

| Electrical Specifications.               | 15          |

| Absolute Maximum Conditions.             | 15          |

| Normal Operating Conditions.             | 15          |

| DC Characteristics.                      | 15          |

| AC Characteristics.                      | 16          |

| Clock Timing.                            | 16          |

| N82C402 / 402A Mechanical Specifications | 17          |

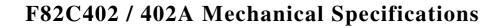

| F82C402 / 402A Mechanical Specifications | 18          |

# List of Figures and Tables

| Figure                                                                                       | Page     |

|----------------------------------------------------------------------------------------------|----------|

| 82C402 Functional Block Diagram                                                              | 1        |

| 82C402 Pinouts                                                                               | 6        |

| 82C402 Crystal Connection<br>82C402 Interface to an 82C450<br>82C402 Interface to an 82C452A | 11       |

| Clock Chip Power Supply Isolation<br>Suggested Clock Chip Layout                             | 12<br>13 |

| 82C402 Clock Timing                                                                          | 16       |

| Plastic Dip Package (PDIP)                                                                   | 17       |

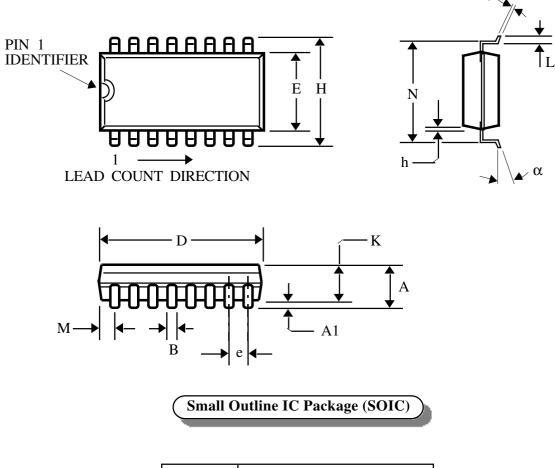

| Small Outline IC Package (SOIC)                                                              | 18       |

| Table                            | Page |

|----------------------------------|------|

| Pin List                         | 6    |

| Pin Descriptions                 | 7    |

| MCLKOUT Frequency Select         | 9    |

| 82C402 VCLKOUT Frequency Select  | 9    |

| 82C402A VCLKOUT Frequency Select | 10   |

| Absolute Maximum Conditions      | 15   |

| Normal Operating Conditions      | 15   |

| DC Characteristics               | 15   |

| AC Characteristics               | 16   |

## Introduction

In applications requiring two or more TTL oscillators, board space, power consumption, and cost may be reduced by using a clock synthesis chip.

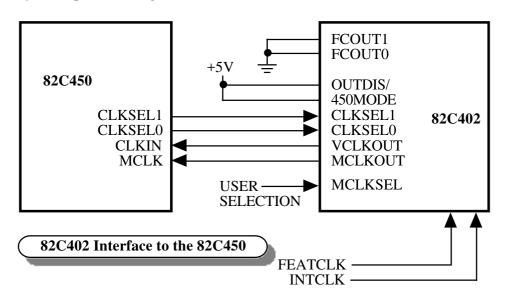

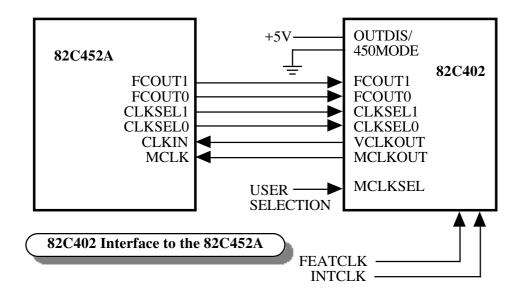

The 82C402 and 82C402A clock synthesizers are designed specifically for interfacing to Chips and Technologies 82C450 1Mb DRAM VGA Controller and 82C452A Super VGA Controller.

There are two versions of the 82C402: the 82C402 and the 82C402A. The only difference between the two is the video clock frequencies produced, therefore all references in this manual to the 82C402 also apply to the 82C402A unless otherwise specified.

The 82C402 features two independent clock outputs impedance matched for direct connection to the

82C450 or 82C452A. This reduces the clock overshoot and undershoot problems which are encountered with fast TTL oscillators and thus eliminates the resistors required to attenuate them. This also reduces high frequency noise within the circuit which facilitates compliance with FCC regulations.

In high-resolution 82C452A applications, the 82C402 replaces up to six TTL oscillators. The 82C402 replaces all five TTL oscillators required for complete 82C450 video mode support. Since only two high frequency clocks are running at one time, noise generated by the board is reduced even further.

The 82C402 allows the multiplexing of an external clock (such as the Feature Connector Clock) thus eliminating the need for 3-state buffers.

Note: The 82C402 and 82C402A are identical in every respect with one exception. One of the video clock frequencies supported in the 82C402 is 32.5 MHz. In the 82C402A, 36 MHz is supported instead of 32.5 MHz (please refer to the frequency tables in the Functional Description).

5

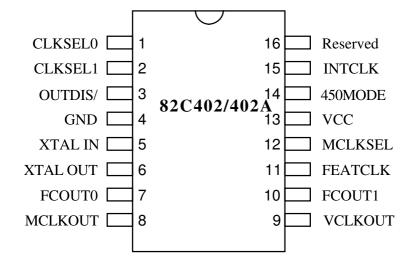

82C402 Pinouts

82C402 Pin List

| Pin Name                                                    | Pin #                      | Pin Name                                          | Pin #                   | Pin Name                                        | Pin #                      |

|-------------------------------------------------------------|----------------------------|---------------------------------------------------|-------------------------|-------------------------------------------------|----------------------------|

| CLKSEL0<br>CLKSEL1<br>OUTDIS/<br>GND<br>XTAL IN<br>XTAL OUT | 1<br>2<br>3<br>4<br>5<br>6 | FCOUT0<br>MCLKOUT<br>VCLKOUT<br>FCOUT1<br>FEATCLK | 7<br>8<br>9<br>10<br>11 | MCLKSEL<br>VCC<br>450MODE<br>INTCLK<br>RESERVED | 12<br>13<br>14<br>15<br>16 |

### **82C402 PIN DESCRIPTIONS**

| Pin #   | Pin Name           | Туре     | Active       | Description                                                                                                                                                                                                                         |  |  |  |

|---------|--------------------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15      | INTCLK             | In       | High         | Selects between the standard frequencies supplied on<br>the VGA adapter and the feature connector clock when<br>clock 2 is selected (VGA Miscellaneous Output<br>Register bits $[3:2] = 10$ ).                                      |  |  |  |

|         |                    |          |              | 0 = Feature clock selected as CLK2<br>1 = 82C402 clock selected as CLK2                                                                                                                                                             |  |  |  |

| 11      | FEATCLK            | In       | High         | Feature connector clock input. This clock is multiplexed with the 82C402 clock frequencies which are selected on CLK2 by the user. The clock source selected is controlled by the INTCLK pin.                                       |  |  |  |

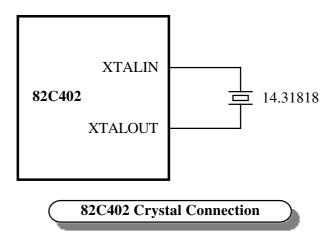

| 5       | XTAL IN            | In       | Both         | Reference frequency input (if using an external oscillator) or 14.31818 MHz crystal input.                                                                                                                                          |  |  |  |

| 6       | XTAL OUT           | Out      | Both         | Optional Oscillator output to a 14.31818 MHz (Series-<br>Resonant) crystal. All passive components required<br>for series resonant operation are implemented<br>internally to the 82C402.                                           |  |  |  |

| 2<br>1  | CLKSEL1<br>CLKSEL0 | In<br>In | Both<br>Both | The CLKSEL inputs are connected directly to the CLKSEL outputs of the 82C450 / 82C452A. They are used in combination with 450MODE, MCLKSEL, and FCOUT1:0 to decode the output frequency requested.                                  |  |  |  |

| 10<br>7 | FCOUT1<br>FCOUT0   | In<br>In | Both<br>Both | The feature connector output signals of the 82C452A are used to select extended mode frequency inputs. These pins should be connected directly to the 82C452A FCOUT pins. For the 82C450, these pins should be connected to ground. |  |  |  |

| 14      | 450MODE            | In       | High         | Determines the VGA controller mode in which the 82C402 is to operate:                                                                                                                                                               |  |  |  |

|         |                    |          |              | 0 = 82C452A<br>1 = 82C450                                                                                                                                                                                                           |  |  |  |

| 12      | MCLKSEL            | In       | Both         | Determines the memory clock speed supplied for the CRT controller:                                                                                                                                                                  |  |  |  |

|         |                    |          |              | VGA RAS MCLKOUT   CONTROLLER ACCESS MCLKSEL (MHz)   82C450 80ns 1 56.644   82C450 100ns 0 50.350   82C452A 100ns 1 40.000   82C452A 120ns 0 32.500                                                                                  |  |  |  |

### **82C402 PIN DESCRIPTIONS**

| Pin # | Pin Name | Туре   | Active | Description                                                                                                                                                                                                                                                                                                   |

|-------|----------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3     | OUTDIS/  | In     | Low    | Output Disable. This disables both of the clock<br>outputs and puts those pins into a high-impedance<br>mode. This is useful for automated board test or for<br>multiplexing additional clocks into the CRT controller.<br>This pin has an internal pull-up and may be left uncon-<br>nected if not required. |

|       |          |        |        | 0 = Clock outputs disabled (3-state)<br>1 = Clock outputs enabled                                                                                                                                                                                                                                             |

| 9     | VCLKOUT  | Out    | Both   | Video Clock Output. This should be connected<br>directly to the CLKIN input on the VGA controller.<br>The output impedance has been matched for a standard<br>layout and the characteristic input impedance of an<br>82C45x VGA controller.                                                                   |

| 8     | MCLKOUT  | Out    | Both   | Memory Clock Output. This should be connected<br>directly to the MCLK input on the VGA controller.<br>The output impedance has been matched for a standard<br>layout and the characteristic input impedance of an<br>82C45x VGA controller.                                                                   |

| 16    | RESERVED | n/c    |        | Reserved pins (do not connect).                                                                                                                                                                                                                                                                               |

| 13    | VCC      | Power  |        | +5V Power Supply.                                                                                                                                                                                                                                                                                             |

| 4     | GND      | Ground |        | Ground Pin.                                                                                                                                                                                                                                                                                                   |

## **Functional Description**

#### **Clock Oscillator Selection**

The output frequency values of VCLKOUT are selected by the 450MODE, CLKSEL1:0, FCOUT1:0 and OUTDIS/ pins as shown at the bottom of the page.

The output frequency values for MCLKOUT are selected by 450MODE and MCLKSEL:

|         | RAS    |         | MCLKOUT |

|---------|--------|---------|---------|

| 450MODE | ACCESS | MCLKSEL | (MHz)   |

| 0       | 120ns  | 0       | 32.500  |

| 0       | 100ns  | 1       | 40.000  |

| 1       | 100ns  | 0       | 50.350  |

At any time during operation, the selection lines can be changed to choose a different frequency. The internal phase-lock loop will immediately begin to seek the newly selected frequency. During the transition period, the clock output may glitch. The intermediate frequency will not exceed the higher of the two transition frequencies.

#### **3-State Output Operation**

The OUTDIS/ signal, when pulled low, will 3-state both of the clock output lines. This supports "wiredor" connections between external clock lines (e.g. the Feature Connector external clock) and allows for procedures such as automated testing, where the clock must be disabled. The OUTDIS/ signal contains an internal pull-up and may be left unconnected if not required.

#### **Optional External Crystal**

Normal operation requires a nominal 14.31818 MHz reference signal which is standard in all PC systems. If the 82C402 is to be used in a motherboard application then it can be used to generate the 14.31818 MHz clock (XTAL OUT) required for the system. If the 14.31818 MHz clock is generated elsewhere on the motherboard, it may be connected directly to the 82C402 (XTAL IN). In motherboard applications, control over the quality of the reference clock is guaranteed by the layout and design. When placing the 82C402 on a daughter card the stability of the

|                 |         |                |        |        |        |         |         | VCLKOUT |

|-----------------|---------|----------------|--------|--------|--------|---------|---------|---------|

| <b>OUTDIS</b> / | 450MODE | <b>ACLKSEL</b> | INTCLK | FCOUT1 | FCOUT0 | CLKSEL1 | CLKSEL0 | (MHz)   |

| 0               | Х       | Х              | Х      | Х      | Х      | Х       | Х       | HIGH-Z  |

| 1               | 0       | Х              | Х      | Х      | Х      | 0       | 0       | 25.175  |

| 1               | 0       | Х              | Х      | Х      | Х      | 0       | 1       | 28.322  |

| 1               | 0       | Х              | 1      | 0      | 0      | 1       | 0       | 44.900  |

| 1               | 0       | Х              | 1      | 0      | 1      | 1       | 0       | 65.000  |

| 1               | 0       | Х              | 1      | 1      | 0      | 1       | 0       | 50.350  |

| 1               | 0       | Х              | 1      | 1      | 1      | 1       | 0       | 40.000  |

| 1               | 0       | Х              | 0      | Х      | Х      | 1       | 0       | FEATCLK |

| 1               | 0       | Х              | 1      | Х      | Х      | 1       | 1       | 44.900  |

| 1               | 1       | 0              | 1      | Х      | Х      | 0       | 0       | 40.000  |

| 1               | 1       | 0              | Х      | Х      | Х      | 0       | 1       | 28.322  |

| 1               | 1       | 0              | 1      | Х      | Х      | 1       | 0       | 32.500  |

| 1               | 1       | 0              | 1      | Х      | Х      | 1       | 1       | 44.900  |

| 1               | 1       | 0              | 0      | Х      | Х      | 0       | 0       | FEATCLK |

| 1               | 1       | 0              | 0      | Х      | Х      | 1       | 0       | FEATCLK |

| 1               | 1       | 0              | 0      | Х      | Х      | 1       | 1       | FEATCLK |

| 1               | 1       | 1              | 1      | Х      | Х      | 0       | 0       | 40.000  |

| 1               | 1       | 1              | Х      | Х      | Х      | 0       | 1       | 50.350  |

| 1               | 1       | 1              | 1      | Х      | Х      | 1       | 0       | 32.500  |

| 1               | 1       | 1              | 1      | Х      | Х      | 1       | 1       | 44.900  |

| 1               | 1       | 1              | 0      | Х      | Х      | 0       | 0       | FEATCLK |

| 1               | 1       | 1              | 0      | Х      | Х      | 1       | 0       | FEATCLK |

| 1               | 1       | 1              | 0      | Х      | Х      | 1       | 1       | FEATCLK |

82C402 VCLKOUT Frequency Select

|         |         |         |        |        |        |         |         | VCLKOUT |

|---------|---------|---------|--------|--------|--------|---------|---------|---------|

| OUTDIS/ | 450MODE | MCLKSEL | INTCLK | FCOUT1 | FCOUT0 | CLKSEL1 | CLKSEL0 | (MHz)   |

| 0       | Х       | Х       | Х      | Х      | Х      | Х       | Х       | HIGH-Z  |

| 1       | 0       | Х       | Х      | Х      | Х      | 0       | 0       | 25.175  |

| 1       | 0       | Х       | Х      | Х      | Х      | 0       | 1       | 28.322  |

| 1       | 0       | Х       | 1      | 0      | 0      | 1       | 0       | 44.900  |

| 1       | 0       | Х       | 1      | 0      | 1      | 1       | 0       | 65.000  |

| 1       | 0       | Х       | 1      | 1      | 0      | 1       | 0       | 50.350  |

| 1       | 0       | Х       | 1      | 1      | 1      | 1       | 0       | 40.000  |

| 1       | 0       | Х       | 0      | Х      | Х      | 1       | 0       | FEATCLK |

| 1       | 0       | Х       | 1      | Х      | Х      | 1       | 1       | 36.000  |

| 1       | 1       | 0       | 1      | Х      | Х      | 0       | 0       | 40.000  |

| 1       | 1       | 0       | Х      | Х      | Х      | 0       | 1       | 28.322  |

| 1       | 1       | 0       | 1      | Х      | Х      | 1       | 0       | 36.000  |

| 1       | 1       | 0       | 1      | Х      | Х      | 1       | 1       | 44.900  |

| 1       | 1       | 0       | 0      | Х      | Х      | 0       | 0       | FEATCLK |

| 1       | 1       | 0       | 0      | Х      | Х      | 1       | 0       | FEATCLK |

| 1       | 1       | 0       | 0      | Х      | Х      | 1       | 1       | FEATCLK |

| 1       | 1       | 1       | 1      | Х      | Х      | 0       | 0       | 40.000  |

| 1       | 1       | 1       | Х      | Х      | Х      | 0       | 1       | 50.350  |

| 1       | 1       | 1       | 1      | Х      | Х      | 1       | 0       | 36.000  |

| 1       | 1       | 1       | 1      | Х      | Х      | 1       | 1       | 44.900  |

| 1       | 1       | 1       | 0      | Х      | Х      | 0       | 0       | FEATCLK |

| 1       | 1       | 1       | 0      | Х      | Х      | 1       | 0       | FEATCLK |

| 1       | 1       | 1       | 0      | Х      | Х      | 1       | 1       | FEATCLK |

|         |         |         |        |        |        |         |         |         |

82C402A VCLKOUT Frequency Select

system bus 14.31818 MHz reference frequency is not assured. In most modern PC designs, this signal is stable enough for use with the 82C402.

For those cases where a stable noise-free system clock cannot be guaranteed, the 82C402 includes a built-in oscillator which can serve as the reference source. If this mode is desired, an external seriesresonant 14.31818 MHz crystal should be connected between the XTAL IN and XTAL OUT pins. No additional resistors or capacitors are required. All components necessary to achieve series resonance are fabricated internal to the 82C402.

### No External Components Required

Under normal conditions no external components are required for proper operation of any of the internal circuitry of the 82C402. The phase-lock loops require no external capacitors or resistors.

#### **Clock Synthesizer Description**

Both of the oscillator blocks are classic phase-locked loops connected as shown in the block diagram on the first page. The external input frequency (XTAL IN) is 14.31818 Mhz and goes into a "divide-by-n" block. The resultant signal becomes the reference frequency for the phase-locked loop circuitry.

The phase-locked loop is essentially a feedback system which attempts to get two signals (the divided reference signal and the divided variable 'synthesized' signal) to arrive in phase. The system attempts to achieve zero phase error between the negative edges arriving at the phase detector. The phase error at the charge pump tells the VCO to either go faster or slower depending on what is required. The greater the change in control voltage, the greater the change in the VCO's output frequency. This up and down movement of the variable frequency will ultimately 'lock-on' to the reference frequency, resulting in an output oscillation as stable as the input reference. An internal 'loop filter' provides stability and damping.

#### **Output Frequency Accuracy**

The accuracy of the output frequency depends upon the target output frequency. The tables within this document contain target frequencies which are different than the actual frequencies produced by the clock synthesizer. The output frequency of the 82C402 clock synthesizer is an integral fraction of the input (reference) frequency:

$$f_{Out} = \frac{2 f_{Ref} m}{n}$$

m,n integer

Only certain output frequencies are possible for a particular reference input. The 82C402 always produces an output frequency within 1.5% of the target. This is more than sufficient to meet standard display requirements.

#### **Minimized Parasitic Problems**

All of the 82C40x family of frequency synthesis components have been optimized to reduce internal noise and crosstalk problems. To minimize adjacency problems, all the synthesis blocks are physically separated into discrete elements with their output oscillator pins isolated as much as possible. Further, all the synthesis VCO's are separated from their digital logic. Finally, separate ground buses for the analog and digital circuitry are used internally. This eliminates the need to provide separate analog and digital VCC and GND to the chip.

The parts use center pins to deliver power and ground to the die instead of the more conventional corner pins. The package leadframes are optimized to have especially 'fat' power and ground leads. This gives the lowest possible inductance from the supply pin on the package to the die within, and results in minimized supply noise problems such as ground-bounce and output crosstalk.

#### Stability and "Bit-Jitter"

The long-term frequency stability of the 82C40x phase-locked loop frequency synthesis components are good due to the nature of the feedback mechanism employed internally in the design. As a result, stability of the devices are affected more by the accuracy of the external reference source than by the internal frequency synthesis circuits.

Short-term stability (also called "bit-jitter") is a manifestation of the frequency synthesis process. The 82C40x frequency synthesis parts have been designed with an emphasis on reduction of "bit-jitter". The primary cause of this phenomenon is the "dance" of the VCO as it strives to maintain lock. Low-gain VCO's and sufficient loop filtering are design elements specifically included to minimize this "bit-jitter". The 82C40x families of frequency synthesis components are all guaranteed to operate at a jitter rate low enough to be visually unnoticeable in the graphics display.

#### **Temperature and Process Sensitivity**

Because of its feedback circuitry, the 82C402 is inherently stable over temperature and manufacturing process variations. An advantage of incorporating the loop filter internal to the chip is that now the loop filter will track the same process variations as does the VCO. This means there are no manufacturing "tweaks" required to filter components as is commonly required for external "de-coupled" filters.

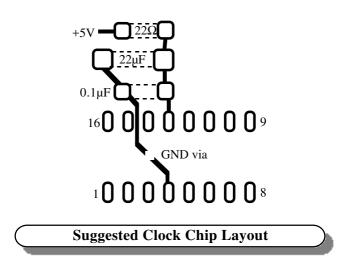

#### 82C40x Clock Chip Layout

Clock synthesis chips are extremely sensitive to voltage supply noise. This is due in part to their use of VCO's to lock onto the desired frequency. The 82C40x family of clock chips all currently contain multiple Phase Lock Loops (PLLs). Each Phase Lock Loop employs a Voltage Controlled Oscillator (VCO). These VCO's have a very high df/dv so small changes in supply voltage can cause large shifts in output frequency. The stability of the VCO's in graphics applications is critical in order to avoid frequency fluctuations. Temporary phase shifts are seen on the display as jitter. To minimize supply line ripple, CHIPS has developed the following layout suggestions for filtering the power supply to the 82C40x clock chips.

When using the 82C402, a full power and ground plane layout should be employed both under and around the IC package.

For two layer boards, bring a separate VCC trace from the bus connector up to the clock chip. This is also desirable but not absolutely necessary for multilayer layouts. Filter this trace at its source with a  $0.1\mu$ F capacitor (C1) and again adjacent to the 22 $\Omega$ resistor (C2) as shown. Multi layer boards tapping an inner power plane may omit the first  $0.1\mu$ F capacitor (C1) but should include the second (C2). All designs must include R1, C3, and C4.

The 22 $\Omega$  resistor acts to filter small fluctuations but also drops the supply voltage to the 82C40x chip by approximately 500mV. This value may be increased to as much as 33 $\Omega$  in very noisy situations with careful attention given to the supply voltage level at the clock chip. If the supply (VCC) drops below 4.25V at the clock chip then the phase lock loop may lose lock. The 82C40x family of clock chips have been tuned to operate with a  $22\Omega$  resistor in series with the VCC input.

The isolated supply should be filtered by a bulk tantalum  $22\mu$ F-47 $\mu$ F capacitor and immediately adjacent to the clock chip by another 0.1 $\mu$ F cap. Both capacitors should be placed within 0.15" of the power pin.It is extremely important that the power supply trace to the clock chip pass from the 22 $\Omega$

resistor, connecting the bulk capacitor, then connecting the 0.1µF capacitor before reaching the power pin on the clock chip. There will be high frequency noise on the isolated supply trace between the bulk capacitor and the 0.1µF. It is important that the clock chip power pin not see any of this noise so do not route the trace from the bulk cap to the 0.1µF via the power pin. The 0.1µF cap will filter this high frequency noise which may otherwise cause visible jitter on the display. For through-hole designs, use ceramic disk capacitors rather than axial leaded capacitors. Minimizing inductance between the VCC and GND pins on the clock chip is very important. For two layer designs, a GND plane should be placed under the 82C40x and its immediate bypass components.

The designer should also avoid routing the clock output traces of the 82C402 in close parallel proximity for any great distance. Large routing lengths and large fanouts add capacitance to output drivers. Capacitance affects the rise and fall times of the outputs and the duty cycle. The 82C402 has been optimized to have its clock output pins connected directly to the VGA controller. When designing with this device, the best rule to follow is to locate the 82C402 as close to the 82C45x VGA controller as is possible. Do not route high frequency signals such as DRAM control lines near to the 82C402 or its clock outputs. A suggested layout is shown below for the isolated section of the supply.

## **Electrical Specifications**

#### 82C402 ABSOLUTE MAXIMUM CONDITIONS

| Symbol           | Parameter                               | Min  | Тур | Max                  | Units |

|------------------|-----------------------------------------|------|-----|----------------------|-------|

| P <sub>D</sub>   | Power Dissipation                       | -    | _   | 175                  | mW    |

| V <sub>CC</sub>  | Supply Voltage                          | -0.5 | _   | 7.0                  | V     |

| V <sub>I</sub>   | Input Voltage                           | -0.5 | _   | V <sub>CC</sub> +0.5 | V     |

| T <sub>SOL</sub> | Maximum Soldering Temperature (10 sec.) | _    | _   | 260                  | °C    |

| T <sub>OP</sub>  | Operating Temperature (Ambient)         | -25  | _   | 85                   | ° C   |

| T <sub>STG</sub> | Storage Temperature                     | -40  | _   | 125                  | ° C   |

Note: Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions described under Normal Operating Conditions.

#### 82C402 NORMAL OPERATING CONDITIONS

| Symbol          | Parameter           | Min  | Тур | Max  | Units |

|-----------------|---------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage      | 4.75 | 5   | 5.25 | V     |

| T <sub>A</sub>  | Ambient Temperature | 0    | _   | 70   | ° C   |

#### 82C402 DC CHARACTERISTICS

(Under Normal Operation Conditions Unless Noted Otherwise)

| Symbol           | Parameter                 | Notes                                              | Min  | Max                  | Units |

|------------------|---------------------------|----------------------------------------------------|------|----------------------|-------|

| I <sub>CC1</sub> | Power Supply Current      | @ 0°C                                              | _    | 35                   | mA    |

| I                | Input Low Leakage Current | $V_I = 0.4 v$                                      | _    | -500                 | μA    |

| I                | Input High Current        | V <sub>I</sub> = 4.6 v                             | _    | 2.5                  | μA    |

| I <sub>OZ</sub>  | Output Leakage Current    | High Impedance                                     | _    | 10                   | μA    |

| V <sub>IL</sub>  | Input Low Voltage         |                                                    | -0.5 | 0.8                  | V     |

| V                | Input High Voltage        |                                                    | 2.5  | V <sub>CC</sub> +0.5 | V     |

| V <sub>OL</sub>  | Output Low Voltage        | $I_{OL} = 4.0 \text{ mA}$ (Clock Outputs)          | _    | 0.4                  | V     |

| V <sub>OH</sub>  | Output High Voltage       | $I_{OH} = -1.0 \text{ mA} \text{ (Clock Outputs)}$ | 2.8  | _                    | V     |

| C <sub>ℕ</sub>   | Input Capacitance         |                                                    | _    | 10                   | pF    |

|                  | Bit Jitter                | (10)                                               | _    | ±350                 | ps    |

|                  | Bit Jitter                | Absolute                                           | _    | 500                  | ps    |

Electrical specifications contained herein are preliminary and subject to change without notice.

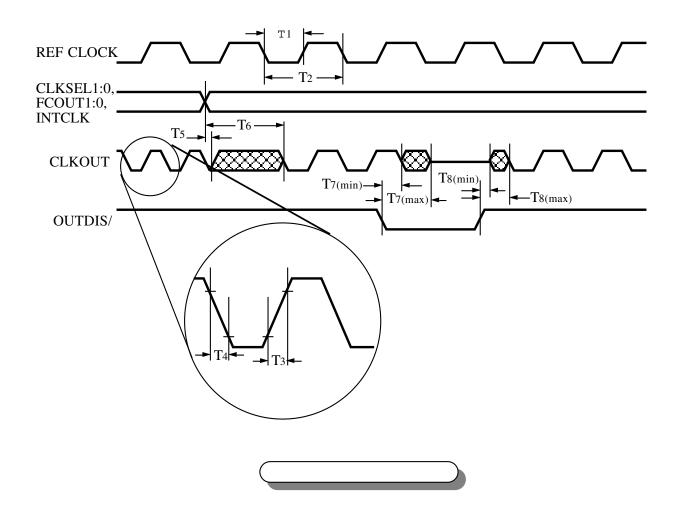

### 82C402 AC CHARACTERISTICS - Clock Timing

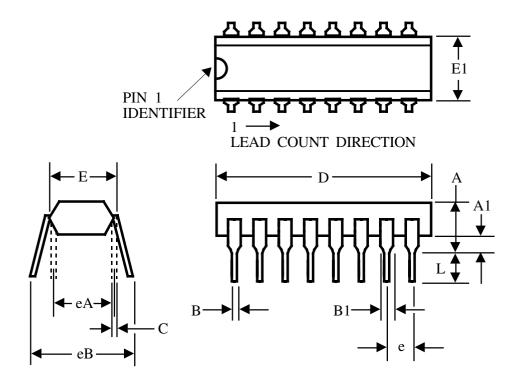

## N82C402 / 402A Mechanical Specifications

Plastic Dip Package (PDIP)

|        | LEAD COUNT = 16 |       |       |  |

|--------|-----------------|-------|-------|--|

| SYMBOL | MIN             | TYP   | MAX   |  |

| А      | 0.195           | -     | 0.200 |  |

| A1     | 0.015           | -     | -     |  |

| В      | 0.015           | -     | 0.020 |  |

| B1     | 0.050           | -     | 0.070 |  |

| С      | 0.008           | -     | 0.012 |  |

| D      | 0.745           | -     | 0.790 |  |

| E      | 0.290           | -     | 0.310 |  |

| E1     | 0.220           | -     | 0.280 |  |

| e      | _               | 0.100 | -     |  |

| eA     | 0.290           | -     | -     |  |

| eB     | —               | _     | 0.310 |  |

| L      | 0.100           | _     | _     |  |

(Dimensions in Inches)

|        | LEAD COUNT = 16 |             |       |

|--------|-----------------|-------------|-------|

| SYMBOL | MIN             | ТҮР         | MAX   |

| A      | 0.099           | -           | 0.104 |

| A1     | 0.004           | -           | 0.009 |

| В      | 0.014           | -           | 0.019 |

| C      | 0.009           | 0.010       | 0.013 |

| D      | 0.405           | -           | 0.410 |

| E      | 0.294           | -           | 0.299 |

| e      | —               | 0.050       | -     |

| Н      | 0.402           | -           | 0.419 |

| h      | —               | 0.025 x 45° | -     |

| L      | 0.030           | _           | 0.040 |

| α      | 0 °             | _           | 8 °   |

| K      | 0.088           | _           | 0.098 |

| М      | 0.020           | -           | 0.030 |

| N      | 0.335           | —           | 0.351 |

(Dimensions in Inches)